#### **FEATURES**

48.7

- ☐ 100 ns Instruction Cycle Time

- ☐ 32-Bit ALU/Accumulator

- ☐ Wait States for Communication to Slow Off-Chip Memories/Peripherals

- 16 bit Internal and External Architecture

- ☐ Single 5V Supply

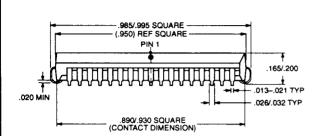

- ☐ Packaging: 68-Pin PLCC

- ☐ CMOS Technology

#### **GENERAL DESCRIPTION**

This data sheet provides the user with the necessary information to integrate this dedicated DSP (Digital Signal Processor) into the Sierra ARIA<sup>TM</sup> sound chip set.

The SC18025 is part of a chip set, used with the Multimedia System Controller (SC18000 or SC18005) and in conjunction with a ROM (SC18050, SC18051 or SC18052). By selecting a Multimedia System Controller and ROM a three chip set will be matched to form one of the three combinations called ST8000, ST8001 or ST8002.

The SC18025 contains a real time multi-tasking operating system kernel, as well as the algorithms for creating ARIA synthesis and performing audio recording and

playback. The operating system kernel consists of a Task Manager and a Task Sequencer. The Task Manager handles the installation and removal of DSP tasks including verification that newly installed tasks are correctly initialized. The Task Sequencer is responsible for sequencing all active DSP tasks using a cooperative multi-tasking scheme. The following features are integrated into the operating system kernel:

- An interrupt handler for DAC/ADC control and synchronization as well as management of the DAC/ ADC double buffering system

- PC IRQ generation for DSP Tasks requiring such interrupts

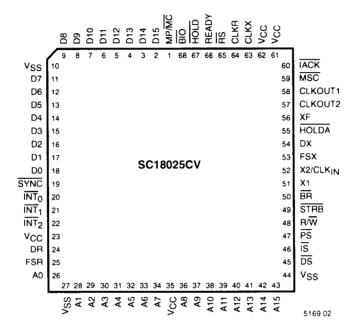

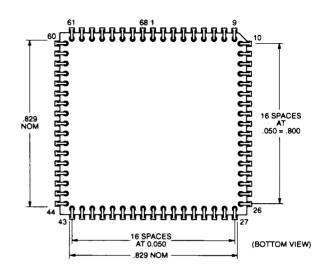

## **68 PIN PLCC PACKAGE**

SC18025CV

Functions to handle command parameter buffering and retrieval

The algorithms contained within the SC18025 allow for generation of ARIA synthesis and controlling recording and playback. ARIA synthesis is based on a sampled waveform technique utilizing waveforms stored in the Sound ROM (SC18051 or SC18052). The following functions are performed when generating ARIA synthesis:

- Execution of up to 32 synthesis operators to generate the individual instrument sounds

- Mixing of the 32 individual operator outputs

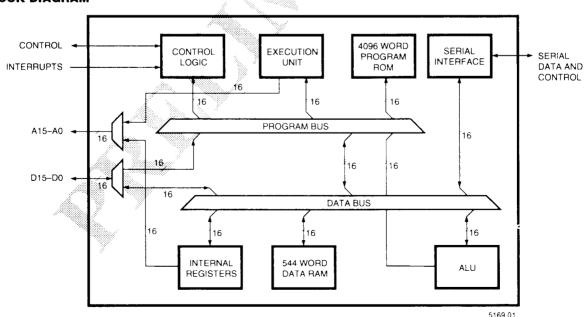

# **BLOCK DIAGRAM**

Figure 1.

Sound Blaster is a trademark of Creative Labs, Inc. ARIA is a trademark of Sierra Semiconductor

# **GENERAL DESCRIPTION (continued)**

- Amplitude Envelope Generation for each operator

- Low Frequency Oscillator (LFO) effects generation

- Individual operator volume and stereo pan settings as well as master volume scaling

The audio recording and playback functions support various formats

- of PCM linear samples as well as 4:1 ADPCM compression/decompression. The SC18025 supports the following modes of operation while in PCM Audio Only mode:

- Up to 4 mono or 2 stereo channels of audio playback at rates up to 44.1 kHz

- Up to 3 mono channels or 1 stereo channel of audio playback and 1 mono or stereo channel of audio recording at rates up to 44.1 kHz

In addition, various DSP commands are used to control the ARIA synthesizer and Audio playback/recording functions.

#### PIN DESCRIPTIONS

| PIN NAME                           | PIN NUMBER       | I/O/Z† | DESCRIPTION                                                                                                                            |

|------------------------------------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| A15-A0                             | 43–36, 34–28, 26 | O/Z    | 16-Bit address bus A15 (MSB) through A0 (LSB).                                                                                         |

| BIO                                | 68               | I      | Branch control input. Polled by BIOZ instruction.                                                                                      |

| BR                                 | 50               | 0      | Bus request signal. Asserted when the SC18025 requires access to an external global data memory space.                                 |

| CLKOUT1                            | 58               | 0      | Master clock output (crystal or CLK <sub>IN</sub> frequency/4).                                                                        |

| CLKOUT2                            | 57               | 0      | A second clock output signal. (-90° phase)                                                                                             |

| CLKR                               | 64               | I      | Clock for receive input for serial port.                                                                                               |

| CLKX                               | 63               | I      | CLock for transmit output for serial port.                                                                                             |

| D15-D0                             | 2–9, 11–18       | I/O/Z  | 16-Bit data bus D15 (MSB) through D0 (LSB). Multiplexed between program, data and I/O spaces.                                          |

| DR                                 | 24               | I      | Serial data receive input.                                                                                                             |

| DS                                 | 45               | O/Z    | Data memory space select signal.                                                                                                       |

| DX                                 | 54               | O/Z    | Serial data transmit output.                                                                                                           |

| FSR                                | 25               | I      | Frame synchronization pulse for receive input.                                                                                         |

| FSX                                | 53               | I/O/Z  | Frame synchronization pulse for transmit. Configurable as either an input or an output.                                                |

| HOLD                               | 67               | I      | Hold input. When asserted, SC18025 goes into an idle mode and places the data, address, and control lines in the high impedance state. |

| HOLDA                              | 55               | 0      | Hold acknowledge signal.                                                                                                               |

| IACK                               | 60               | 0      | Interrupt acknowledge signal.                                                                                                          |

| INT <sub>2</sub> -INT <sub>0</sub> | 22–20            | I      | External user interrupt inputs.                                                                                                        |

| ĪS                                 | 46               | O/Z    | I/O space select signal.                                                                                                               |

| $MP/\overline{MC}$                 | 1                | I      | Microprocessor/microcomputer mode select pin.                                                                                          |

| MSC                                | 59               | 0      | Microstate complete signal.                                                                                                            |

| PS                                 | 47               | O/Z    | Program memory space select signal.                                                                                                    |

| READY                              | 66               | I      | Data ready input. Asserted by external logic when using slower devices to indicate that the current bus transaction is complete.       |

| RS                                 | 65               | I      | Reset input.                                                                                                                           |

| R/W                                | 48               | O/Z    | Read/write signal.                                                                                                                     |

| STRB                               | 49               | O/Z    | Strobe signal.                                                                                                                         |

| SYNC                               | 19               | I      | Synchronous input.                                                                                                                     |

| V <sub>CC</sub>                    | 23, 35, 61, 62   | I      | 5V supply pins.                                                                                                                        |

# PIN DESCRIPTIONS

| PIN NAME        | PIN NUMBER | I/O/Z† | DESCRIPTION                                                  |  |

|-----------------|------------|--------|--------------------------------------------------------------|--|

| V <sub>SS</sub> | 10, 27, 44 | I      | Ground pins.                                                 |  |

| X1              | 51         | 0      | Output from internal oscillator from crystal.                |  |

| X2/CLKIN        | 52         | I      | Input to internal oscillator from crystal or external clock. |  |

| XF              | 56         | 0      | External flag output (latched software-programmable signal). |  |

<sup>†</sup> I/O/Z denotes input/output/high-impedance rate.

# **CONNECTION DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (see Note 1)   | -0.3V to 7V                 |

|------------------------------------------------------|-----------------------------|

| Input voltage range: Pins 24 and 25 All other inputs | -0.3V to 15V<br>-0.3V to 7V |

| Output voltage range                                 | -0.3V to 7V                 |

| Continuous power dissipation                         | 2W                          |

| Operating free-air temperature range                 | 0°C to 70°C                 |

| Storage temperature range                            | -55°C to 150°C              |

NOTE 1: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond those listed in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 2: All voltage values ar with respect to V<sub>SS</sub>.

# RECOMMENDED OPERATING CONDITIONS

| SYMBOL          | PARAMETER                      | TEST CONDITIONS                                                   | MIN          | NOM | MAX                                          | UNIT   |

|-----------------|--------------------------------|-------------------------------------------------------------------|--------------|-----|----------------------------------------------|--------|

| V <sub>CC</sub> | Supply voltage                 |                                                                   | 4.75         | 5   | 5.25                                         | v      |

| $V_{SS}$        | Supply voltage                 |                                                                   |              | 0   |                                              | V      |

| V <sub>IH</sub> | High-level input voltage       | All inputs except CLK <sub>IN</sub> /CLKX/CLKR INT <sub>0-2</sub> | 2.35<br>2.5  |     | V <sub>CC</sub> +0.3<br>V <sub>CC</sub> +0.3 | V<br>V |

| V <sub>IL</sub> | Low-level input voltage        | All inputs except MP/MC MP/MC                                     | -0.3<br>-0.3 |     | 0.8<br>0.8                                   | V<br>V |

| I <sub>OH</sub> | High-level output current      |                                                                   |              |     | 300                                          | μА     |

| I <sub>OL</sub> | Low-level output current       |                                                                   |              |     | 2                                            | mA     |

| T <sub>A</sub>  | Operating free-air temperature |                                                                   | 0            |     | 70                                           | °C     |

# $\begin{tabular}{ll} \textbf{ELECTRICAL CHARACTERISTICS OVER SPECIFIED FREE-AIR TEMPERATURE RANGE} \\ \textbf{(unless otherwise noted)} \end{tabular}$

| SYMBOL         | PARAMETER                       | TEST CONDITIONS                                | MIN | NOM       | MAX        | UNIT |

|----------------|---------------------------------|------------------------------------------------|-----|-----------|------------|------|

| $V_{OH}$       | High-level output voltage       | V <sub>CC</sub> = Min., I <sub>OH</sub> = Max. | 2.4 | 3         |            | v    |

| $V_{OL}$       | Low-level output voltage        | $V_{CC} = Min., I_{OH} = Max.$                 |     | 0.3       | 0.6        | V    |

| IZ             | Three-state current             | V <sub>CC</sub> = Max.                         | -20 |           | 20         | μА   |

| I              | Input current                   | $V_{\rm I} = V_{\rm SS}$ to $V_{\rm CC}$       | -10 |           | 10         | μА   |

| $I_{CC}$       | Supply current Normal Idle/HOLD | $T_A = 0$ °C, $V_{CC} = Max.$ , $fx = Max.$    |     | 110<br>50 | 185<br>100 | mA   |

| C <sub>I</sub> | Input capacitance               |                                                |     | 15        |            | pF   |

| Co             | Output capacitance              |                                                |     | 15        |            | pF   |

**NOTE:** All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

# CLOCK CHARACTERISTICS AND TIMING

The SC18025 can use either its internal oscillator or an external frequency source for a clock.

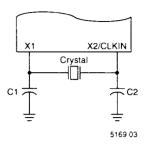

#### **Internal Clock Option**

The internal oscillator is enabled by connecting a crystal across X1 and X2/CLK<sub>IN</sub> (see Figure 2). The

frequency of CLKOUT1 is one-fourth the crystal fundamental frequency. The crystal should be either fundamental or overtone mode, and parallel resonant, with an effective series resistence of 30 ohms, a power dissipation of 1 mW, and be specified at a load capacitance of 20 pF. Note that overtone crystals require an additional tuned LC circuit.

Figure 2. Internal Clock Option

| SYMBOL          | PARAMETER             | TEST CONDITIONS                     | MIN | TYP | MAX   | UNIT |

|-----------------|-----------------------|-------------------------------------|-----|-----|-------|------|

| f <sub>x</sub>  | Input clock frequency | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | 6.7 |     | 40.96 | MHz  |

| f <sub>sx</sub> | Serial port frequency |                                     | 01  |     | 5,120 | kHz  |

| C1, C2          |                       |                                     |     | 10  |       | pF   |

NOTE 1: The serial port is tested at a minimum frequency of 1.25 MHz. However, the serial port is fully static and will properly function down to f<sub>sx</sub> = 0 Hz.

Table 1.

#### **External Clock Option**

An external frequency source can be used by injecting the frequency directly into X2/CLK<sub>IN</sub> with X1 left unconnected. The external fre-

quency injected must conform to the specifications in Table 2.

| SYMBOL                | PARAMETER                                                 | MIN  | TYP | MAX  | UNIT |

|-----------------------|-----------------------------------------------------------|------|-----|------|------|

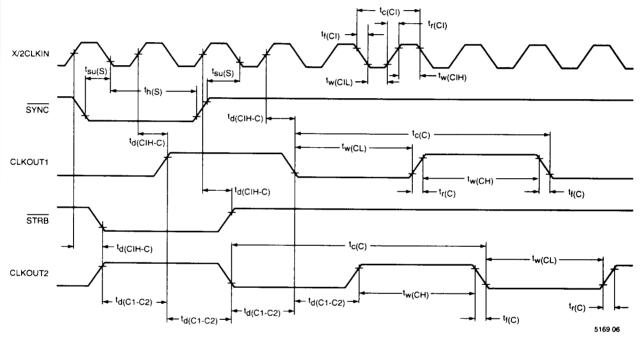

| t <sub>c(C)</sub>     | CLKOUT1/CLKOUT2 cycle time                                | 97.7 |     | 597  | ns   |

| t <sub>d(CIH-C)</sub> | CLK <sub>IN</sub> high to CLKOUT1/CLKOUT2/STRB high/low   | 5    |     | 30   | ns   |

| t <sub>f(C)</sub>     | CLKOUT1/CLKOUT2/STRB fall time                            |      |     | 5    | ns   |

| t <sub>r(C)</sub>     | CLKOUT1/CLKOUT2/STRB rise time                            |      |     | 5    | ns   |

| t <sub>w(CL)</sub>    | CLKOUT1/CLKOUT2 low pulse duration                        | 2Q-8 | 2Q  | 2Q+8 | ns   |

| t <sub>W(CH)</sub>    | CLKOUT1/CLKOUT2 high pulse duration                       | 2Q-8 | 2Q  | 2Q+8 | ns   |

| t <sub>d(C1-C2)</sub> | CLKOUT1 high to CLKOUT2 low, CLKOUT2 high to CLKOUT1 high | Q-5  | Q   | Q+5  | ns   |

Table 2. Switching Characteristics Over Recommended Operating Conditions (Q =  $1/4t_{c(C)}$ )

| SYMBOL              | PARAMETER                                                        | MIN  | TYP | MAX | UNIT |

|---------------------|------------------------------------------------------------------|------|-----|-----|------|

| t <sub>c(CI)</sub>  | CLK <sub>IN</sub> cycle time                                     | 24.4 |     | 150 | ns   |

| t <sub>f(CI)</sub>  | CLK <sub>IN</sub> fall time (see Note 1)                         |      |     | 5   | ns   |

| t <sub>r(CI)</sub>  | CLK <sub>IN</sub> rise time (see Note 1)                         |      |     | 5   | ns   |

| t <sub>w(CIL)</sub> | $CLK_{IN}$ low pulse duration, $t_{c(CI)} = 50$ ns (see Note 2)  | 20   |     |     | ns   |

| t <sub>w(CIH)</sub> | $CLK_{IN}$ high pulse duration, $t_{c(CI)} = 50$ ns (see Note 2) | 20   |     |     | ns   |

| t <sub>su(S)</sub>  | SYNC setup time before CLK <sub>IN</sub> low                     | 5    |     | Q-5 | ns   |

| t <sub>h(S)</sub>   | SYNC hold time from CLK <sub>IN</sub> low                        | 8    |     |     | ns   |

NOTE 1: Value derived from characterization data and not tested.

**NOTE 2:** CLKIN duty cycle[ $t_{r(Cl)} + t_{w(ClH)}$ ]/ $t_{c(Cl)}$  must be within 40–60%.

Table 3. Timing Requirements Over Recommended Operating Conditions (Q =  $1/4t_{c(C)}$ )

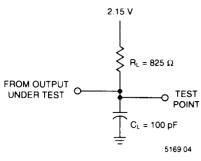

Figure 3. Test Load Circuit

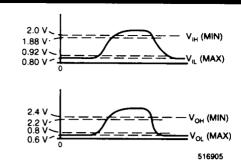

Figure 4. Voltage Reference Levels

Figure 7. Clock Timing

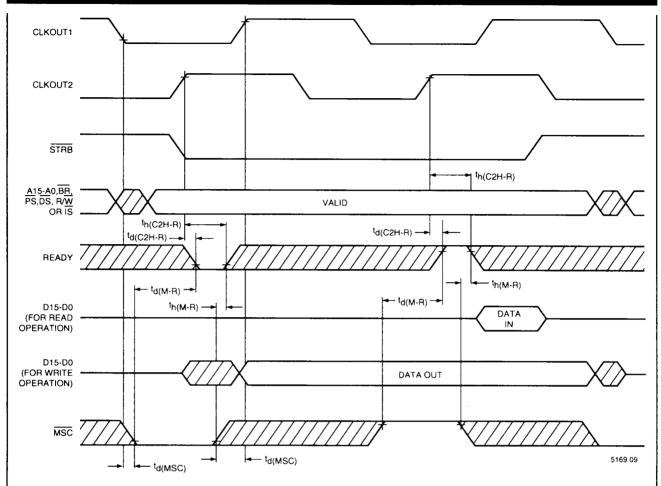

#### **MEMORY AND PERIPHERAL INTERFACE TIMING**

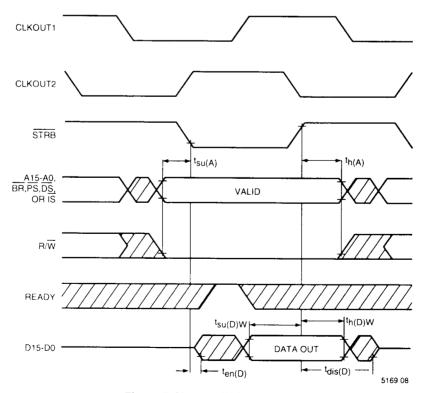

| SYMBOL               | PARAMETER                                                                          | MIN   | TYP | MAX  | UNIT |

|----------------------|------------------------------------------------------------------------------------|-------|-----|------|------|

| t <sub>d(C1-S)</sub> | STRB from CLKOUT1 (if STRB is present)                                             | Q-6   | Q   | Q+6  | ns   |

| t <sub>d(C2-S)</sub> | CLKOUT2 to STRB (if STRB is present)                                               | -6    | 0   | 6    | ns   |

| t <sub>su(A)</sub>   | Address setup time before STRB low (see Note 3)                                    | Q-12  |     |      | ns   |

| t <sub>h(A)</sub>    | Address hold time after STRB high (see Note 3)                                     | Q-8   |     |      | ns   |

| t <sub>w(SL)</sub>   | STRB low pulse duration (no wait states, see Note 4)                               | 2Q-5  |     | 2Q+5 | ns   |

| t <sub>w(SH)</sub>   | STRB high pulse duration (betwen consecutive cycles, see Note 4)                   | 2Q-5  |     | 2Q+5 | ns   |

| t <sub>su(D)W</sub>  | Data write setup time before STRB high (no wait states)                            | 2Q-20 |     |      | ns   |

| t <sub>h(D)W</sub>   | Data write hold time from STRB high                                                | Q-10  | Q   |      | ns   |

| t <sub>en(D)</sub>   | Data bus starts being driven after \$\tilde{STRB}\$ low (write cycle) (see Note 2) | 0     |     |      | ns   |

| t <sub>dis(D)</sub>  | Data bus three-state after STRB high (write cycle) (see Note 2)                    |       | Q   | Q+15 | ns   |

| t <sub>d(MSC)</sub>  | MSC valid from CLKOUT1                                                             | -12   | 0   | 12   | ns   |

**NOTE 1:**  $Q = 1/4t_{c(C)}$

NOTE 2: Value derived from characterization data and not tested.

**NOTE 3:** A15–A0,  $\overline{PS}$ ,  $\overline{DS}$ ,  $\overline{IS}$ ,  $R/\overline{W}$ , and  $\overline{BR}$  timings are all included in timings referenced as "address."

$\textbf{NOTE 4:} \qquad \text{Delays between CLKOUT1/CLKOUT2 edges and } \overline{\textbf{STRB}} \text{ edges track each other, resulting in } t_{w(SL)} \text{ and } t_{w(SH)} \text{ being 2Q with no } t_{w(SL)} \text{ and } t_{w(SL)} \text{ and } t_{w(SL)} \text{ or } t_{w(SL)$

wait states.

Table 4. Switching Characteristics Over Recommended Operating Conditions

| SYMBOL                | PARAMETER                                                             | MIN | NOM | MAX   | UNIT |

|-----------------------|-----------------------------------------------------------------------|-----|-----|-------|------|

| t <sub>a(A)</sub>     | Read data access time from address time (read cycle, see Notes 2 & 3) |     |     | 3Q-35 | ns   |

| t <sub>su(D)R</sub>   | Data read setup time before STRB high                                 | 23  |     |       | ns   |

| t <sub>h(D)R</sub>    | Data read hold time from STRB high                                    | 0   |     |       | ns   |

| t <sub>d(SL-R)</sub>  | READY valid after STRB low (no wait states)                           |     |     | Q-20  | ns   |

| t <sub>d(C2H-R)</sub> | READY valid after CLKOUT2 high                                        |     |     | Q-20  | ns   |

| t <sub>h(SL-R)</sub>  | READY hold time after STRB low (no wait states)                       | Q+3 |     |       | ns   |

| t <sub>h(C2H-R)</sub> | READY hold after CLKOUT2 high                                         | Q+3 |     |       | ns   |

| t <sub>d(M-R)</sub>   | READY valid after MSC valid                                           |     |     | 2Q-25 | ns   |

| t <sub>h(M-R)</sub>   | REDAY hold time after MSC valid                                       | 0   |     |       | ns   |

**NOTE 1:**  $Q = 1/4t_{c(C)}$ .

NOTE 2: A15–A0, PS, DS, IS, R/W, and BR timings are all included in timings referenced as "address."

**NOTE 3:** Read data access time is defined as  $t_{s(A)} = t_{su(A)} + t_{w(SL)} - t_{su(D)R}$ .

Table 5. Timing Requirements Over Recommended Operating Conditions

. igui o oi momory ricuu riiinig

Figure 7. Memory Write Timing

Figure 8. One Wait-State Memory Access Timing

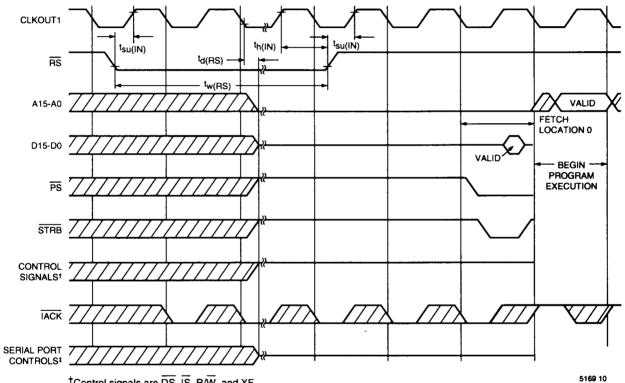

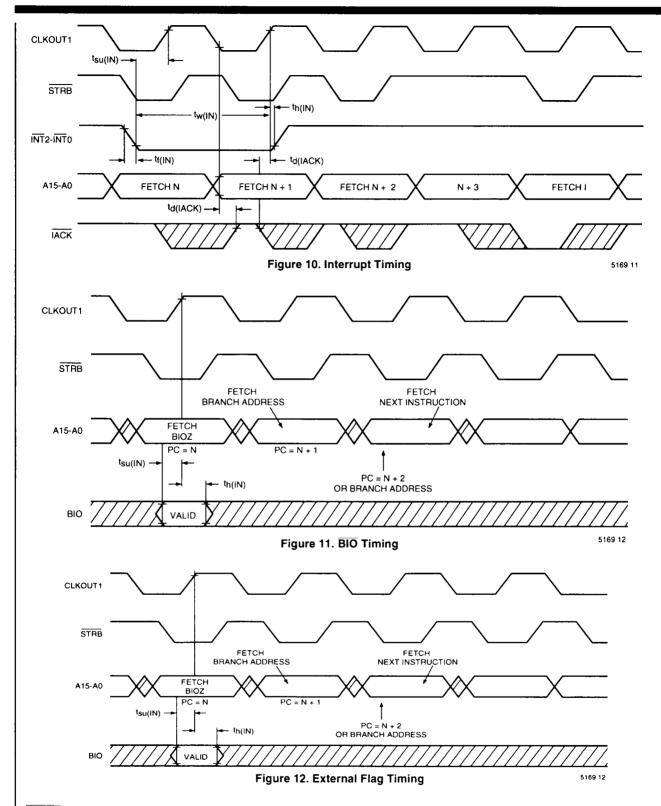

# RS, INT, BIO, AND XF TIMING

| SYMBOL               | PARAMETER                                       | MIN | TYP | MAX | UNIT |

|----------------------|-------------------------------------------------|-----|-----|-----|------|

| t <sub>d(RS)</sub>   | CLKOUT1 low to reset state entered (see note 2) |     |     | 22  | ns   |

| t <sub>d(IACK)</sub> | CLKOUT1 to IACK valid                           | -6  | 0   | 12  | ns   |

| t <sub>d(XF)</sub>   | XF valid before falling edge of STRB            | Q15 |     |     | ns   |

**NOTE 1:**  $Q = 1/4t_{c(C)}$ .

NOTE 2: Value derived from characterization data and not tested.

NOTE 3:  $\overline{\text{RS}}$ ,  $\overline{\text{INT}}$ , and  $\overline{\text{BIO}}$  are asynchronous inputs and can occur at any time during a clock cycle. However, if the specified setup time is met, the exact sequence shown in the timing diagrams will occur.

Table 6. Switching Characteristics Over Recommended Operating Conditions

| SYMBOL              | PARAMETER                                                                                    | MIN                | NOM | MAX | UNIT |

|---------------------|----------------------------------------------------------------------------------------------|--------------------|-----|-----|------|

| t <sub>su(IN)</sub> | $\overline{\text{INT}}/\overline{\text{BIO}}/\overline{\text{RS}}$ setup before CLKOUT1 high | 32                 |     |     | ns   |

| t <sub>h(IN)</sub>  | ĪNT/BIO/RS hold after CLKOUT1 high                                                           | 0                  |     |     | ns   |

| t <sub>f(IN)</sub>  | INT/BIO fall time (see Note 2)                                                               |                    |     | 8   | ns   |

| t <sub>w(IN)</sub>  | INT/BIO low pulse duration                                                                   | t <sub>c(C)</sub>  |     |     | ns   |

| t <sub>w(RS)</sub>  | RS low pulse duration                                                                        | 3t <sub>c(C)</sub> |     |     | ns   |

**NOTE 1:**  $Q = 1/4t_{c(C)}$ .

NOTE 2: Value derived from characterization data and not tested.

NOTE 3:  $\overline{RS}$ ,  $\overline{INT}$ , and  $\overline{BIO}$  are asynchronous inputs and can occur at any time during a clock cycle. However, if the specified setup time is met, the exact sequence shown in the timing diagrams will occur.

**Table 7. Timing Requirements Over Recommended Operating Conditions**

†Control signals are DS, IS, R/W, and XF. ‡Serial port controls are DX and FSX.

Figure 9. Reset Timing

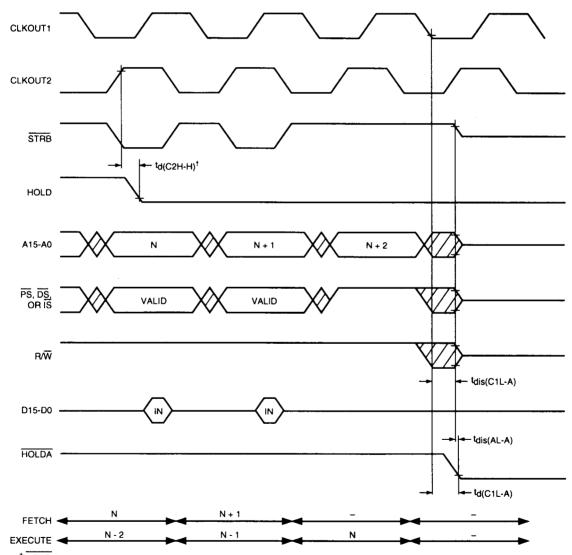

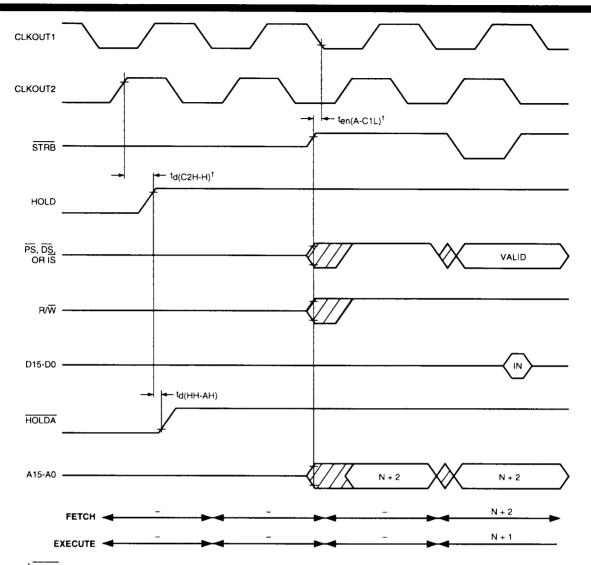

# **HOLD TIMING**

| SYMBOL                | PARAMETER                     | MIN | TYP | MAX  | UNIT |

|-----------------------|-------------------------------|-----|-----|------|------|

| t <sub>d(C2H-H)</sub> | HOLD valid after CLKOUT2 high |     |     | Q-24 | ns   |

**NOTE 1:**  $Q = 1/4t_{c(C)}$ .

**Table 8. Timing Requirements Over Recommended Operating Conditions**

| SYMBOL                 | PARAMETER                                                         | MIN | TYP | MAX | UNIT |

|------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>d(C1L-AL)</sub> | HOLDA low after CLKOUT1 low                                       | 0   |     | 10  | ns   |

| t <sub>dis(AL-A)</sub> | HOLDA low to address three-state (see Note 2)                     |     | 0   |     | ns   |

| tdis(C1L-A)            | Address three-state after CLKOUT1 low (HOLD mode, see Notes 2, 3) |     |     | 20  | ns   |

| t <sub>d(HH-AH)</sub>  | HOLD high to HOLDA high                                           |     |     | 25  | ns   |

| t <sub>en(A-C1L)</sub> | Address driven before CLKOUT1 low (HOLD mode, see Notes 2, 3)     |     |     | 8   | ns   |

**NOTE 1:**  $Q = 1/4t_{c(C)}$ .

NOTE 2: Value derived from characterization data and not tested.

NOTE 3: A15-A0,  $\overline{PS}$ ,  $\overline{DS}$ ,  $\overline{IS}$ ,  $\overline{STRB}$ , and R/W timings are all included in timings referenced as "address."

Table 9. Switching Characteristics Over Recommended Operating Conditions

THOLD is an asynchronous input and can occur at any time during a clock cycle if the specified timing is met the exact sequence shown will occur, otherwise, a delay of one CLKOUT2 cycle will occur.

5169 14

Figure 13. HOLD Timing (Part A)

THOLD is an asynchronous input and can occur at any time during a clock cycle. If the specified timing is met, the exact sequence shown will occur, otherwise, a delay of one CLKOUT2 cycle will occur.

5169 15

Figure 14. HOLD Timing (Part B)

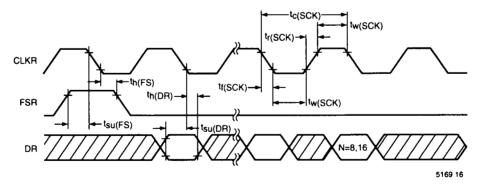

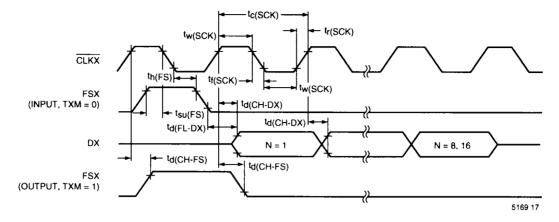

#### **SERIAL PORT TIMING**

| SYMBOL                | PARAMETER                                             | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------------------|-----|-----|-----|------|

| t <sub>d(CH-DX)</sub> | DX valid after CLKX rising edge (see Note 2)          |     |     | 75  | ns   |

| t <sub>d(FL-DX)</sub> | DX valid after FSX falling edge (TXM = 0, see Note 2) |     |     | 40  | ns   |

| t <sub>d(CH-FS)</sub> | FSX valid after CLKX rising edge (TXM = 1)            |     |     | 40  | ns   |

**NOTE 1:**  $Q = 1/4t_{c(C)}$ .

NOTE 2: The last occurence of FSX falling and CLKX rising.

Table 10. Switching Characteristics Over Recommended Operating Conditions

| SYMBOL              | PARAMETER                                                      | MIN | TYP | MAX | UNIT |

|---------------------|----------------------------------------------------------------|-----|-----|-----|------|

| t <sub>c(SCK)</sub> | Serial port clock (CLKX/CLKR) cycle time <sup>3</sup>          | 200 |     |     | ns   |

| t <sub>f(SCK)</sub> | Serial port clock (CLKX/CLKR) fall time (see Note 2)           |     |     | 25  | ns   |

| t <sub>r(SCK)</sub> | Serial port clock (CLKX/CLKR) rise time (see Note 2)           |     |     | 25  | ns   |

| t <sub>w(SCK)</sub> | Serial port clock (CLKX/CLKR) low pulse duration (see Note 4)  | 80  |     |     | ns   |

| t <sub>w(SCK)</sub> | Serial port clock (CLKX/CLKR) high pulse duration (see Note 4) | 80  |     |     | ns   |

| t <sub>su(FS)</sub> | FSX/FSR setup time before CLKX/CLKR falling edge (TXM = 0)     | 18  |     |     | ns   |

| t <sub>h(FS)</sub>  | FSX/FSR setup time after (CLKX/CLKR falling edge (TXM = 0)     | 20  |     |     | ns   |

| t <sub>su(DR)</sub> | DR setup time before CLKR falling edge                         | 10  |     |     | ns   |

| t <sub>h(DR)</sub>  | DR hold time after CLKR falling edge                           | 20  |     |     | ns   |

**NOTE 1:**  $Q = 1/4t_{c(C)}$ .

NOTE 2: Value derived from characterization data and not tested.

NOTE 3: The serial port is tested at a minimum frequency of 1.25 MHz. However, the serial port is fully static and will properly function

down to  $f_{sx} = 0 Hz$ .

**NOTE 4:** The duty cycle of the serial port clock must be within 40–60%.

**Table 11. Timing Requirements Over Recommended Operating Conditions**

Figure 15. Serial Port Receive Timing

Figure 16. Serial Port Receive Timing

## PHYSICAL DIMENSIONS—INCHES (MILLIMETERS)

#### Package 68-Lead PLCC

# THERMAL RESISTANCE CHARACTERISTICS

|                   | PARAMETER                               | MAX | UNIT |

|-------------------|-----------------------------------------|-----|------|

| ReJA              | Junction to free air thermal resistance | 46  | °C W |

| R <sub>0</sub> JC | Junction to case thermal resistance     | 11  | °C W |

Devices sold by Sierra Semiconductor Corp. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Sierra Semiconductor Corp. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Sierra Semiconductor Corp. makes no warranty of merchantability or fitness for any purpose. Sierra Semiconductor Corp. reserves the right to discontinue production and change specifications and prices at any time and without notice.

This product is intended for use in normal commercial applications. Applications requiring an extended temperature range, unusual environmental requirements, or high reliability applications, such as military and aerospace, are specifically not recommended without additional processing by Sierra Semiconductor Corp.

Sierra Semiconductor assumes no responsibility for the use of any circuitry other than circuitry embodied in a Sierra Semiconductor Corp. product. No other circuits, patents, licenses are implied.

#### Life Support Policy

Sierra Semiconductor Corporation's products are not authorized for use as critical components in life support devices or systems.

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

© 1992 SIERRA SEMICONDUCTOR CORPORATION, 2075 North Capitol Avenue, San Jose CA 95132, (408) 263-9300 TELEX 384467

16

Printed in U.S.A. 018025-072