# Burroughs B6700 Information Processing Systems REFERENCE MANUAL

# Burroughs B 6700 INFORMATION PROCESSING SYSTEMS REFERENCE MANUAL

**Burroughs Corporation**

Detroit, Michigan 48232

\$7.50

#### COPYRIGHT© 1969, 1970, 1972 BURROUGHS CORPORATION AA119114, AA190266

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be forwarded using the Remarks Form at the back of the manual, or may be addressed directly to Systems Documentation, Sales Technical Services, Burroughs Corporation, 6071 Second Avenue, Detroit, Michigan 48232.

## **TABLE OF CONTENTS**

| SECTIO | N TITLE                                   | PAGE |

|--------|-------------------------------------------|------|

|        | INTRODUCTION                              | xxi  |

| 1      | SYSTEMS DESCRIPTION                       |      |

|        | General                                   |      |

|        | Description of Units                      |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           | 1-4  |

|        |                                           |      |

|        |                                           |      |

|        |                                           | 1-5  |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        | Operator-Dependent Processor Interrupts   |      |

|        | Operator-Independent Processor Interrupts |      |

|        | External Interrupts                       |      |

|        | Main Memory                               |      |

|        | Memory Words                              |      |

|        |                                           |      |

|        |                                           |      |

|        | Input/Output Processor                    |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

|        |                                           | 1-12 |

|        | •                                         | 112  |

|        |                                           | 1-12 |

|        |                                           | 1-12 |

|        | Real-Time Adapter                         |      |

| 2      | DATA REPRESENTATION                       |      |

|        |                                           |      |

|        |                                           | 2-1  |

|        |                                           |      |

|        |                                           |      |

|        |                                           |      |

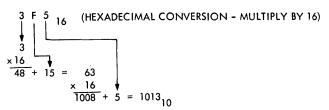

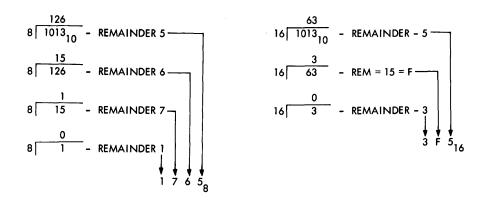

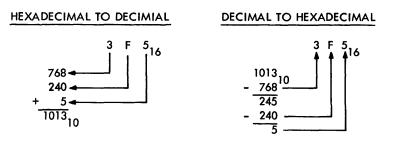

|        | Coded to Decimal Conversion               |      |

|        | Decimal to Coded                          |      |

|        | Decimal and Hexadecimal Table Conversion  | 2-2  |

|        |                                           |      |

|        |                                           |      |

| SECTIO | N TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PAGE |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|        | Order of Magnitude Data Types and Physical Layout Character Type Operands Mantissa Field Logical Operands Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 3      | STACK AND POLISH NOTATION The Stack General Base and Limit of Stack Bi-Directional Data Flow In the Stack Double-Precision Stack Operation Data Addressing Data Descriptor Presence Bit Index Bit Invalid Index Valid Index Read-Only Bit Copy Bit Polish Notation General Simplified Rules for Generation of Polish String Polish String Rules for Evaluating a Polish String Simple Stack Operation Program Structure In Memory Memory Area Allocation Stack-History and Addressing-Environment Lists Mark Stack Control Word Linkage Stack Deletion Relative-Addressing Base of Address Conversion Multiple Variable with Common Address Couples Address Environment Defined Mark Stacks and Re-Entrant Code Level Definition Re-Entrance Job-Splitting Stack Vector Descriptor |      |

| 4      | Presence Bit Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-1  |

|        | Processor Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1  |

| SECTION | TITLE                                    | PAGE |

|---------|------------------------------------------|------|

|         | General                                  | 4-1  |

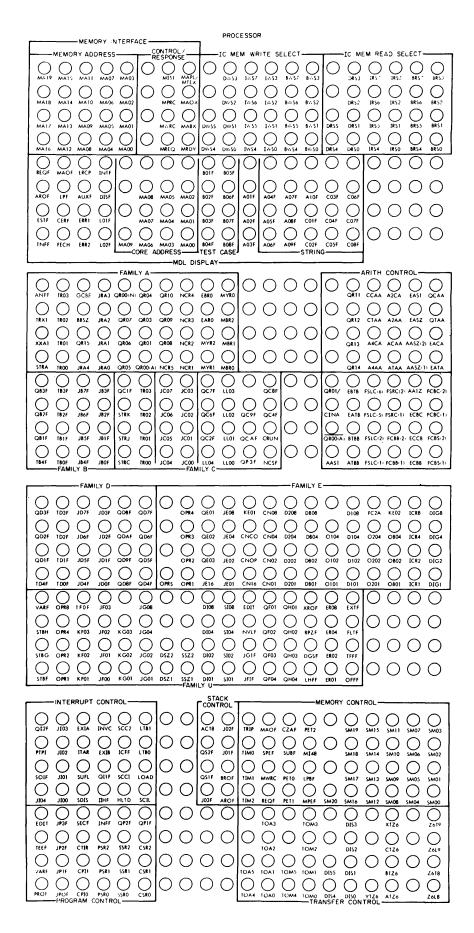

|         | Panel A                                  | 4-1  |

|         | P Register                               | 4-1  |

|         | C Register                               | 4-1  |

|         | A Register                               | 4-1  |

|         | B Register                               | 4-1  |

|         | X Register                               | 4-1  |

|         | Y Register                               |      |

|         | Panel B                                  |      |

|         | Row A                                    |      |

|         | IC Mem Read Select                       |      |

|         | IC Mem Write Select                      |      |

|         | Memory Interface                         |      |

| ***     | Control/Response                         |      |

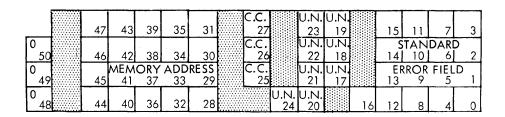

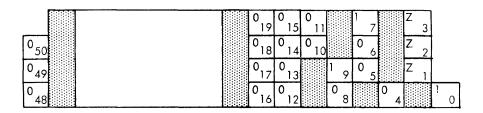

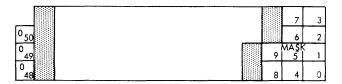

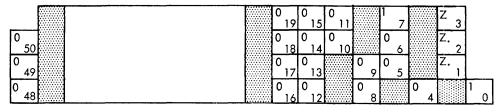

|         | Memory Address                           |      |

|         | Row B                                    |      |

|         | Row C                                    |      |

|         | Family A                                 |      |

|         | Arithmetic Control                       |      |

|         | Row D                                    |      |

|         |                                          |      |

|         | ·                                        |      |

|         | Family C                                 |      |

|         |                                          |      |

|         | Family D                                 |      |

|         | Family E                                 |      |

|         | Row F                                    |      |

|         | Row G                                    |      |

|         | Interrupt Control                        |      |

|         | Stack Control                            |      |

|         | Memory Control                           |      |

|         | Row H                                    |      |

|         | Program Control                          |      |

|         | Transfer Controller                      |      |

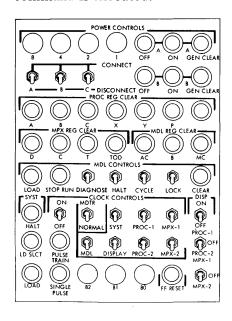

|         | General Maintenance Controls             |      |

|         | Power Controls                           |      |

|         | General Clear and Halt-Load Function     |      |

|         | Processor Register Clear                 |      |

|         | Input/Output Processor Register Clear    |      |

|         | MDL Register Clear                       |      |

|         | MDL Control Switches                     |      |

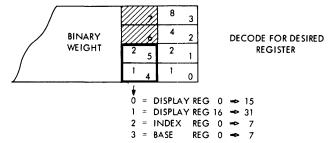

|         | Display Select Switches                  |      |

|         | Clock Controls                           | 4-10 |

|         | Single Pulse Switch                      | 4-10 |

|         | Pulse Train Switch                       | 4-10 |

|         | Indicators B0, B1, B2                    | 4-10 |

|         | MDTR/Normal Switch                       |      |

|         | FF Reset Switch                          |      |

|         | Halt Load and Load Select Switches       | 4-10 |

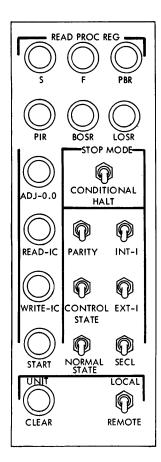

|         | Processor Maintenance Controls (Panel E) |      |

|         | Start Switch                             |      |

| SECTION | TITLE                                            | PAGE |

|---------|--------------------------------------------------|------|

|         | Conditional Halt Switch                          | 4-11 |

|         | Stop Switches                                    |      |

|         | SECL Switch                                      |      |

|         | INT-I Switch                                     |      |

|         | EXT-I Switch                                     |      |

|         | Normal/Control State Switches                    |      |

|         | Parity Switch                                    |      |

|         | Unit Clear Switch                                |      |

|         | Local/Remote Switch                              |      |

|         | ADJ (0,0) Switch                                 |      |

|         | Read IC Switch                                   |      |

|         |                                                  |      |

|         | Read IC Operation                                |      |

|         | Write IC Switch                                  |      |

|         | Write IC Operation                               |      |

|         | Read Proc Reg Switches                           |      |

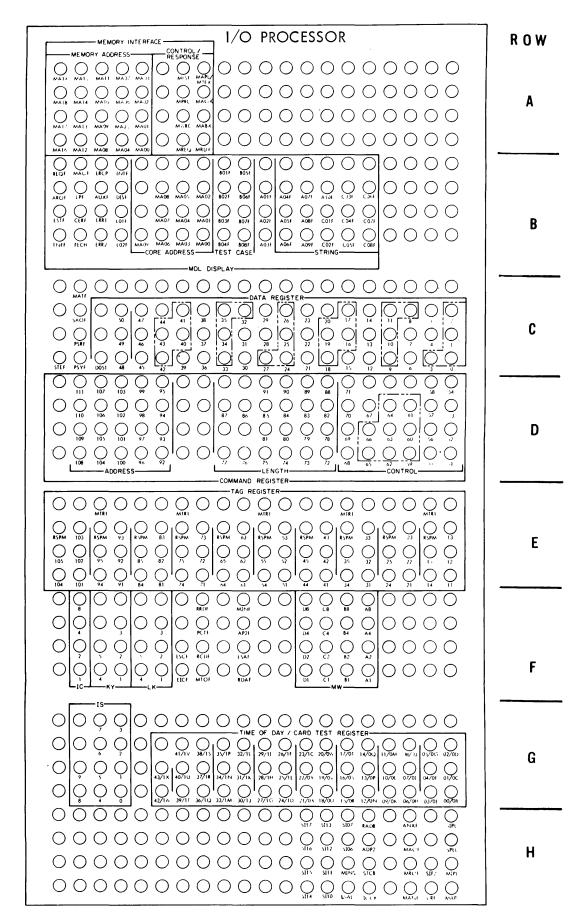

|         | Input/Output Processor Registers and Flip Flops  |      |

|         | Row B                                            |      |

|         | Row C                                            |      |

|         | Row D                                            |      |

|         | Row E                                            | 4-14 |

|         | Row F                                            | 4-14 |

|         | Row G                                            | 4-14 |

|         | Row H                                            | 4-14 |

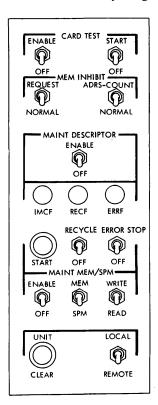

|         | Input/Output Processor Maintenance Control Panel |      |

|         | Write SPM                                        | 4-16 |

|         | Read SPM                                         |      |

|         | Write Main Memory                                |      |

|         | Read Main Memory                                 |      |

|         | Executing I/O Descriptors                        |      |

|         | Single Cycle                                     |      |

|         | Recycle                                          |      |

|         | Logic Card Testing                               |      |

|         | Operators Control Console                        |      |

|         | Operator Panel                                   |      |

|         | Power On (Switch Indicator, White)               |      |

|         |                                                  |      |

|         | Power Off (Switch, Brown)                        | 4.10 |

|         | Halt (Switch/Indicator, Red)                     |      |

|         | Running (Indicator, Yellow)                      |      |

|         | Load Select (Switch/Indicator, Yellow)           |      |

|         | Load (Switch, Brown)                             |      |

|         | Card Load Operation                              |      |

|         | Disk Load Operation                              |      |

|         | Visual Message Control Center                    |      |

|         | Keyboard Control Keys                            |      |

|         | Memory Tester                                    |      |

|         | Non-Test                                         |      |

|         | Test                                             | 4-21 |

|         |                                                  |      |

| 5 SY    | STEM CONCEPT                                     | 5-1  |

|         | Canaral                                          | 5 1  |

| SECTION | TITLE                                         | PAGE |

|---------|-----------------------------------------------|------|

|         | Processor                                     | 5-1  |

|         | Operator Families                             |      |

|         | Program Controller                            |      |

|         | Transfer Controller                           |      |

|         | Stack Registers                               |      |

|         | Internal Data Transfer Section                |      |

|         | Mask and Steering                             |      |

|         | Mask and Steering Example                     |      |

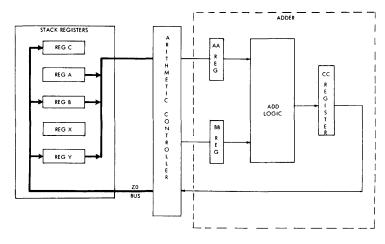

|         | Arithmetic Controller                         |      |

|         | High-Speed Adder                              |      |

|         | Interrupt Controller                          |      |

|         | Operator-Dependent Interrupts                 |      |

|         |                                               |      |

|         | Memory Protect                                |      |

|         | Invalid Operand                               |      |

|         | Divide by Zero                                |      |

|         | Exponent Overflow and Underflow               |      |

|         | Invalid Index                                 |      |

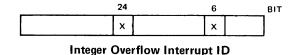

|         | Integer Overflow                              |      |

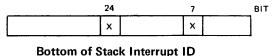

|         | Bottom of Stack                               |      |

|         | Presence Bit                                  |      |

|         | Data-Dependent Presence Bit                   |      |

|         | Procedure-Dependent Presence Bit              |      |

|         | Program Restart                               |      |

|         | Segmented Array                               |      |

|         | Programed Operator                            |      |

|         | Operator-Independent Interrupts               | 5-8  |

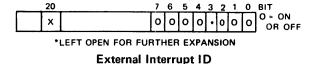

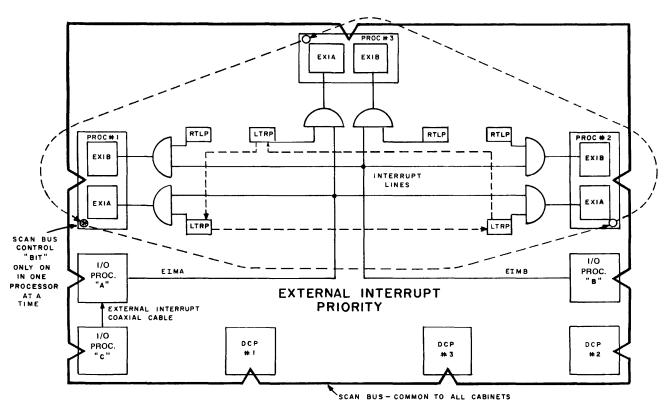

|         | External Interrupts                           | 5-8  |

|         | Processor to Processor                        | 5-9  |

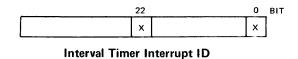

|         | Interval Timer                                | 5-9  |

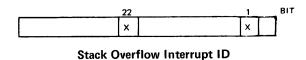

|         | Stack Overflow                                | 5-9  |

|         | Input/Output Processor Interrupts             |      |

|         | Scan Bus Control                              |      |

|         | Priority Handling                             |      |

|         | Priority-Handling Example with IIHF Off       |      |

|         | Priority-Handling Example with IIHF On        |      |

|         | I/O Finish and Data Communications Interrupts |      |

|         | General Control Adapter                       |      |

|         | Alarm Interrupts                              |      |

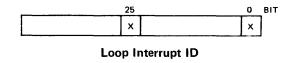

|         | Loop                                          |      |

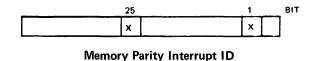

|         | Memory Parity                                 |      |

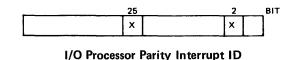

|         | I/O Processor Parity                          |      |

|         | Invalid Address                               |      |

|         | Stack Underflow                               |      |

|         | Invalid Program Word                          |      |

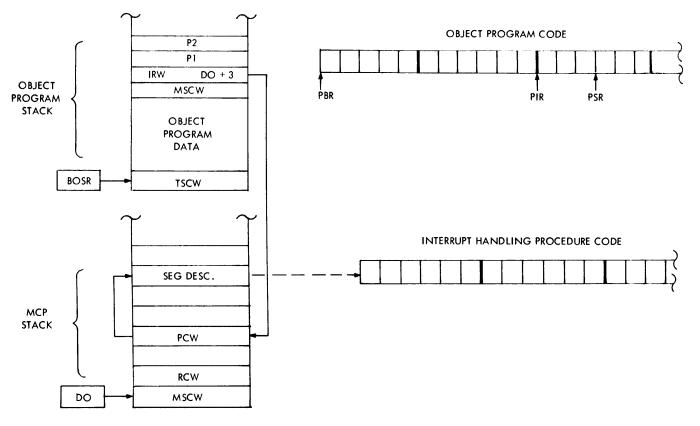

|         | Interrupt Handling                            |      |

|         | String Operator Controller                    |      |

|         | Control State/Normal State                    |      |

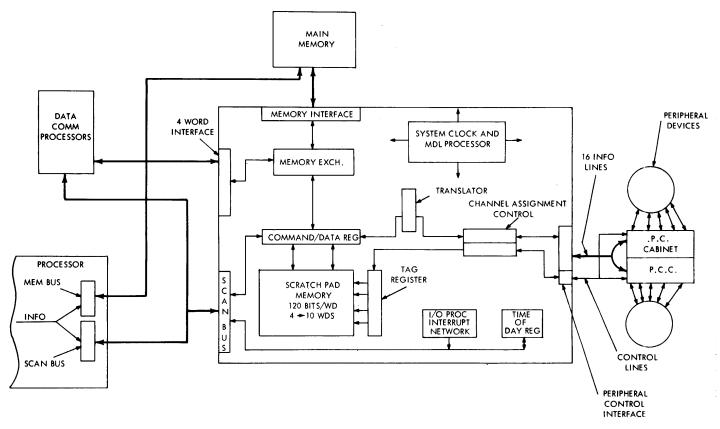

|         | Input/Output Processor                        |      |

|         | * ' *                                         |      |

|         | Scan Bus                                      |      |

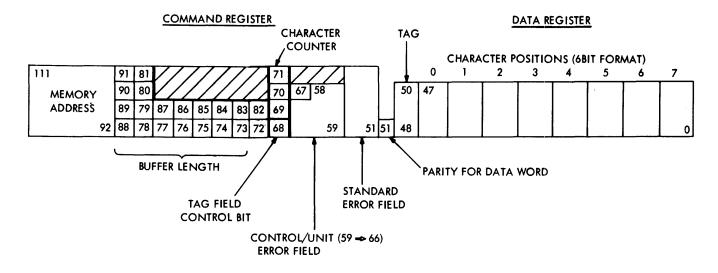

|         | Command Data Register                         | 5-14 |

| SECTION | N TITLE                                          | PAGE |

|---------|--------------------------------------------------|------|

|         | Scratch Pad Memory                               | 5-14 |

|         | Tag Register                                     | 5-15 |

|         | Memory Exchange                                  |      |

|         | Interrupt Network                                |      |

|         | Time of Day Register                             | 5-15 |

|         | Channel Assignment Control                       |      |

|         | Character Translator                             |      |

|         | Peripheral Control Interface                     |      |

|         | Data Communications Interface                    | 5-16 |

|         | System Clock Control and MDL Processor           |      |

|         | System Clock                                     |      |

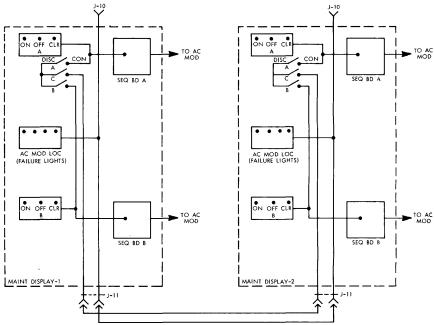

|         | Maintenance Diagnostic Processor                 | 5-17 |

|         | Display Mode                                     |      |

|         | Diagnose Mode                                    |      |

|         | Detect Mode                                      |      |

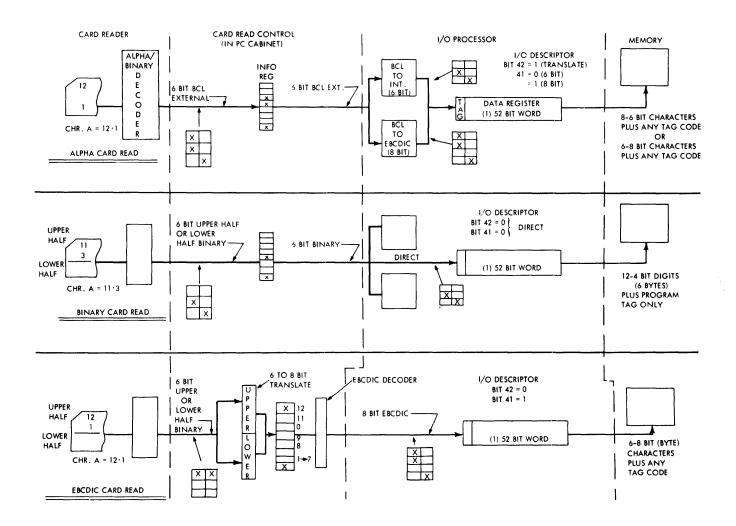

|         | Information Flow from Card Reader to Main Memory |      |

|         | Alpha Card Read                                  |      |

|         | Binary Card Read                                 |      |

|         | EBCDIC Card Read                                 |      |

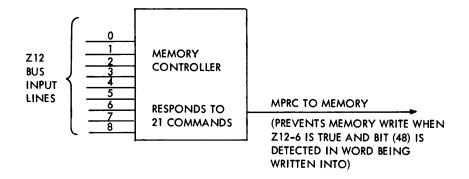

|         | Memory and Input/Output Processor Controller     |      |

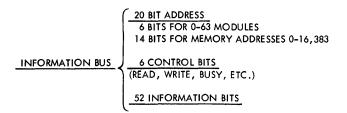

|         | Memory Bus                                       |      |

|         | Scan Bus                                         |      |

|         | Address Adder                                    |      |

|         | Integrated Circuit (IC) Memory                   |      |

|         | Main Memory                                      |      |

|         | Organization                                     |      |

|         | Memory Protection                                |      |

|         | Cabinet Configuration                            |      |

|         | Interface                                        |      |

|         | Priority                                         |      |

|         | Memory Registers                                 |      |

|         | Memory Addressing                                |      |

|         | Memory Interlacing                               |      |

|         | Memory Testing                                   |      |

|         | Stack Controller                                 |      |

|         | Buck Controller                                  |      |

| 6       | PROGRAM OPERATORS                                | 6-1  |

| Ü       | General                                          |      |

|         | Syllable Addressing and Syllable Identification  |      |

|         | Syllable Format and Addressing                   |      |

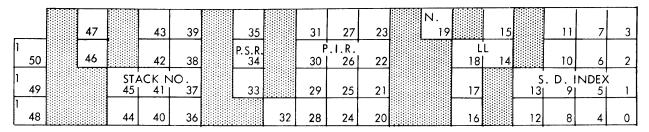

|         | P and T Registers                                |      |

|         | Operation Types                                  |      |

|         | Name Call                                        |      |

|         | Value Call                                       |      |

|         | Operators                                        |      |

|         | Word Data Descriptor                             |      |

|         | String Descriptor                                |      |

|         | Segment Descriptor                               |      |

|         | Mark Stack Control Word                          |      |

|         | Program Control Word                             |      |

|         | 1 10gram Common word                             | 0-0  |

| SECTION | I TITLE                                      | PAGE |

|---------|----------------------------------------------|------|

|         | Return Control Word                          | 6-6  |

|         | Indirect Reference Word                      |      |

|         | Stuffed Indirect Reference Word              |      |

|         | Step Index Word                              |      |

|         | •                                            |      |

| 7       | PRIMARY MODE OPERATORS                       |      |

|         | General                                      |      |

|         | Arithmetic Operators                         |      |

|         | Add (ADD) 80                                 |      |

|         | Subtract (SUBT) 81                           |      |

|         | Multiply (MULT) 82                           |      |

|         | Extended Multiply (MULX) 8F                  |      |

|         | Divide (DIVD) 83                             |      |

|         | Integer Divide (IDIV) 84                     |      |

|         | Remainder Divide (RDIV) 85                   |      |

|         | Integerize, Truncated (NTIA) 86              |      |

|         | Integerize, Rounded (NTGR) 87                |      |

|         | Type-Transfer Operators                      | 7-3  |

|         | Set to Single-Precision, Truncated (SNGT) CC |      |

|         | Set to Single-Precision, Rounded (SNGL) CD   |      |

|         | Set to Double-Precision (XTND) CE            |      |

|         | Logical Operators                            |      |

|         | Logical And (LAND) 90                        |      |

|         | Logical Or (LOR) 91                          | 7-4  |

|         | Logical Negate (LNOT) 92                     | 7-4  |

|         | Logical Equivalence (LEQV) 93                | 7-4  |

|         | Relational Operators                         | 7-4  |

|         | Logical Equal (SAME) 94                      | 7-4  |

|         | Greater Than (GRTR) 8A                       | 7-4  |

|         | Greater Than or Equal (GREQ) 89              |      |

|         | Equal (EQUL) 8C                              |      |

|         | Less Than or Equal (LSEQ) 8B                 |      |

|         | Less Than (LESS) 88                          |      |

|         | Not Equal (NEQL) 8D                          |      |

|         | Branch Operators                             |      |

|         | Branch False (BRFL) A0                       |      |

|         | Branch True (BRTR) A1                        | 7-5  |

|         | Branch Unconditional (BRUN) A2               | 7-5  |

|         | Dynamic Branch False (DBFL) A8               |      |

| •       | Dynamic Branch True (DBTR) A9                | 7-5  |

|         | Dynamic Branch Unconditional (DBUN) AA       |      |

|         | Step and Branch (STBR) A4                    | 7-5  |

|         | Universal Operators                          |      |

|         | No Operation (NOOP) FE                       | 7-6  |

|         | Conditional Halt (HALT) DF                   |      |

|         | Invalid Operator (NVLD) FF                   |      |

|         | Store Operators                              |      |

|         | Store Destructive (STOD) B8                  |      |

|         | Store Non-Destructive (STON) B9              |      |

|         | Overwrite Destructive (OVRD) BA              |      |

| SECTION | TITLE                                                  | PAGE   |

|---------|--------------------------------------------------------|--------|

|         | Overwrite Non-Destructive (OVRN) BB                    | 7-6    |

|         | Stack Operators                                        |        |

|         | Exchange (EXCH) B6                                     |        |

|         | Delete Top Of Stack (DLET) B5                          |        |

|         | Duplicate Top Of Stack (DUPL) B7                       |        |

|         | Push Down Stack Registers (PUSH) B4                    |        |

|         | Literal Call Operators                                 |        |

|         | Lit Call Zero (ZERO) B0                                |        |

|         | Lit Call One (ONE) B1                                  |        |

|         | Lit Call 8 Bits (LT8) B2                               |        |

|         | Lit Call 16 Bits (LT16) B3                             |        |

|         | Lit Call 48 Bits (LT48) BE                             |        |

|         | Make Program Control Word (MPCW) BF                    |        |

|         | Index and Load Operators                               |        |

|         | Index (INDX) A6                                        |        |

|         |                                                        |        |

|         | Index and Load Value (NXLN) A5                         |        |

|         | Index and Load Value (NXLV) AD                         |        |

|         | Load (LOAD) BD                                         |        |

|         | Scale Operators                                        |        |

|         | Scale Left (SCLF) C0                                   |        |

|         | Dynamic Scale Left (DSLF) C1                           |        |

|         | Scale Right Save (SCRS) C4                             |        |

|         | Dynamic Scale Right Save (DSRS) C5                     |        |

|         | Scale Right Truncate (SCRT) C2                         | /-8    |

|         | Dynamic Scale Right Truncate (DSRT) C3                 |        |

|         | Scale Right Final (SCRF) C6                            |        |

|         | Dynamic Scale Right Final (DSRF) C7                    |        |

|         | Scale Right Rounded (SCRR) C8                          | 7-9    |

|         | Dynamic Scale Right Round (DSRR) C9                    |        |

|         | Bit Operators                                          |        |

|         | Bit Set (BSET) 96                                      |        |

|         | Dynamic Bit Set (DBST) 97                              |        |

|         | Bit Reset (BRST) 9E                                    |        |

|         | Dynamic Bit Reset (DBRS) 9F                            |        |

|         | Change Sign Bit (CHSN) 8E                              |        |

|         | Transfer Operators                                     |        |

|         | Field Transfer (FLTR) 98                               | 7-9    |

|         | Dynamic Field Transfer (DFTR) 99                       |        |

|         | Field Isolate (ISOL) 9A                                |        |

|         | Dynamic Field Isolate (DISO) 9B                        | . 7-10 |

|         | Field Insert (INSR) 9C                                 |        |

|         | Dynamic Field Insert (DINS) 9D                         | . 7-10 |

|         | String Transfer Operators                              | . 7-10 |

|         | Transfer Words, Destructive (TWSD) D3                  | . 7-10 |

|         | Transfer Words, Update (TWSU) DB                       | . 7-11 |

|         | Transfer Words, Overwrite Destructive (TWOD) D4        |        |

|         | Transfer Words, Overwrite Update (TWOU) DC             | . 7-11 |

|         | Transfer While Greater, Destructive (TGTD) E2          | 7-11   |

|         | Transfer While Greater, Update (TGTU) EA               | . 7-11 |

|         | Transfer While Greater or Equal, Destructive (TGED) E1 | . 7-11 |

| SECTION | TITLE                                                      | PAGE |

|---------|------------------------------------------------------------|------|

|         | Transfer While Greater or Equal, Update (TGEU) E9          | 7-11 |

|         | Transfer While Equal, Destructive (TEQD) E4                |      |

|         | Transfer While Equal, Update (TEQU) EC                     |      |

|         | Transfer While Less or Equal, Destructive (TLED) E3        |      |

|         | Transfer While Less or Equal, Update (TLEU) EB             |      |

|         | Transfer While Less, Destructive (TLSD) E0                 |      |

|         | Transfer While Less, Update (TLSU) E8                      |      |

|         | Transfer While Not Equal, Destructive (TNED) E5            |      |

|         | Transfer While Not Equal, Update (TNEU) ED                 |      |

|         | Transfer Unconditional, Destructive (TUND) E6              |      |

|         | Transfer Unconditional, Update (TUNU) EE                   |      |

|         | String Isolate (SISO) D5                                   |      |

|         | Compare Operators                                          |      |

|         | Compare Characters Greater, Destructive (CGTD) F2          |      |

|         | Compare Characters Greater, Update (CGTU) FA               |      |

|         | Compare Characters Greater or Equal, Destructive (CGED) F1 |      |

|         | Compare Characters Greater or Equal, Update (CGEU) F9      |      |

|         | Compare Characters Equal, Destructive (CEQD) F4            |      |

|         | Compare Characters Equal, Update (CEGU) FC                 |      |

|         | Compare Characters Less or Equal, Destructive (CLED) F3    |      |

|         | Compare Characters Less or Equal, Update (CLEU) FB         |      |

|         | Compare Characters Less, Destructive (CLSD) F0             |      |

|         | Compare Characters Less, Update (CLSU) F8                  |      |

|         | Compare Characters Not Equal, Destructive (CNED) F5        |      |

|         | Compare Characters Not Equal, Update (CNEU) FD             |      |

|         | Edit Operators                                             |      |

|         | Table Enter Edit, Destructive (TEED) D0                    |      |

|         | Table Enter Edit, Update (TEEU) D8                         | 7-14 |

|         | Execute Single Micro, Destructive (EXSD) D2                |      |

|         | Execute Single Micro, Update (EXSU) DA                     |      |

|         | Execute Single Micro, Single Pointer Update (EXPU) DD      |      |

|         | Pack Operators                                             |      |

|         | Pack, Destructive (PACD) D1                                | 7 14 |

|         | Pack, Update (PACU) D9                                     |      |

|         | Input Convert Operators                                    |      |

|         | Input Convert, Update (ICVU) CB                            |      |

|         | Read True False Flip Flop (RTFF) DE                        |      |

|         | Set External Sign (SXSN) D6                                |      |

|         | Read and Clear Overflow Flip Flop (ROFF) D7                | 7-15 |

|         | Subroutine Operators                                       |      |

|         | Value Call (VALC) 00⇒3F                                    |      |

|         | Name Call (NAMC) $40 \Rightarrow 7F$                       |      |

|         | Exit Operator (EXIT) A3                                    |      |

|         | Return Operator (RETN) A7                                  |      |

|         | Enter Operator (ENTR) AB                                   |      |

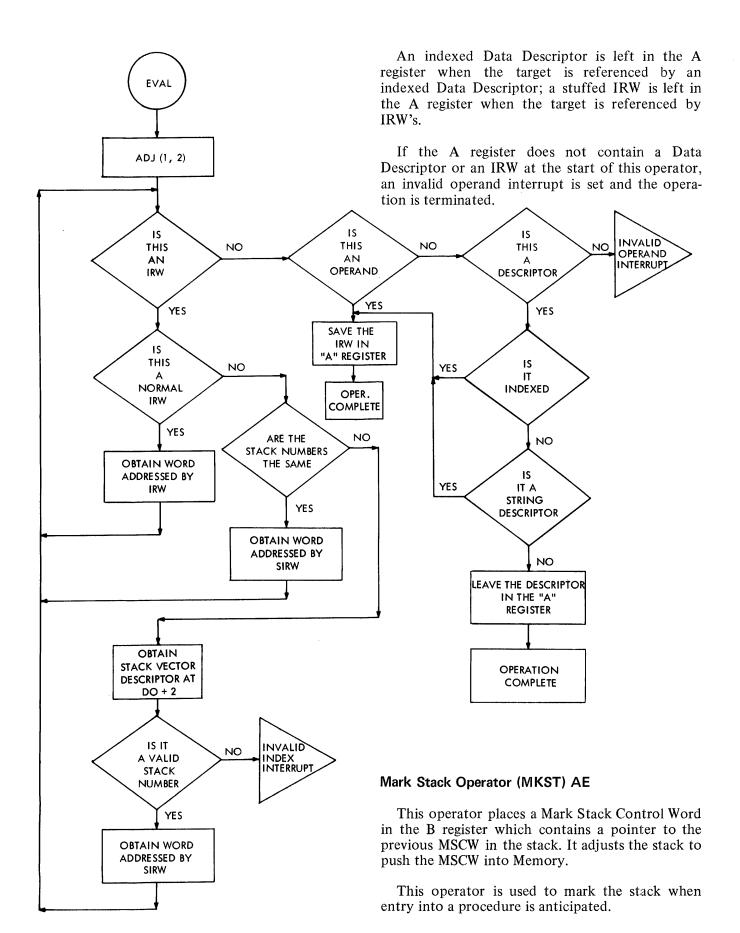

|         | Evaluate (EVAL) AC                                         |      |

|         | Mark Stack Operator (MKST) AE                              |      |

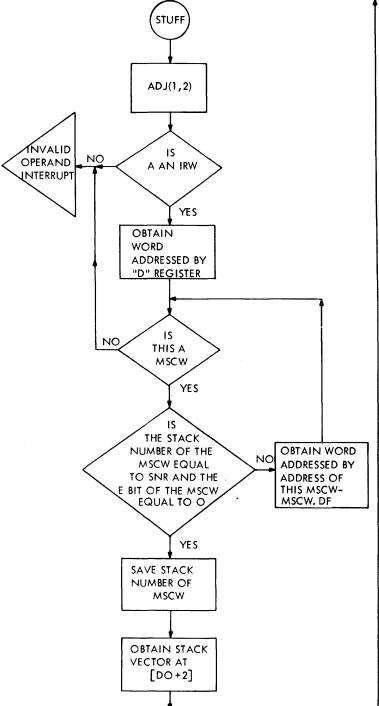

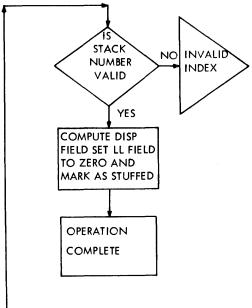

|         | Stuff Environment (STFF) AF                                |      |

|         | Insert Mark Stack Operator (IMKS) CF                       |      |

| SECTION | TITLE                                                   | PAGE |

|---------|---------------------------------------------------------|------|

| . 8 V   | ARIANT MODE OPERATION AND OPERATORS                     | 8-1  |

|         | General                                                 | 8-1  |

|         | Escape to 16-Bit Instruction (VARI) 95                  | 8-1  |

|         | Operators                                               | 8-1  |

|         | Set Two Singles to Double (JOIN) 9542                   | 8-1  |

|         | Set Double to Two Singles (SPLT) 9543                   | 8-1  |

|         | Idle Until Interrupt (IDLE) 9544                        | 8-1  |

|         | Set Interval Timer (SINT) 9545 (Control State Operator) | 8-1  |

|         | Enable External Interrupts (EEXI) 9546                  | 8-1  |

|         | Disable External Interrupts (DEXI) 9547                 |      |

|         | Scan Operators                                          | 8-1  |

|         | Scan In (SCNI) 954A                                     |      |

|         | Read Time Of Day Clock                                  | 8-2  |

|         | Read General Control Adapter                            | 8-2  |

|         | Read Result Descriptor                                  |      |

|         | Read Interrupt Mask                                     |      |

|         | Read Interrupt Register                                 |      |

|         | Read Interrupt Literal                                  |      |

|         | Interrogate Peripheral Status                           | 8-5  |

|         | Interrogate Peripheral Unit Type                        | 8-6  |

|         | Interrogate I/O Path                                    | 8-7  |

|         | Scan Out (SCNO) 954B                                    |      |

|         | Set Time Of Day Clock                                   |      |

|         | Set General Control Adapter                             |      |

|         | Initiate I/O (Control State Only)                       |      |

|         | Read Processor Identification (WHOI) 954E               | 8-10 |

|         | Interrupt Other Processor (HEYU) 954F                   | 8-10 |

|         | Occurs Index (OCRX) 9585                                | 8-10 |

|         | Integerized, Rounded, Double-Precision (NTGD) 9587      | 8-11 |

|         | Leading One Test (LOG2) 958B                            | 8-11 |

|         | Move To Stack (MVST) 95AF                               | 8-11 |

|         | Set Tag Field (STAG) 95B4                               | 8-12 |

|         | Read Tag Field (RTAG) 95B5                              | 8-12 |

|         | Rotate Stack Up (RSUP) 95B6                             | 8-12 |

|         | Rotate Stack Down (RSDN) 95B7                           | 8-12 |

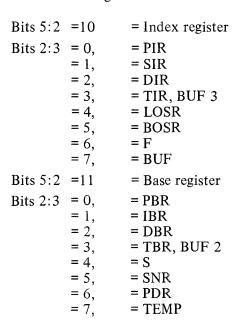

|         | Read Processor Register (RPRR) 95B8                     | 8-12 |

|         | Set Processor Register (SPRR) 95B9                      | 8-13 |

|         | Read With Lock (RDLK) 95BA                              | 8-13 |

|         | Count Binary Ones (CBON) 95BB                           | 8-13 |

|         | Load Transparent (LODT) 95BC                            | 8-13 |

|         | Linked List Lookup (LLLU) 95BD                          | 8-13 |

|         | Masked Search for Equal (SRCH) 95BE                     | 8-13 |

|         | Unpack Absolute, Destructive (UABD) 95D1                | 8-14 |

|         | Unpack Absolute, Update (UABU) 95D9                     | 8-14 |

|         | Unpack Signed, Destructive (USND) 95D0                  | 8-14 |

|         | Unpack Signed, Update (USNU) 95D8                       | 8-14 |

|         | Transfer While True, Destructive (TWTD) 95D3            | 8-14 |

|         | Transfer While True, Update (TWTU) 95DB                 | 8-14 |

|         | Transfer While False, Destructive (TWFD) 95D2           | 8-14 |

|         | Transfer While False Undate (TWFU) 95DA                 | Q 11 |

| SECTION | N TITLE                                              | PAGE |

|---------|------------------------------------------------------|------|

|         | Translate (TRNS) 95D7                                | 8-15 |

|         | Scan While Greater, Destructive (SGTD) 95F2          | 8-15 |

|         | Scan While Greater, Update (SGTU) 95FA               |      |

|         | Scan While Greater or Equal, Destructive (SGED) 95F1 |      |

|         | Scan While Greater or Equal, Update (SGEU) 95F9      |      |

|         | Scan While Equal, Destructive (SEQD) 95F4            |      |

|         | Scan While Equal, Update (SEQU) 95FC                 |      |

|         | Scan While Less or Equal, Destructive (SLED) 95F3    | 8-15 |

|         | Scan While Less or Equal, Update (SLEU) 95FB         |      |

|         | Scan While Less, Destructive (SLSD) 95F0             |      |

|         | Scan While Less, Update (SLSU) 95F8                  |      |

|         | Scan While Not Equal, Destructive (SNED) 95F5        | 8-16 |

|         | Scan While Not Equal, Update (SNEU) 95FD             |      |

|         | Scan While True, Destructive (SWTD) 95D5             |      |

|         | Scan While True, Update (SWTU) 95DD                  |      |

|         |                                                      |      |

|         | Scan While False, Destructive (SWFD) 95D4            |      |

|         | Scan while False, Opdate (SWFO) 93DC                 | 8-10 |

| 9       | EDIT MODE OPERATION AND OPERATORS                    | 9-1  |

|         | General                                              |      |

|         | Edit Mode Operators                                  |      |

|         | Move Characters (MCHR) D7                            |      |

|         | Move Numeric Unconditional (MVNU) D6                 | 9-1  |

|         | Move With Insert (MINS) D0                           |      |

|         | Move With Float (MFLT) D1                            |      |

|         | Skip Forward Source Characters (SFSC) D2             |      |

|         | Skip Reverse Source Characters (SRSC) D3             |      |

|         | Skip Forward Destination Characters (SFDC) DA        |      |

|         | Skip Reverse Destination Characters (SRDC) DB        |      |

|         | Reset Float (RSTF) D4                                |      |

|         | End Float (ENDF) D5                                  |      |

|         | Insert Unconditional (INSU) DC                       |      |

|         | Insert Conditional (INSC) DD                         |      |

|         | Insert Display Sign (INSG) D9                        |      |

|         | Insert Overpunch (INOP) D8                           |      |

|         | End Edit (ENDE) DE                                   |      |

|         | End Edit (ENDE) DE                                   |      |

| 10      | INPUT/OUTPUT PROCESSOR AND PERIPHERAL CONTROLS       | 10-1 |

|         | General                                              | 10-1 |

|         | Operation                                            | 10-1 |

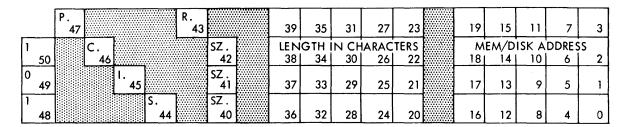

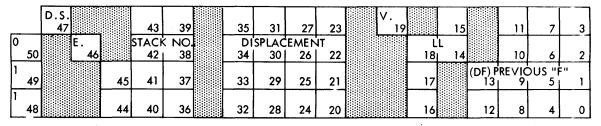

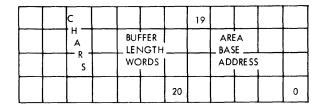

|         | Descriptor Formats                                   | 10-2 |

|         | Function Word                                        | 10-2 |

|         | Area Descriptor                                      |      |

|         | I/O Control Word                                     |      |

|         | Result Descriptor                                    |      |

|         | Peripheral Units and Associated Peripheral Controls  | 10-3 |

|         | Console                                              |      |

|         | Card Reader                                          |      |

|         | Card Punch                                           |      |

|         | Line Printers                                        |      |

|         |                                                      |      |

| SECTIO | N TITLE                                          | PAGE  |

|--------|--------------------------------------------------|-------|

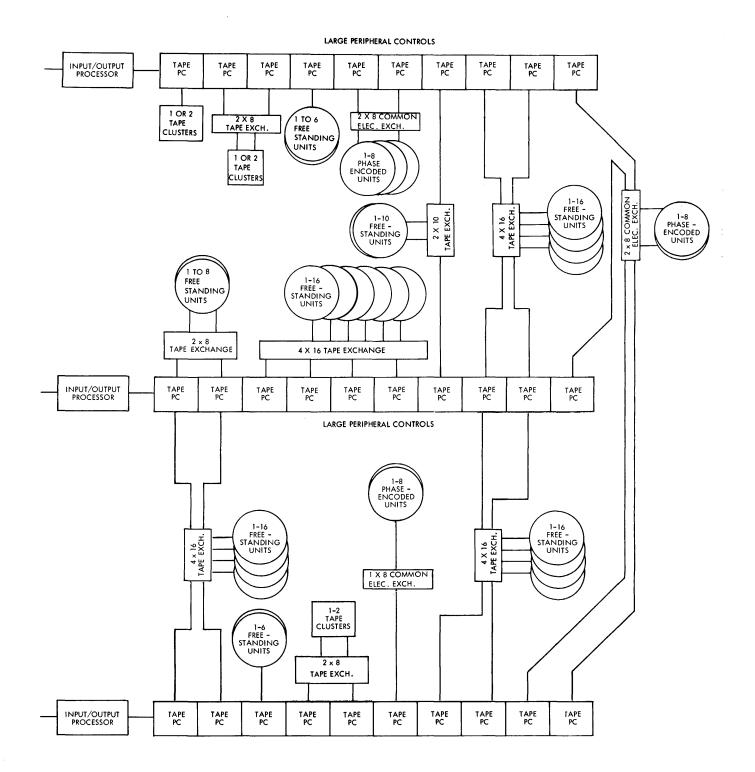

|        | Magnetic Tape Subsystem                          | 10-11 |

|        | Paper Tape                                       |       |

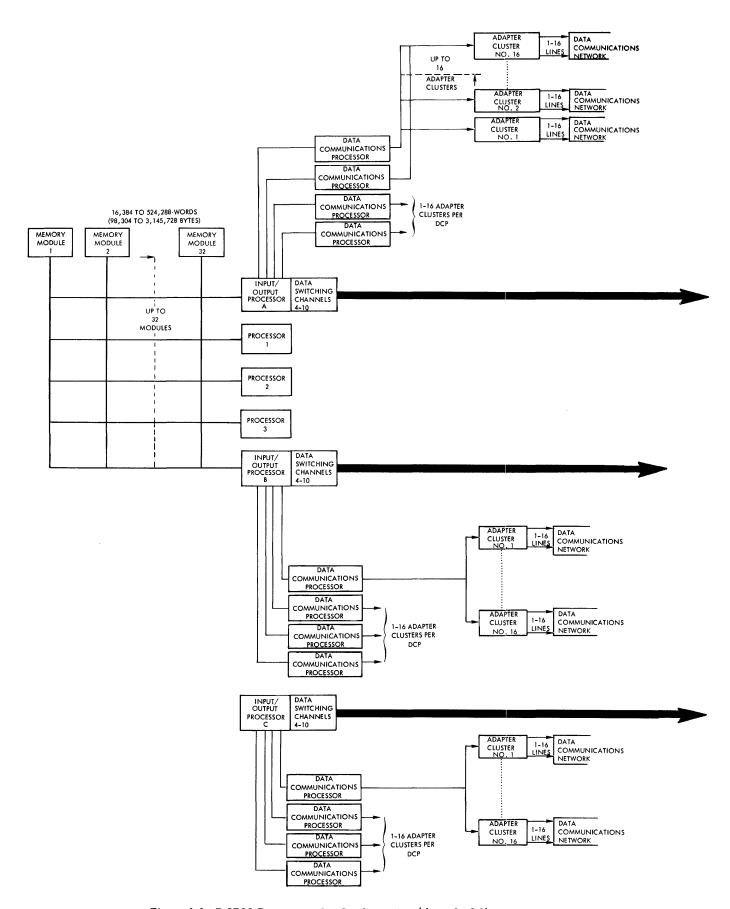

| 11     | B6700 DATA COMMUNICATIONS SYSTEM                 |       |

|        | General                                          |       |

|        | Data Communications Processor (DCP)              |       |

|        | Adapter Cluster                                  |       |

|        | Line Adapter                                     | 11-4  |

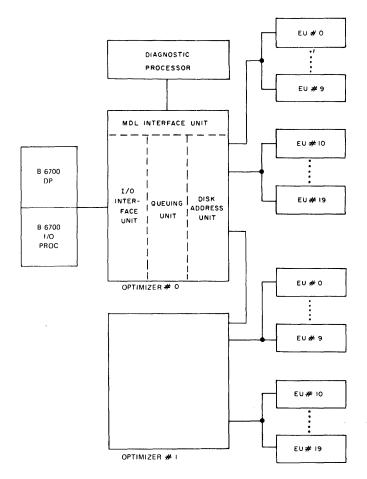

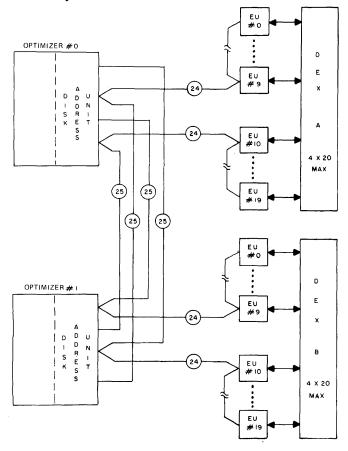

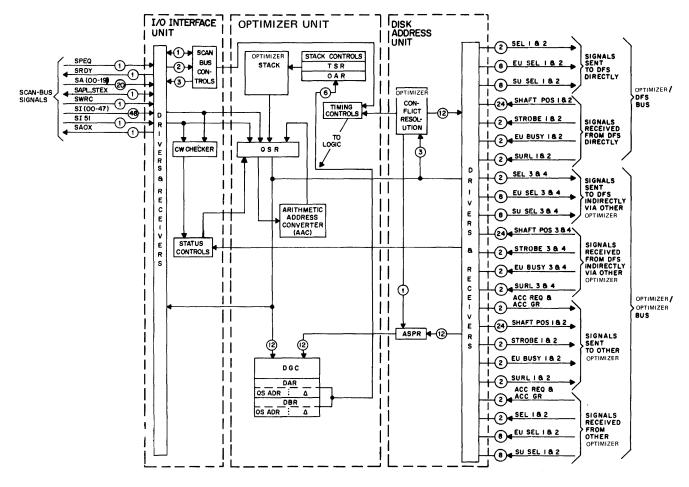

| 12     | DISK FILE OPTIMIZER                              | 12-1  |

|        | General                                          | 12-1  |

|        | Functional Characteristics                       |       |

|        | Functional Performance Characteristics           |       |

|        | Components                                       |       |

|        | Operational Characteristics                      |       |

|        | Accumulation of Control Words                    |       |

|        | Queuing the Control Words                        |       |

|        | Stack Operation                                  |       |

|        | Stack Erasure and Compression                    |       |

|        | Optimizer Dump                                   |       |

|        | Degraded Mode Operation                          |       |

|        | EU Conflict Resolution                           |       |

|        | Interface Requirements                           |       |

|        | Interface with the I/O Processor                 |       |

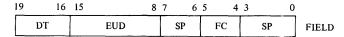

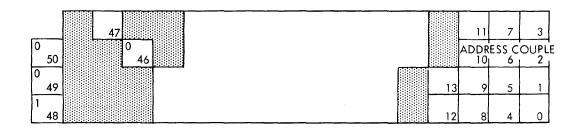

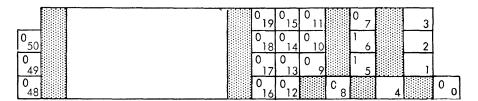

|        | Control Word                                     |       |

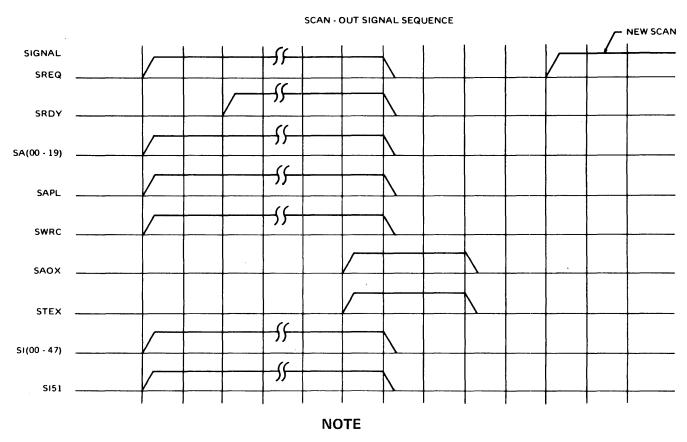

|        | Scan-Out                                         |       |

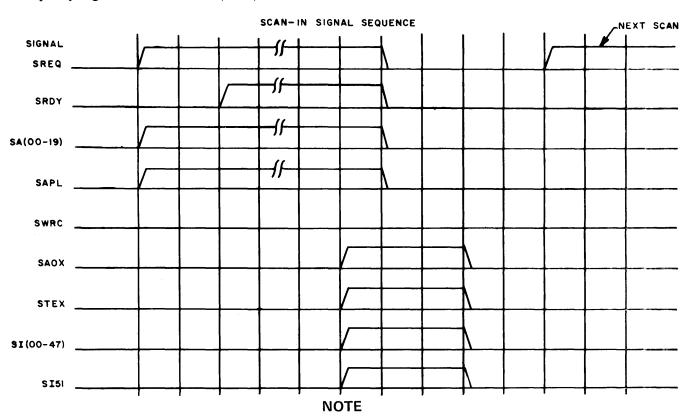

|        | Scan-In                                          |       |

|        | Scan Address Lines (SA)                          |       |

|        | Scan-Out Information Lines                       |       |

|        | Scan-In Information Lines (SI)                   |       |

|        | Dynamic Interaction with the B 6700              |       |

|        | Optimized Control Word Request                   |       |

|        | Top-of-Stack-Control Word Request                |       |

|        | Store the Control Word Request                   |       |

|        | Clear-the-Stack Request                          |       |

|        | First Stack Scan Cycle Incomplete                |       |

|        | Arithmetic Address Converter (AAC) Busy          |       |

|        | No Access to OEX                                 |       |

|        | SU Not Available                                 |       |

|        | Optimizer Stack (OS) Empty                       |       |

|        | Control Word Not Available                       | 12-8  |

|        | Scan Bus Parity Error                            | 12-8  |

|        | Optimizer Stack (OS) Parity Error                |       |

|        | Disk Address Error                               |       |

| -      | Optimizer Stack Full                             |       |

|        | Disk Interface                                   |       |

|        | Signals Sent Directly to the Disk File Subsystem | 12-9  |

| SECTION | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PAGE                                                                                                                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Signals Received Directly from the Disk File Subsystem Signals Sent to the Disk File Subsystem Via the Other Optimizer Signals Received From the Disk File Subsystem Via the Other Optimizer Signals Sent to the Other Optimizer Signals Received From the Other Optimizer Functional Units I/O Interface Unit Drivers (DR) and Receivers (RX) Scan Bus Controls Control Word (CW) Checker Status Controls Disk Address Unit Drivers and Receivers EU Conflict Resolution Actual Shaft Position Registers (ASPR) Optimizing Unit Arithmetic Address Converter (AAC) Optimizer Stack Optimizer Stack Optimizer Stack Register (OSR) Stack Controls Top-of-the-Stack Register (TSR) Optimizer Address Register (OAR) Delta Generator and Comparator (DGC) Delta A Register and Delta B Register (DAR and DBR) Timing Controls | . 12-10<br>. 12-10<br>. 12-11<br>. 12-11<br>. 12-11<br>. 12-11<br>. 12-11<br>. 12-11<br>. 12-12<br>. 12-12<br>. 12-13<br>. 12-13 |

| А       | APPENDIX A – OPERATORS, ALPHABETICAL LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A-1                                                                                                                                                                                                                                 |

| A       | APPENDIX B – OPERATORS, NUMERICAL LIST PRIMARY MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | B-1                                                                                                                                                                                                                                 |

| A       | APPENDIX C – CONTROL WORD FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C-1                                                                                                                                                                                                                                 |

| A       | APPENDIX D – SCAN FUNCTION CODE WORDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D-1                                                                                                                                                                                                                                 |

| Α       | APPENDIX E – DATA REPRESENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | E-1                                                                                                                                                                                                                                 |

| A       | APPENDIX F – B 6700 EBCDIC/HEX CARD CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | F-1                                                                                                                                                                                                                                 |

| A       | APPENDIX G – HEXADECIMAL-DECIMAL CONVERSION TABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | G-1                                                                                                                                                                                                                                 |

# LIST OF ILLUSTRATIONS

| FIGURE                                                                                      | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                   | PAGE |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

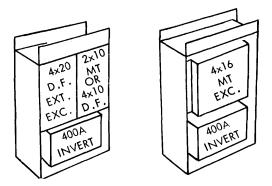

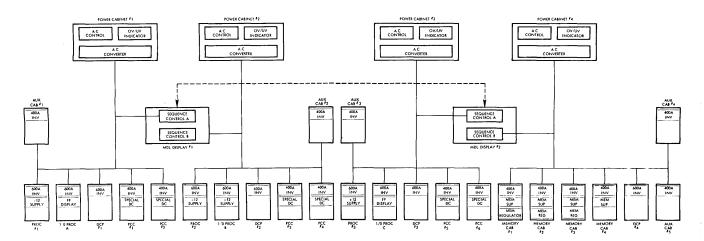

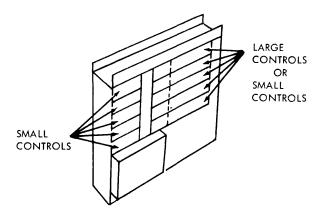

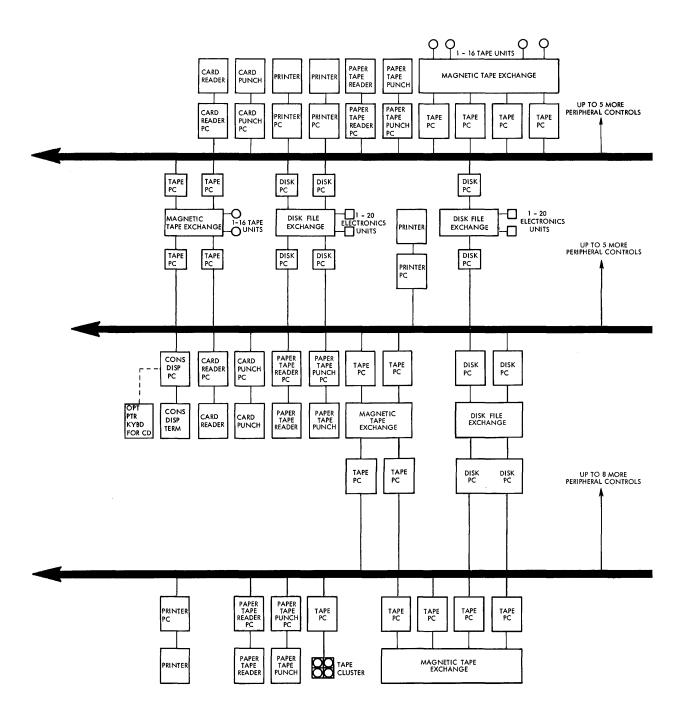

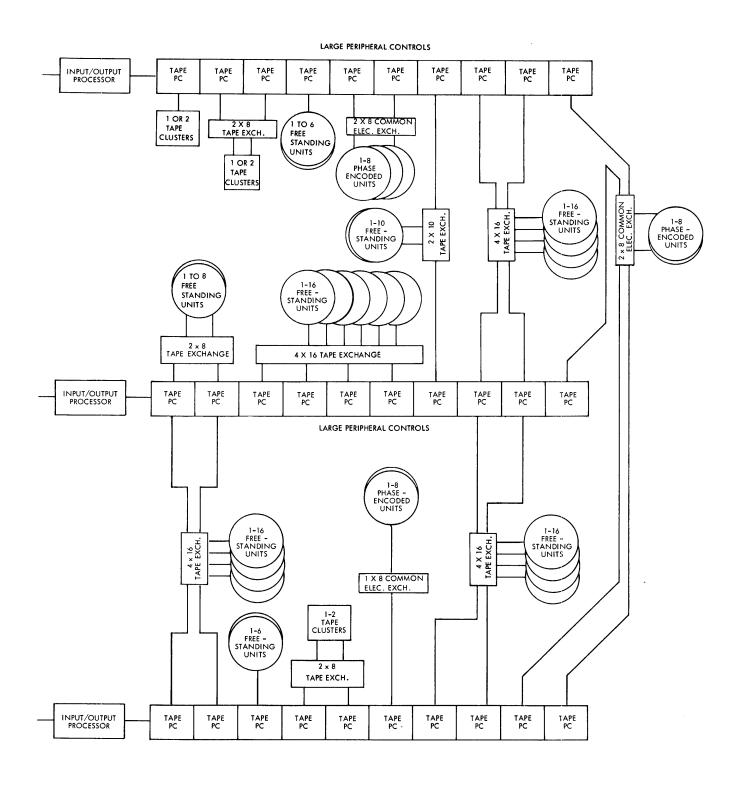

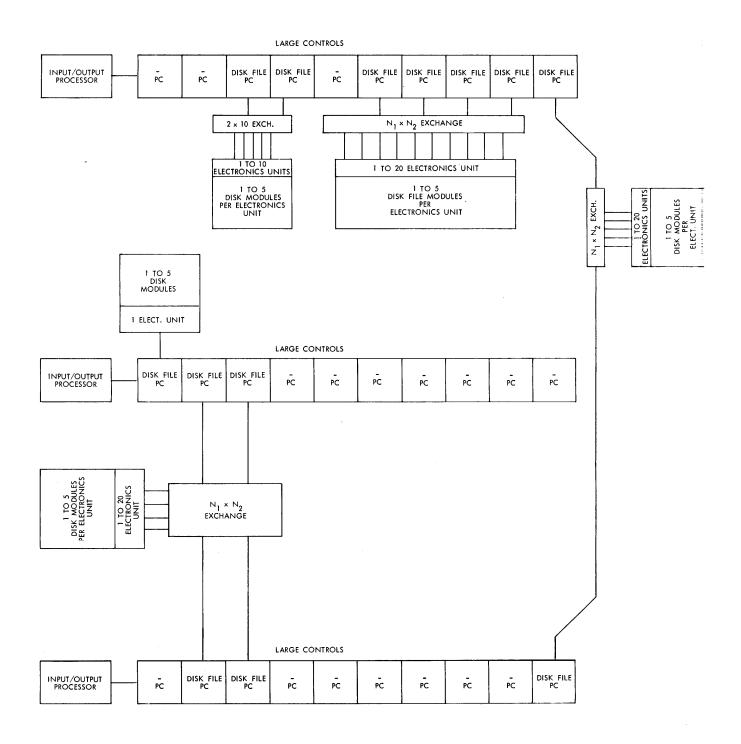

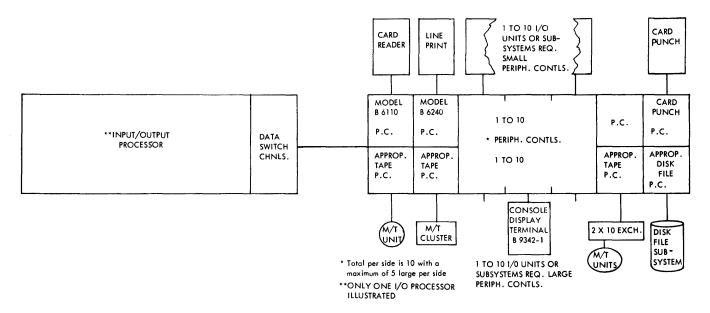

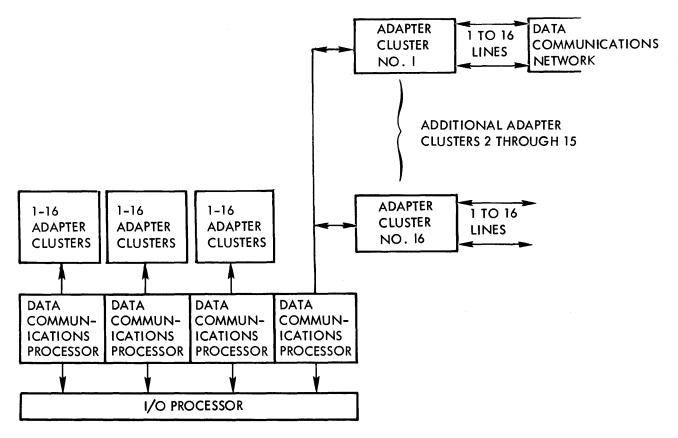

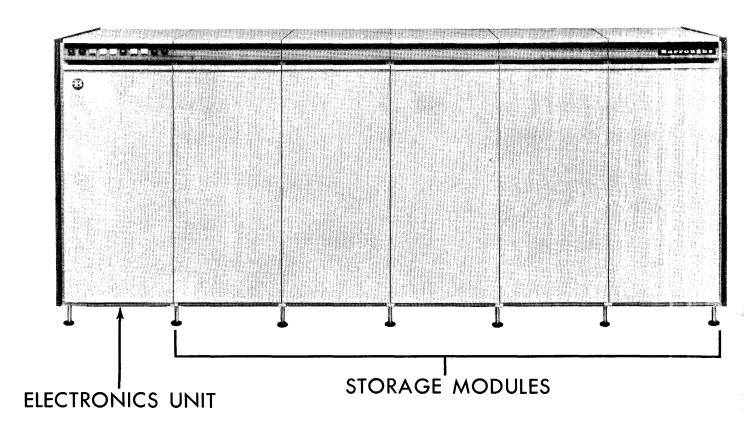

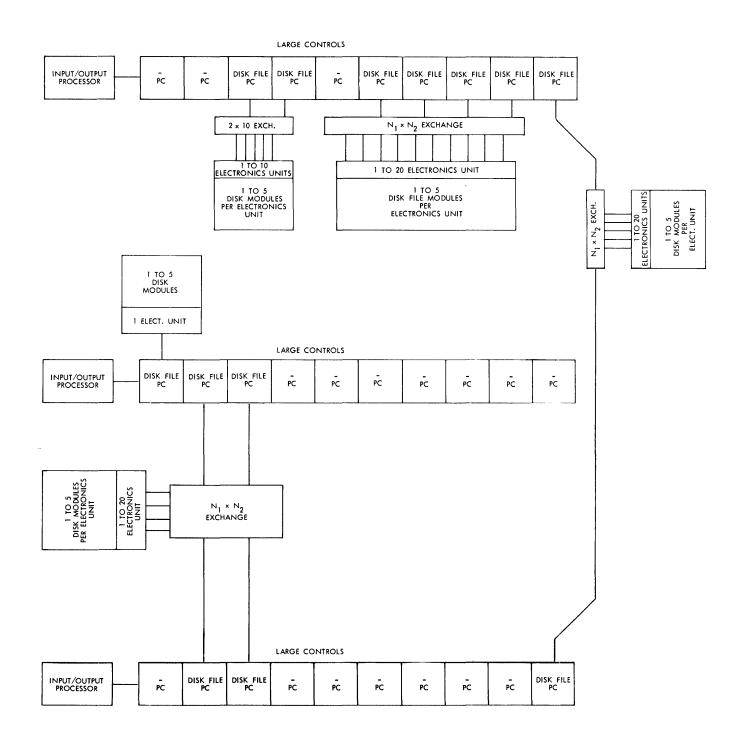

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8                                        | Auxiliary Cabinets  B 6700 Power Supply  Peripheral Control Cabinet  B 6700 Representative Configuration (Two Sheets)  Magnetic Tape Subsystem Relationships  Disk File Subsystem Relationships  Input/Output Subsystem  Organization of Data Communications Processor Remote Lines                                                                                                                                                     |      |

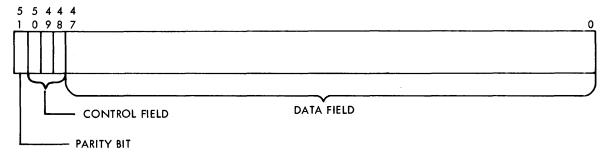

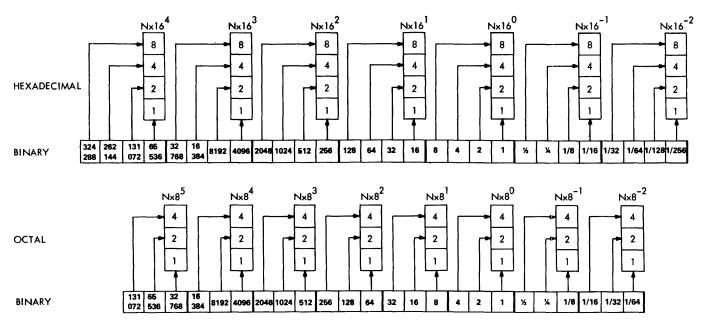

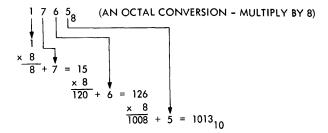

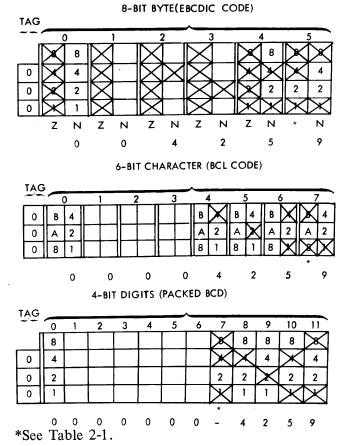

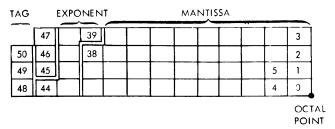

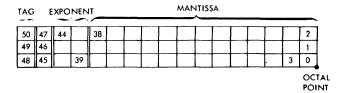

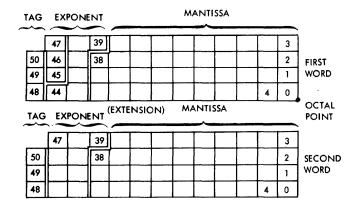

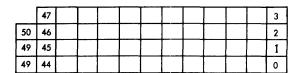

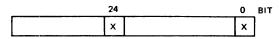

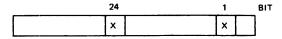

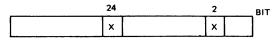

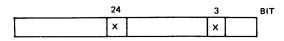

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12<br>2-13 | Basic Word Structure Number Base Graphic Characters Binary to Hexadecimal and Octal Conversion Relationship of Octal, Decimal and Hexadecimal Numbers Hexadecimal and Octal to Decimal Decimal 101310 to Hexadecimal and Octal HEX and DEC Table Conversion Order of Magnitude Table (-4259) in 8-, 6-, and 4-Bit Code Single-Precision Operand (Hexadecimal) Single-Precision Operand (Octal) Double-Precision Operand Logical Operand |      |

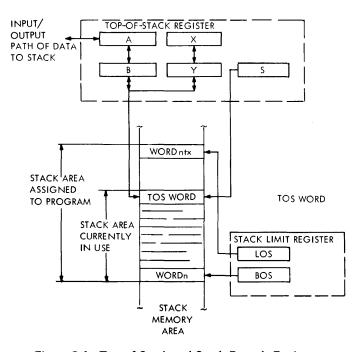

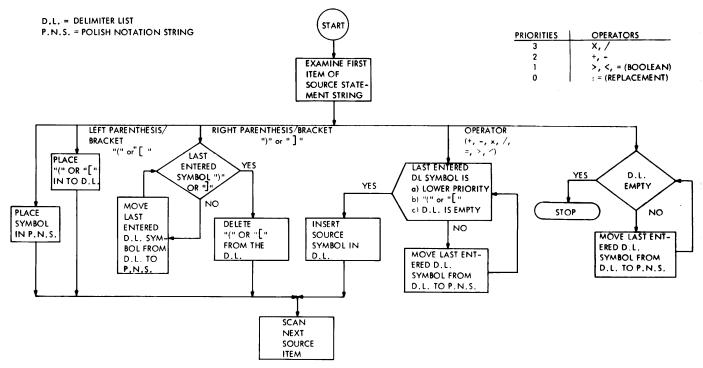

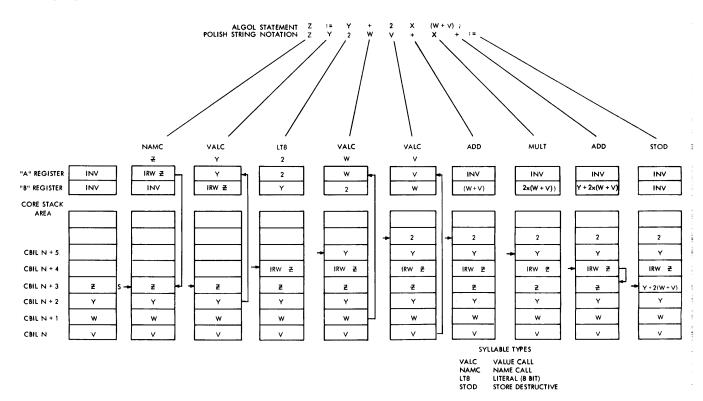

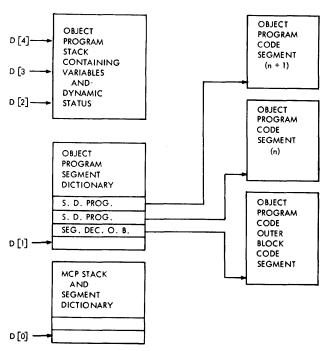

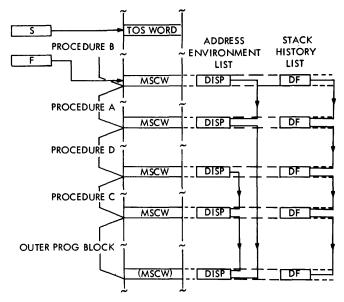

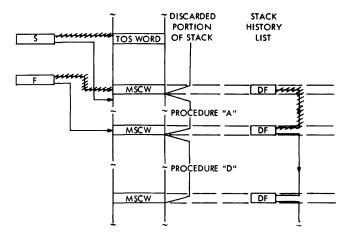

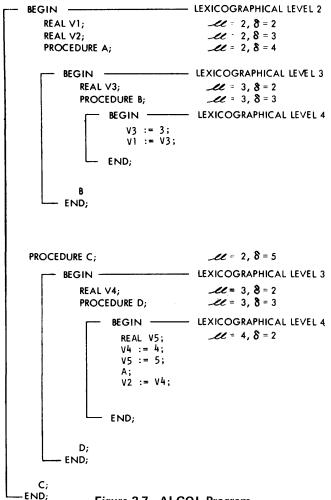

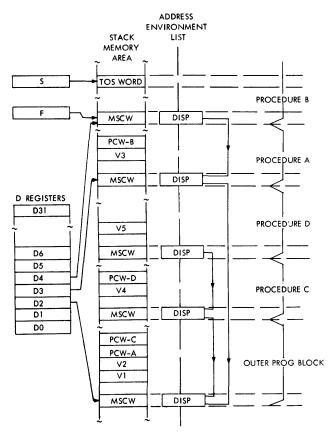

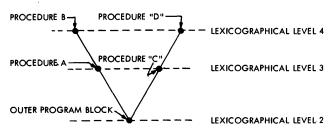

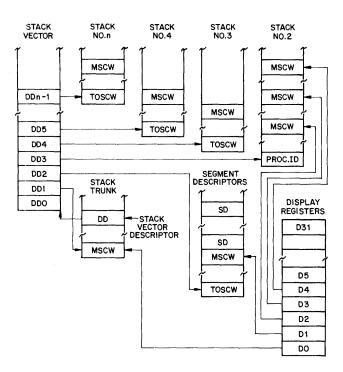

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10                         | Top of Stack and Stack Bounds Registers Polish Notation Flow Chart Stack Operation Object Program in Memory Stack History and Addressing Environment List Stack Cut-Back Operation on Procedure Exit ALGOL Program With Lexicographical Structure Indicated D Registers Indicating Current Addressing Environment Addressing Environment Tree of ALGOL Program Multiple Linked Stacks                                                   |      |

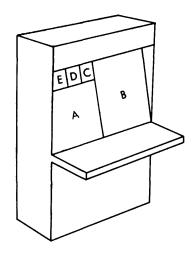

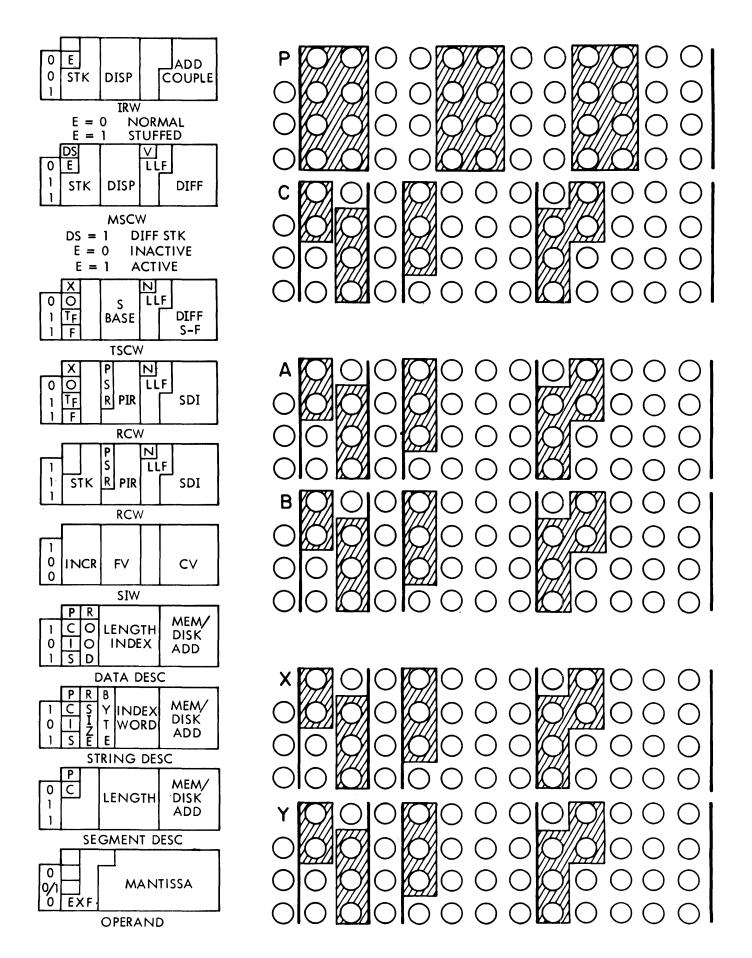

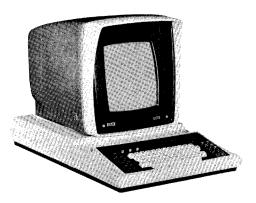

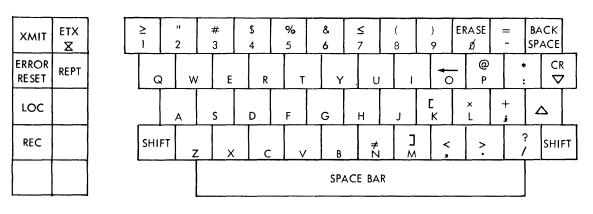

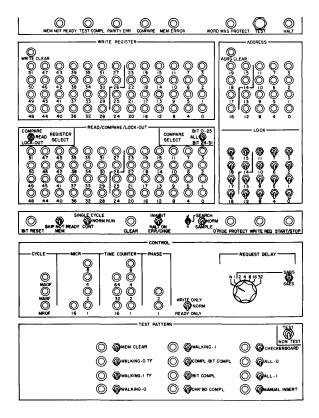

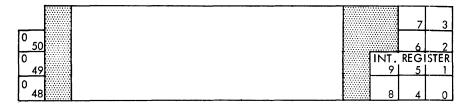

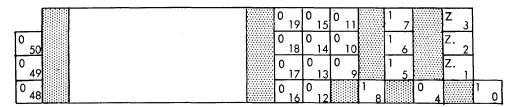

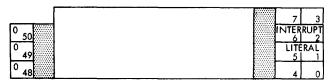

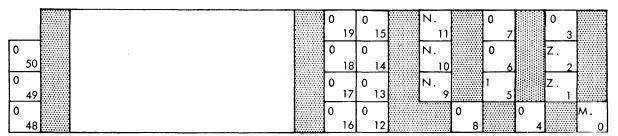

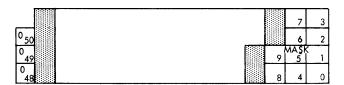

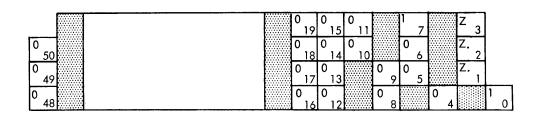

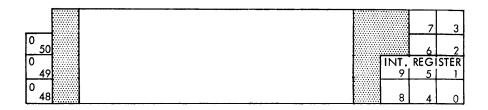

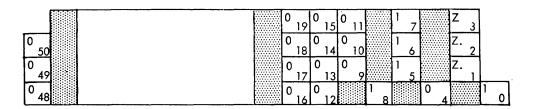

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13 | Processor Display Panels Processor Register Panel A Processor Display Panel B Power Control Address Register Panel E Input/Output Processor Display Panel B Panel D Input/Output Processor Maintenance Control Panel Operators Control Console Visual Message Control Center Keyboard Format Memory Tester Memory Tester Panel                                                                                                          |      |

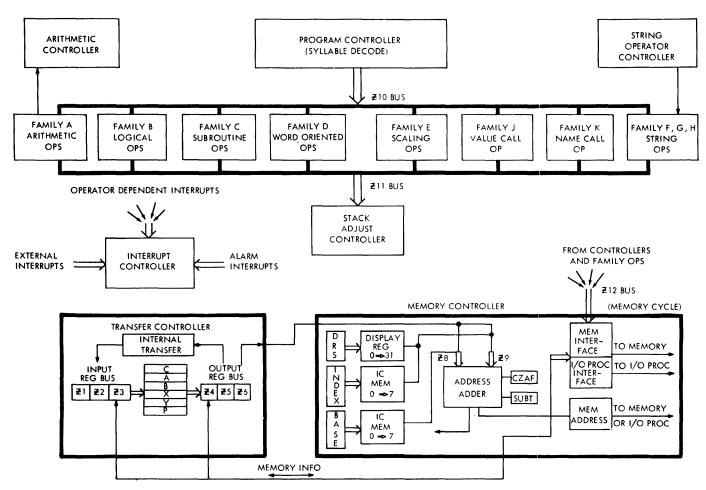

| 5-1<br>5-2                                                                                  | B 6700 Processor Organization                                                                                                                                                                                                                                                                                                                                                                                                           |      |

# LIST OF ILLUSTRATIONS (cont)

| FIGURE      | TITLE                                        | PAGE |

|-------------|----------------------------------------------|------|

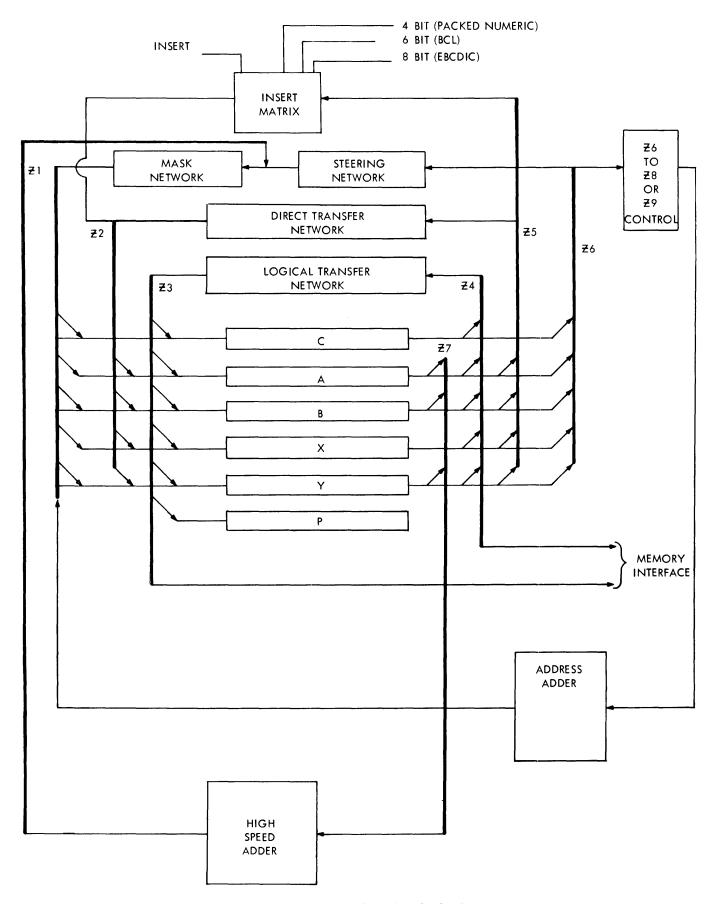

| 5-3         | Internal Data Transfer Section               | 5-4  |

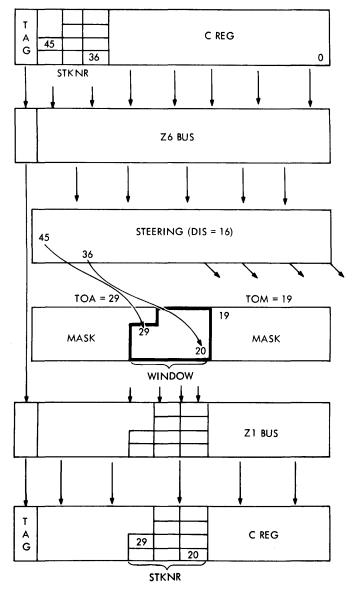

| 5-4         | Mask and Steering                            | 5-5  |

| 5-5         | Arithmetic Control                           |      |

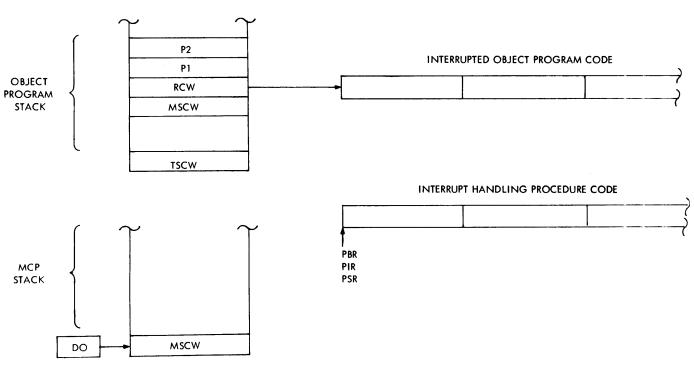

| 5-6         | Presence Bit Interrupt                       | 5-8  |

| 5-7         | B 6700 Scan Bus Priority Control             | 5-11 |

| 5-8         | Stack Format                                 | 5-13 |

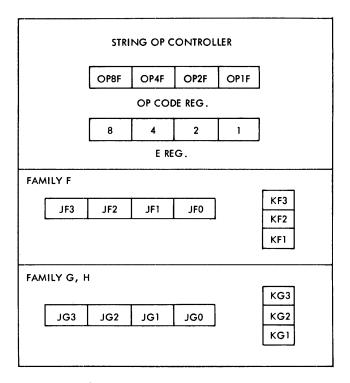

| <b>5-</b> 9 | String Op Controller                         | 5-14 |

| 5-10        | E Register Functions                         | 5-14 |

| 5-11        | Input/Output Processor Block Diagram         | 5-15 |

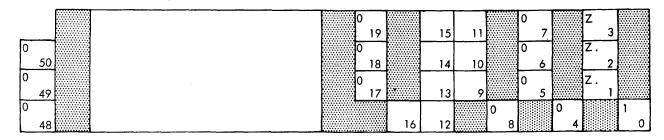

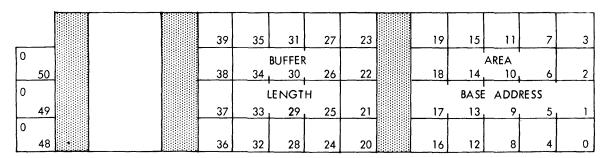

| 5-12        | Command Data Register and Scratch Pad Memory | 5-16 |

| 5-13        | Data Information Flow                        | 5-18 |

| 5-14        | Memory Controller Decoding                   | 5-19 |

| 5-15        | Memory Organization                          | 5-21 |

| 5-16        | Information Transmission                     | 5-21 |

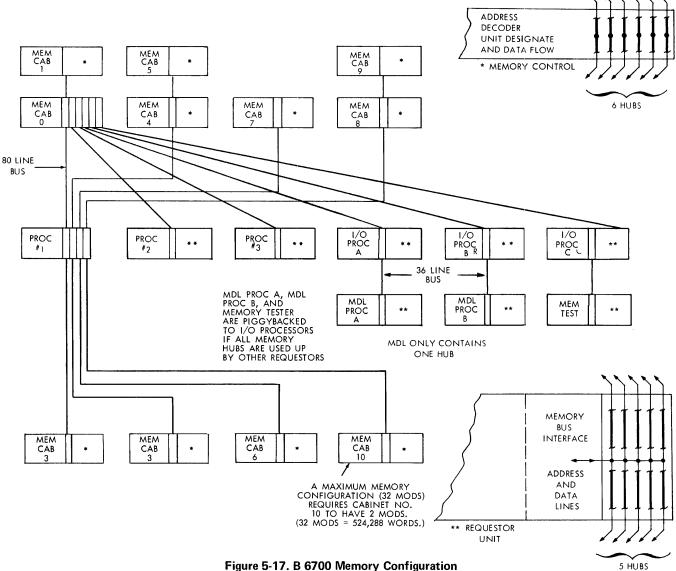

| 5-17        | B 6700 Memory Configuration                  | 5-22 |

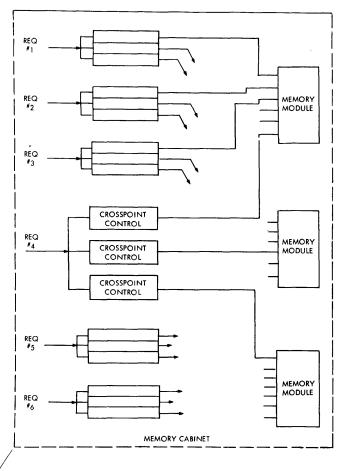

| 5-18        | Memory Module Selection                      | 5-23 |

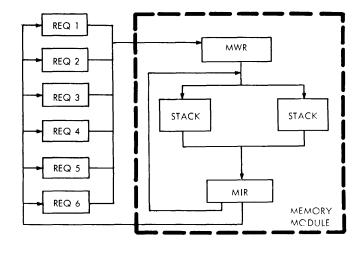

| 5-19        | Memory Registers                             |      |

| 5-20        | Interlace Addressing                         |      |

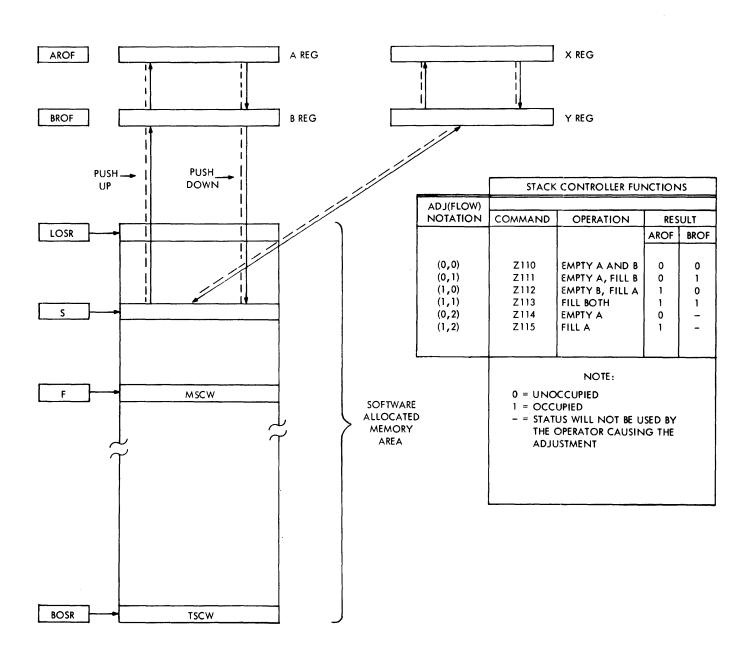

| 5-21        | Hardware Stack Adjustment                    | 5-24 |

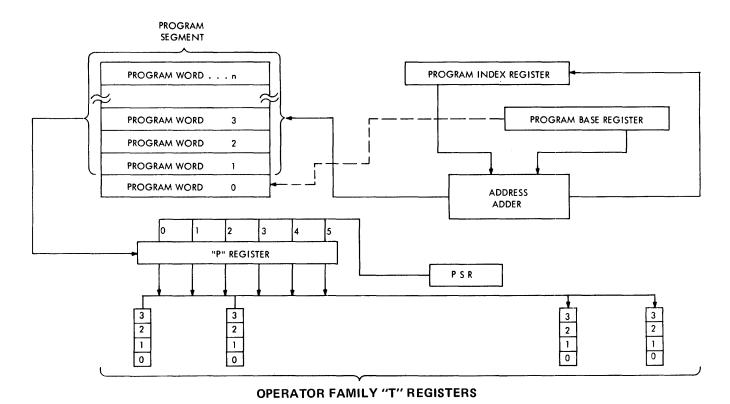

| 6-1         | Program Word                                 | 6-1  |

| 6-2         | Program Word, Syllable Addressing            | 6-2  |

| 6-3         | Syllable Decode Table                        |      |

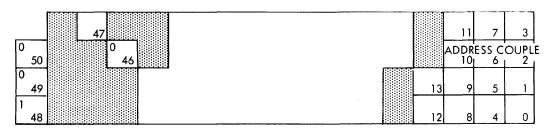

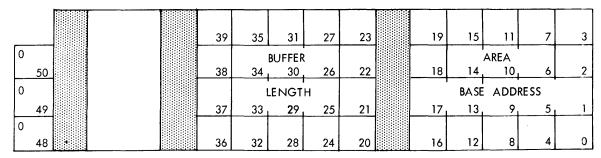

| 6-4         | Word Data Descriptor                         | 6-3  |

| 6-5         | String Descriptor (Non-indexed)              | 6-4  |

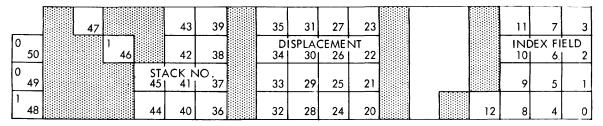

| 6-6         | Byte/Word Index Field                        | 6-4  |

| 6-7         | Segment Descriptor                           | 6-4  |

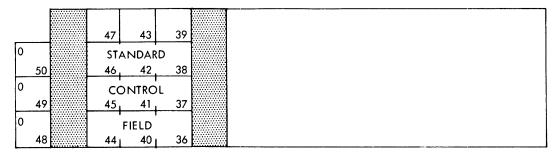

| 6-8         | Mark Stack Control Word                      | 6-5  |

| 6-9         | Program Control Word                         | 6-6  |

| 6-10        | Return Control Word                          | 6-6  |

| 6-11        | Indirect Reference Word                      | 6-7  |

| 6-12        | Stuffed Indirect Reference Word              | 6-7  |

| 6-13        | Program Level Bit Assignment                 | 6-8  |

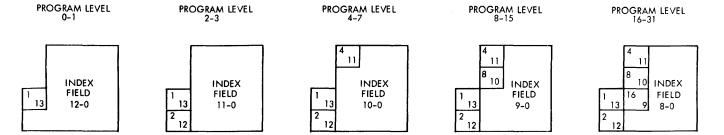

| 6-14        | Step Index Word                              | 6-8  |

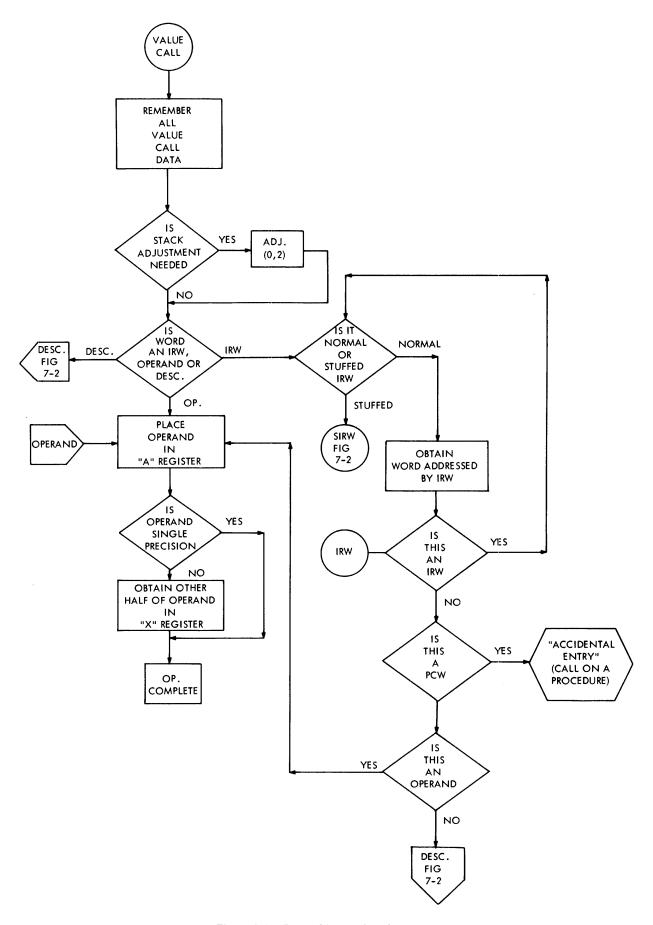

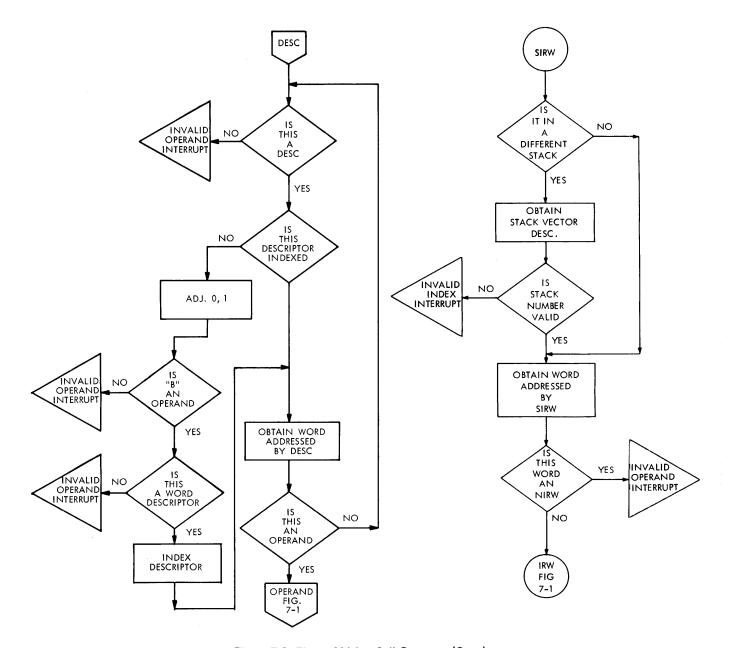

| 7-1         | Flow of Value Call Operator                  |      |

| 7-2         | Flow of Value Call Operator (cont)           | 7-17 |

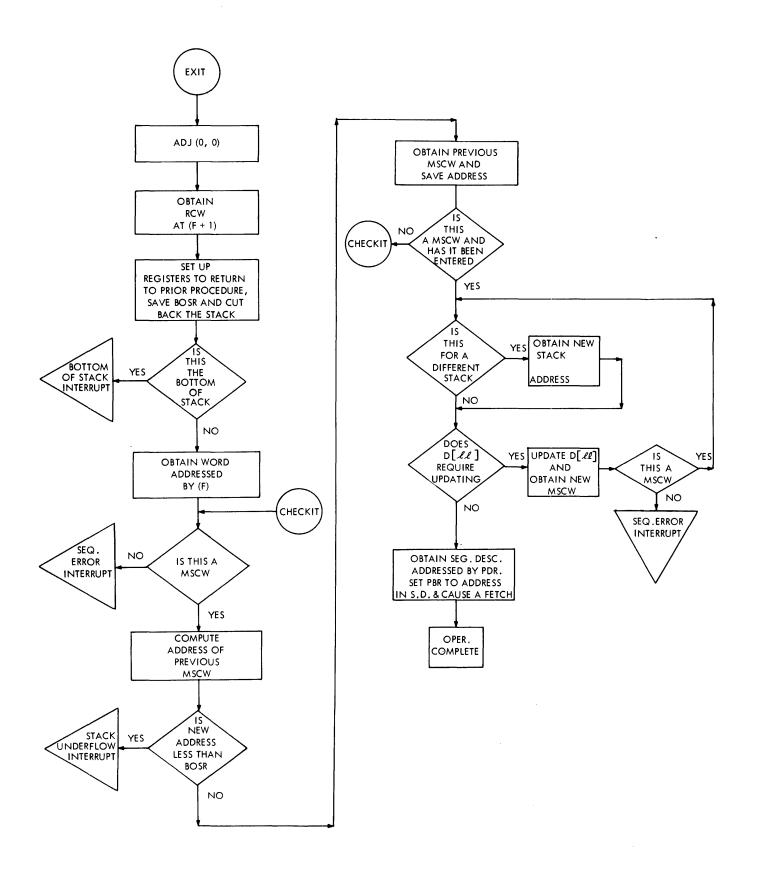

| 7-3         | Flow of Exit Operator                        | 7-18 |

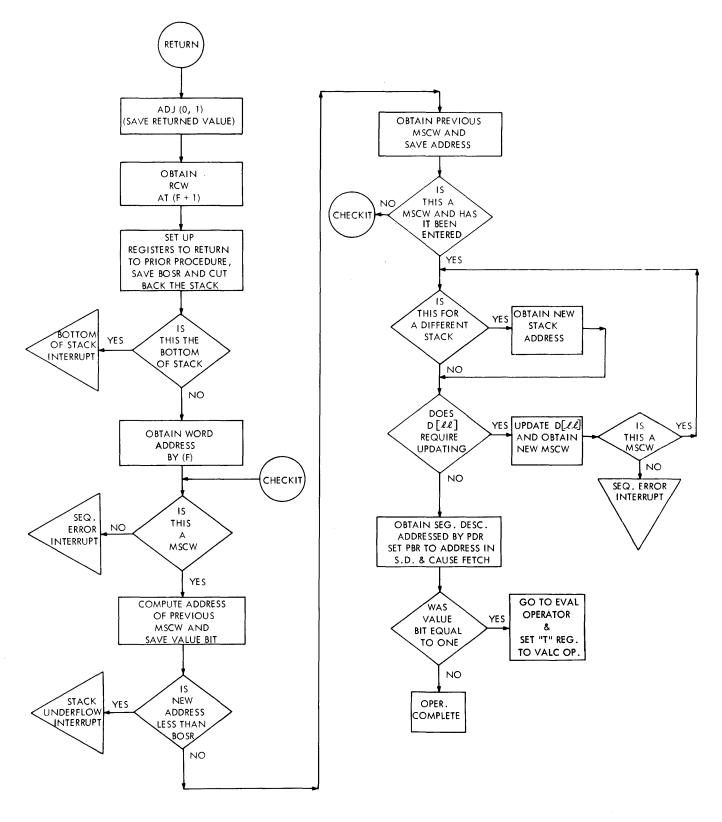

| 7-4         | Flow of Return Operator                      | 7-19 |

| 7-5         | Flow of Enter Operator                       | 7-20 |

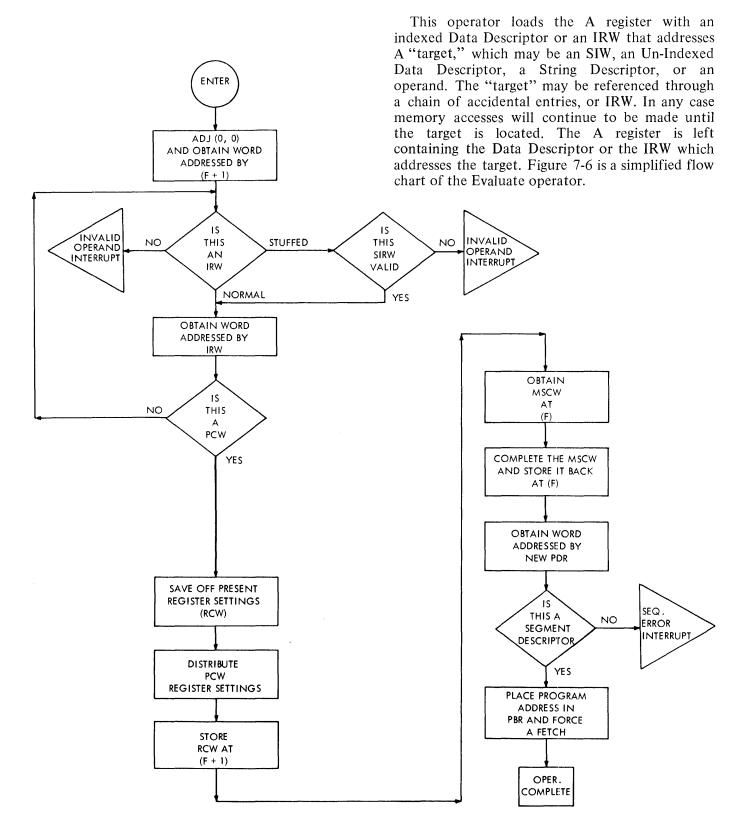

| <b>7-</b> 6 | Flow of Evaluate Operator                    |      |

| 7-7         | Flow of Stuff Environment Operator           | 7-22 |

| 8-1         | Read Time-of-Day Function Word               |      |

| 8-2         | Time-of-Day Word                             |      |

| 8-3         | Read General Control Adapter Function Word   |      |

| 8-4         | Read Result Descriptor Function Word         | 8-3  |

| 8-5         | Result Descriptor                            | 8-3  |

| 8-6         | Read Interrupt Mask Function Word            |      |

| 8-7         | Interrupt Mask Word                          | 8-4  |

# LIST OF ILLUSTRATIONS (cont)

| FIGURE | TITLE                                          | PAGE  |

|--------|------------------------------------------------|-------|

| 8-8    | Read Interrupt Register Function Word          | 8-4   |

| 8-9    | Interrupt Register Word                        | 8-4   |

| 8-10   | Read Interrupt Literal Function Word           | 8-5   |

| 8-11   | Interrupt Literal Word                         | 8-5   |

| 8-12   | Interrogate Peripheral Status Function Word    | 8-5   |

| 8-13   | Status Vector Word                             | 8-6   |

| 8-14   | Interrogate Peripheral Unit Type Function Word |       |

| 8-15   | Unit Type Function Word                        |       |

| 8-16   | Interrogate I/O Path Function Word             |       |

| 8-17   | I/O Path Result Word                           |       |

| 8-18   | Set Time-of-Day Clock Function Word            |       |

| 8-19   | Time-of-Day Word                               |       |

| 8-20   | Set General Control Adapter Function Word      |       |

| 8-21   | Initiate I/O Function Word                     |       |

| 8-22   | Area Descriptor                                |       |

| 8-23   | I/O Control Word                               |       |

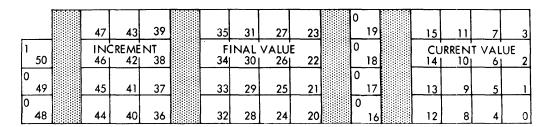

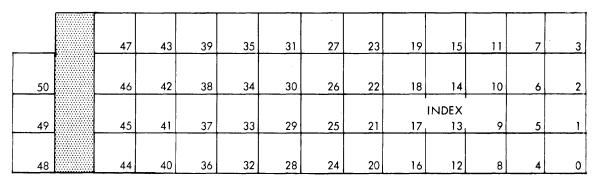

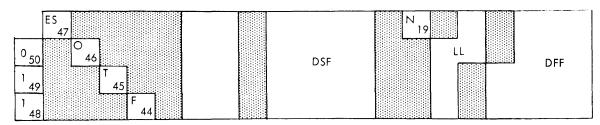

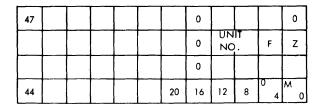

| 8-24   | Index Control Word                             |       |

| 8-25   | Index Word                                     |       |

| 8-26   | Top-Of-Stack Control Word (TSCW)               |       |

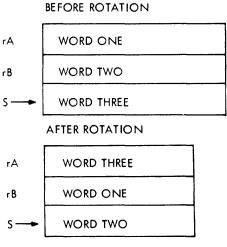

| 8-27   | Stack Rotation Up                              |       |

| 8-28   | Stack Rotation Down                            |       |

| 0-20   | Stack Rotation Down                            | 6-12  |

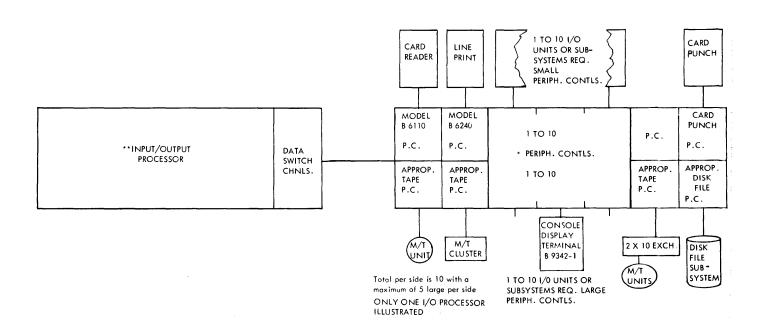

| 10-1   | Input/Output Subsystem                         |       |

| 10-2   | I/O Descriptor Formats                         | 10-2  |

| 10-3   | Result Descriptor Format                       | 10-3  |

| 10-4   | Console Control Center                         | 10-3  |

| 10-5   | Single Line Control Result Descriptor          | 10-4  |

| 10-6   | Single Line Control I/O Control Word           | 10-4  |

| 10-7   | Card Reader                                    |       |

| 10-8   | Card Read I/O Control Word                     |       |

| 10-9   | Card Read Result Descriptor                    |       |

| 10-10  | Card Punch                                     |       |

| 10-11  | Card Punch I/O Control Word                    |       |

| 10-12  | Card Punch Result Descriptor                   |       |

| 10-13  | Line Printer                                   |       |

| 10-14  | Line Printer I/O Control Word                  |       |

| 10-15  | Line Printer Result Descriptor                 |       |

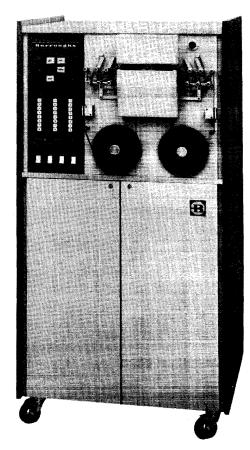

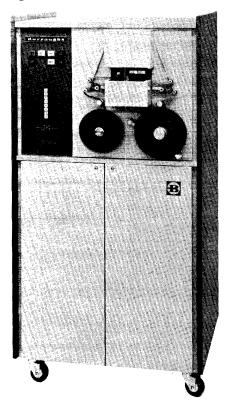

| 10-16  | Free Standing Magnetic Tape Units              |       |

| 10-17  | Cluster Tape Unit                              |       |

| 10-18  | Magnetic Tape Configuration                    |       |

| 10-19  | I/O Control Word Magnetic Tape                 |       |

| 10-20  | Magnetic Tape Result Descriptor                |       |

| 10-21  | Basic Disk File Subsystem                      |       |

| 10-22  | Disk File Configurations                       |       |

| 10-23  | Disk File I/O Control Word                     |       |

| 10-24  | Disk File Result Descriptor                    |       |

| 10-25  | B 9120 Paper Tape Reader                       |       |

| 10-26  | B 9220 Paper Tape Punch                        |       |

| 10-27  | Paper Tape I/O Control Word and Operations     |       |

| 10-28  | Paper Tape Result Descriptor                   | 10-15 |

## LIST OF ILLUSTRATIONS (cont)

| FIGURE                                       | TITLE                                                                                                                                                                                          | PAGE                         |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

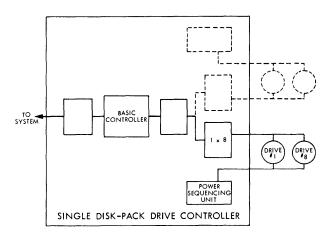

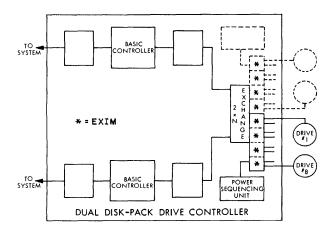

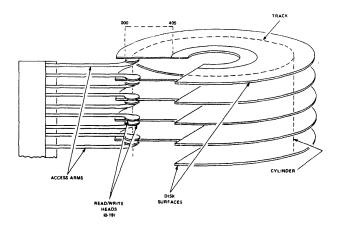

| 10-29<br>10-30<br>10-31<br>10-32<br>10-33    | Disk-Pack Drive and Disk-Pack Drive Controller Disk-Pack Subsystem Block Diagram Disk-Pack Recording Surfaces Disk-Pack I/O Control Word (IOCW) Disk-Pack Result Descriptor Format             | 10-16<br>10-16<br>10-18      |

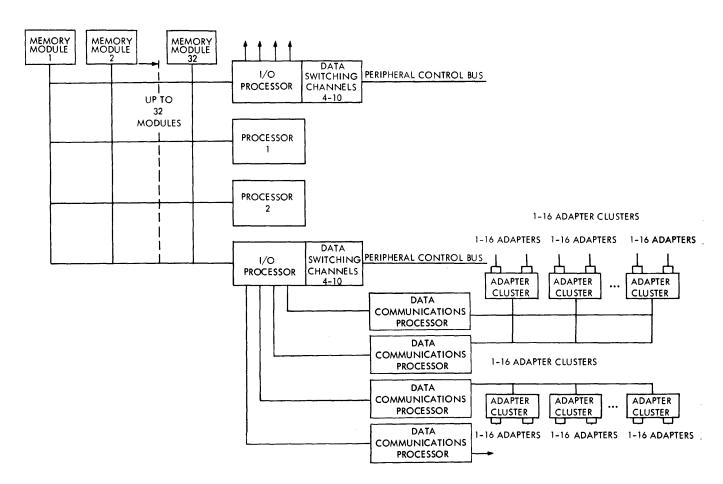

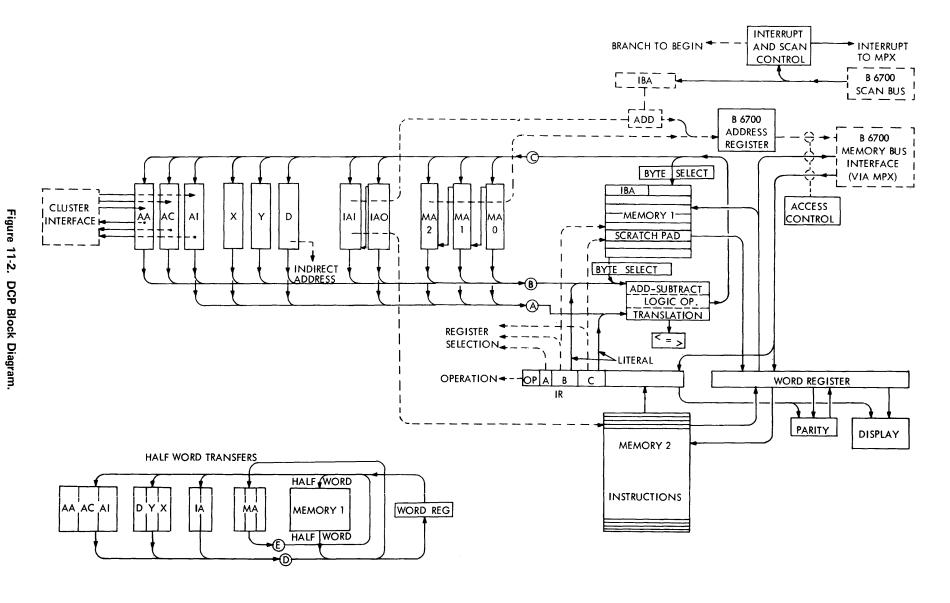

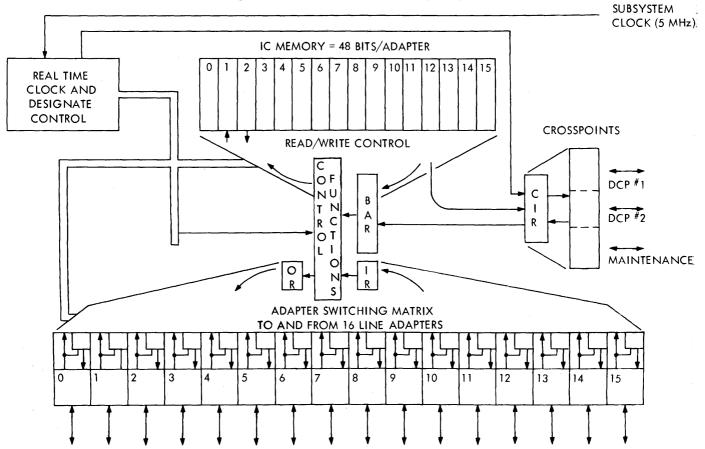

| 11-1<br>11-2<br>11-3                         | B 6700 System Configuration Including Data Communications                                                                                                                                      | 11-2                         |

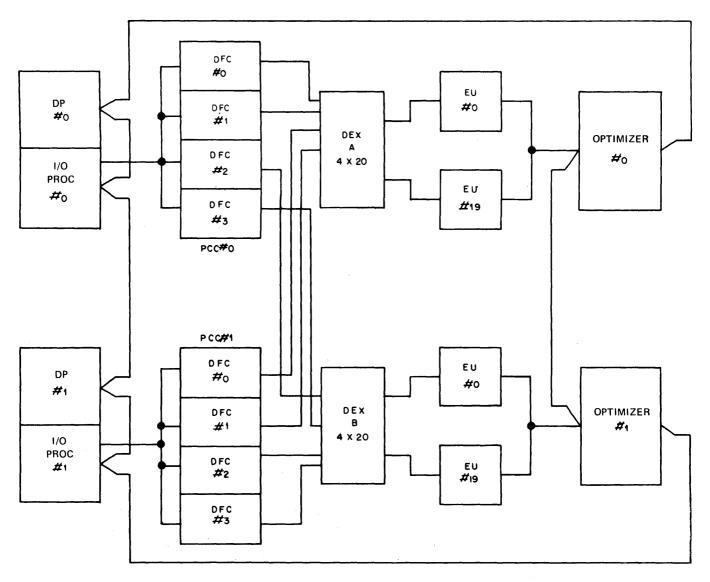

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6 | The Optimizer in the B 6700 System Optimizer Interface Scan-Out Signal Sequence Scan-In Signal Sequence The Disk File Subsystem (DFS) Interface Optimizer Block Diagram with Interface Signals | 12-2<br>12-4<br>12-5<br>12-9 |

|                                              | LIST OF TABLES                                                                                                                                                                                 |                              |

| TABLE                                        | TITLE                                                                                                                                                                                          | PAGE                         |

| 1-1                                          | B 6700 Central Units Chart                                                                                                                                                                     | 1.1                          |

| 2-1                                          | Negative Sign Configurations                                                                                                                                                                   |                              |

| 3-1                                          | Evaluation of Polish String A 7 B C + x :=                                                                                                                                                     |                              |

| 3-2                                          | Description of Stack Operation                                                                                                                                                                 |                              |

| 6-1                                          | Sub-Field Lengths                                                                                                                                                                              |                              |

| 10-1                                         | F Field Codes                                                                                                                                                                                  |                              |

| 10-2                                         | Peripherals and Controls                                                                                                                                                                       |                              |

| 10-3                                         | Available Magnetic Tape Subsystems                                                                                                                                                             | 10-7                         |

| 10-4                                         | Magnetic Tape Operations                                                                                                                                                                       | 10-10                        |

| 10-5                                         | Disk File Memory System Types                                                                                                                                                                  | 10-13                        |

| 10-6                                         | Disk-Pack Subsystem Characteristics                                                                                                                                                            | 10-17                        |

| 11-1                                         | Data Communications Terminal Compatibility                                                                                                                                                     | 11-4                         |

# INTRODUCTION

The Burroughs B 6700 is a medium to large, high-speed Information Processing System. The following are some of the features incorporated in this system:

- 1. Monolythic Circuitry.

- 2. Memory expandable to 1,048,576 words.

- 3. Memory Cycle Times of 1.2 microseconds, 1.5 microseconds, and 500 nanoseconds.

- 4. Peripheral configuration expandable to 256 units.

- 5. Triple Input/Output Processor system permitting up to 36 simultaneous Input/Output (I/O) operations.

- 6. Data Communication Software for remote computing and file manipulation.

- 7. Disk File storage over 36 billion bytes (8-bit characters).

A unique hardware design, developed from years of successful experience with the B 5000 series, has resulted in the parallel design of the B 6700 hardware and software. Whereas hardware traditionally was designed prior to software development, parallel design assures that the hardware contains all necessary logic for efficient software packages, which in turn optimizes hardware capabilities. The B 6700 design affords a general "re-entrant" technique which permits multiple users to share a common object program. In addition, the systems further expand the use of hardware stack organization used in the B 5500. For example, the Segment Dictionary, a separate table for each program in the B 5500, has been placed in the base of the program stack in the B

6700. This part of the stack is used for multiple executions of the same program, thus implementing in the hardware many of the bookkeeping functions required to implement Master Control Program (MCP) re-entrancy.

To provide dynamic storage allocation, the B 6700 system employs and expands upon the Burroughs descriptor method of segmentation, first used on the B 5500, in lieu of some form of fixed-sized "paging" technique.

Designed to bring the user simplified programing, operational ease, and complete freedom of system expansion, the B 6700 offers a choice of problem-oriented languages, some of these languages are: COBOL for business applications and ALGOL and FORTRAN for solution of mathematical problems. Operator intervention is minimized by the MCP, which provides for complete system management.

The complete flexibility of programing and control of the processing pattern provides the B 6700 with smooth growth potential. Starting with a minimum configuration, the user may expand his system in small increments to accommodate a growing work-load. With each addition, the MCP automatically adjusts to attain increased system production and efficiency, expanding system multiprograming capabilities.

This reference manual describes the hardware characteristics of the B 6700 system. Because of the design concept of the B 6700, there exists a strong interdependence between the hardware and the Master Control Program (MCP). This material pertains only to the hardware considerations, whereas the MCP is discussed in a separate manual.

# SYSTEMS DESCRIPTION

#### **GENERAL**