PCP-125A

# REFERENCE MANUAL

\*Registered Trademark of General Electric Company

# REFERENCE MANUAL

General Electric reserves the right to make changes in the equipment (or software) and its characteristics (or functions) at any time without notice.

### TABLE OF CONTENTS

| CHAPTER 1 | SYSTE | EM ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1.1   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | 1.2   | SCOPE OF MANUAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

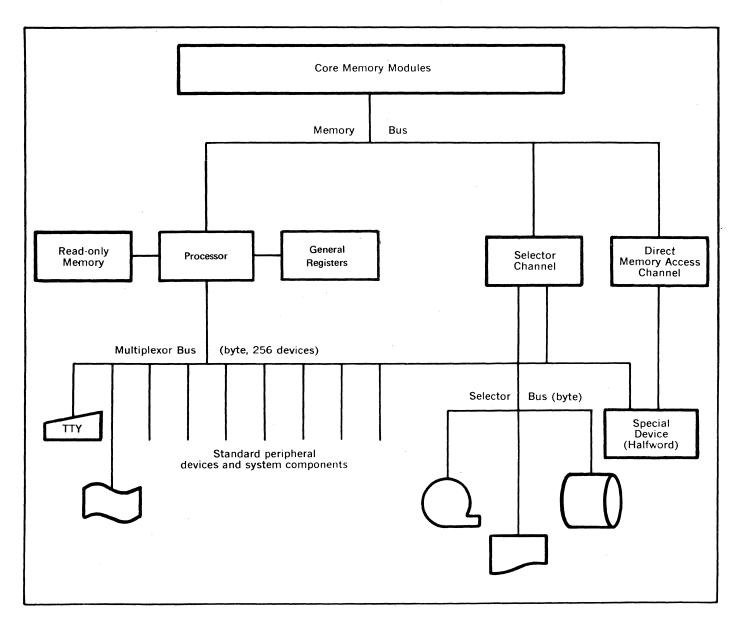

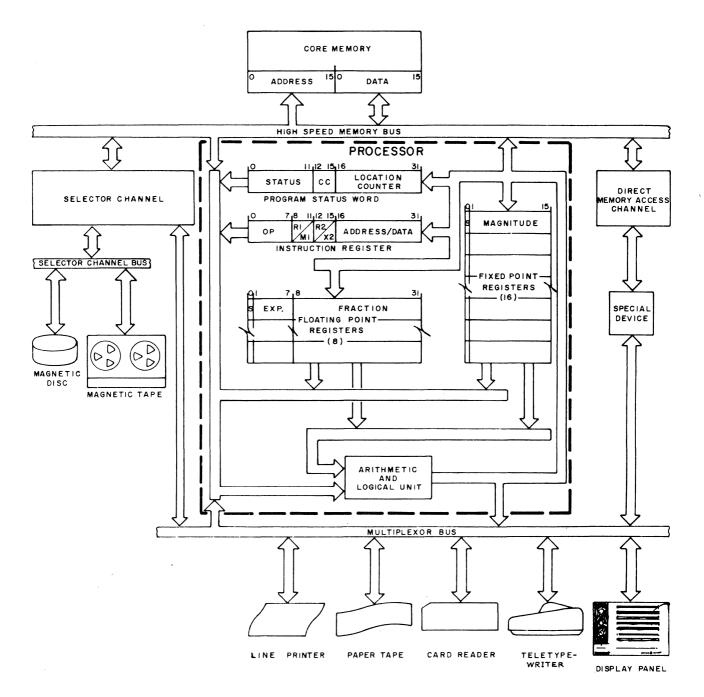

|           | 1.3   | PROCESSOR ORGANIZATION. $\ldots \ldots 1^{-2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           |       | 1.3.1 General Registers $\ldots$ $1-2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           |       | 1.3.2 Arithmetic/Logical Unit. $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |       | 1.3.3 Control Unit $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |       | 1.3.4 Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

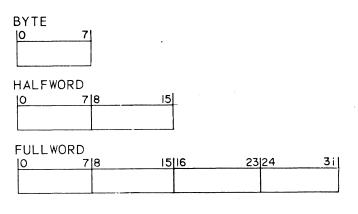

|           | 1.4   | STORAGE WORD FORMATS $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |       | 1.4.1 Hexadecimal Notation $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

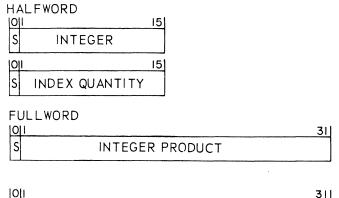

|           |       | 1.4.2 Arithmetic Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |       | 1.4.3 Logical Data $\ldots$ 1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |       | 1.4.4 Information Positioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           | 1.5   | INSTRUCTION WORD FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           | 1.6   | GENERAL REGISTERS AND STORAGE ADDRESSING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           | 1.0   | 1.6.1       General Registers       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1       1.6.1                                                                                                                                                                 |

|           |       | 1.6.2         Storage Addressing         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2         1.6.2 |

|           |       | 1.6.3       Address Modification By Indexing       1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | 1.7   | PROGRAM STATUS WORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | 1. (  | 1.7.1 Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

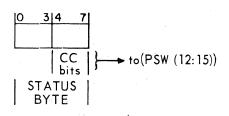

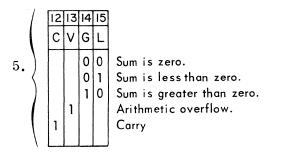

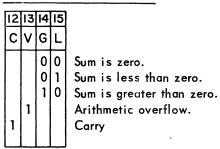

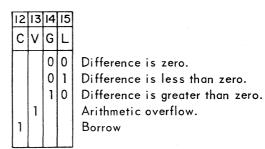

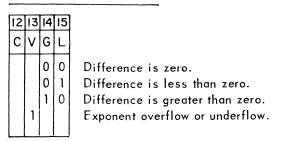

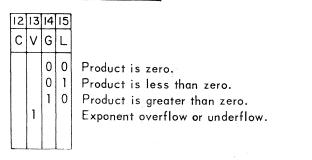

|           |       | 1.7.2 Condition Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |       | 1.7.3         Instruction Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |       | 1.7.4       Instruction Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | 1.8   | INTERRUPT SYSTEM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | 1.0   | 1.8.1         Interrupt Procedure         1.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |       | 1.8.2 Acknowledgement of External Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           |       | 1.8.3       Interrupts       1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |       | 1.8.4         Power Failure         1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

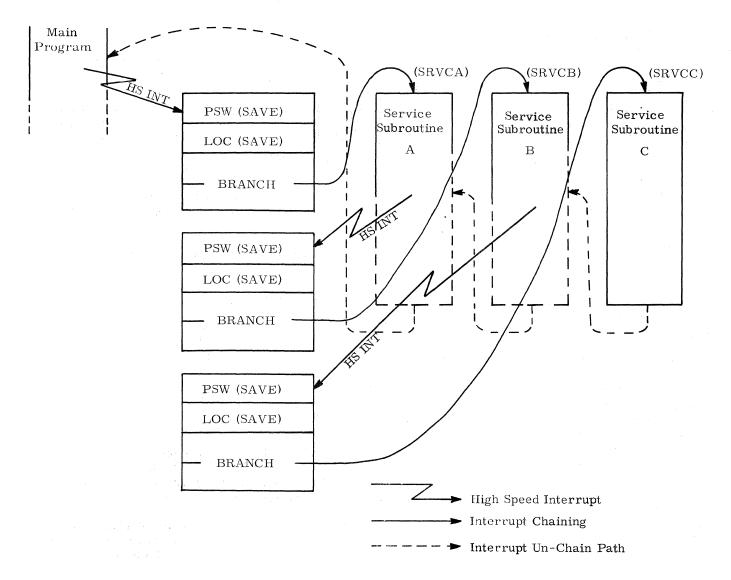

|           |       | 1.8.5         High Speed Interrupt Option         1.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | 1 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1.9   | INPUT/OUTPUT SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |       | 1.9.1       Basic Input/Output Programming       1-15         1.9.2       Program Controlled Input/Output       1-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |       | 1.9.3 Interrupt Controlled Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           |       | 1.9.4 Block Input/Output Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

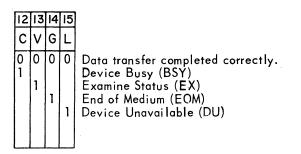

|           |       | 1.9.5 Condition Code for Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |       | 1.9.6 Direct Memory Access Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | 1 10  | 1.9.7 Selector Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | 1.10  | REGISTER SAVE POINTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | 1.11  | CORE MEMORY ALLOCATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CHAPTER 2 | INSTR | CUCTION REPERTOIRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | 2.1   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | 2.2   | LOAD AND STORE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |       | 2.2.1 Load Halfword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |       | 2.2.2 Store Halfword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |       | 2.2.3 Load Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |       | 2.2.4 Store Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |       | 2.2.5 Load Multiple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |       | 2.2.6         Store Multiple         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6         2.2.6                                                                                      |

|           |       | 2.2.7         Floating-Point Load         2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           |       | 2.2.8         Floating-Point Store           2.2.8         Floating-Point Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |       | 2.2.9         Load Program Status Word         2.7.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |       | 2.2.10 Autoload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 2.3   | FIXED POINT ARITHMETIC INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | 4.0   | 2.3.1 Add Halfword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

i

## TABLE OF CONTENTS (Continued)

|           |         | 2.3.2       Add With Carry Halfword                                                                           |

|-----------|---------|---------------------------------------------------------------------------------------------------------------|

|           |         | 2.3.4         Subtract with Carry nanword         2.10           2.3.5         Multiply Halfword         2-11 |

|           | 2 4     | 2.3.6 Divide Halfword                                                                                         |

|           | 2.4     | FLOATING -POINT ARITHMETIC INSTRUCTIONS2-122.4.1Floating-Point Add2-12                                        |

|           |         | 2.4.1         Floating Four Rule         2.12           2.4.2         Floating-Point Subtract         2-13    |

|           |         | 2.4.3 Floating-Point Multiply                                                                                 |

|           |         | 2.4.4 Floating-Point Divide                                                                                   |

|           | 2.5     | LOGICAL INSTRUCTIONS                                                                                          |

|           |         | 2.5.1       AND Halfword       2-15         2.5.2       OR Halfword       2-16                                |

|           |         | 2.5.2       OR Halfword       2-16         2.5.3       Exclusive OR Halfword       2-16                       |

|           |         | 2.5.4       Compare Logical Halfword       2-17                                                               |

|           |         | 2.5.5         Floating-Point Compare         2-17                                                             |

|           | 2.6     | SHIFT INSTRUCTIONS                                                                                            |

|           |         | 2.6.1 Shift Left Halfword Arithmetic 2-19                                                                     |

|           |         | 2.6.2 Shift Right Halfword Arithmetic                                                                         |

|           |         | 2.6.3 Shift Left Halfword Logical                                                                             |

|           | 2.7     | 2.6.4Shift Right Halfword Logical $2-20$ BRANCH INSTRUCTIONS $2-21$                                           |

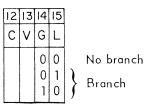

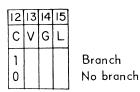

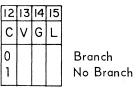

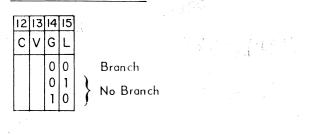

|           | 2.1     | 2.7.1         Branch on True Condition         2-21                                                           |

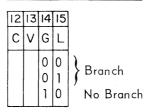

|           |         | 2.7.2 Branch on False Condition                                                                               |

|           |         | 2.7.3 Branch Unconditional                                                                                    |

|           |         | 2.7.4 No Operation                                                                                            |

|           |         | 2.7.5 Branch On Index IIigh                                                                                   |

|           |         | 2.7.6       Branch On Index Low or Equal.       2-24         2.7.7       Branch And Link.       2-25          |

|           | 2.8     | 2.7.7 Branch And Link                                                                                         |

|           | 4.0 , , | ON CONDITION                                                                                                  |

| •         |         | 2.8.1 Branch on Zero                                                                                          |

|           |         | 2.8.2 Branch On Not Zero                                                                                      |

|           |         | 2.8.3 Branch On Plus                                                                                          |

|           |         | 2.8.4 Branch On Not Plus                                                                                      |

|           |         | 2.8.5       Branch On Minus.       2-29         2.8.6       Branch On Not Minus       2-29                    |

|           |         | 2.8.7       Branch On Carry.       2-30                                                                       |

|           |         | 2.8.8         Branch On Overflow         2-30                                                                 |

|           |         | 2.8.9 Branch On Low                                                                                           |

|           |         | 2.8.10 Branch On Not Low 2-31                                                                                 |

|           |         | 2.8.11 Branch On Equal                                                                                        |

|           | 9       | 2.8.12 Branch On Not Equal                                                                                    |

|           | 2.9     | DEVICE INTERRUPT AND CONTROL INSTRUCTIONS                                                                     |