# MAINTENANCE MANUAL

**VOLUME 1**

# MAINTENANCE MANUAL

**VOLUME 1**

30-1 GE 29-026R01 30-2 GE 29-034R01

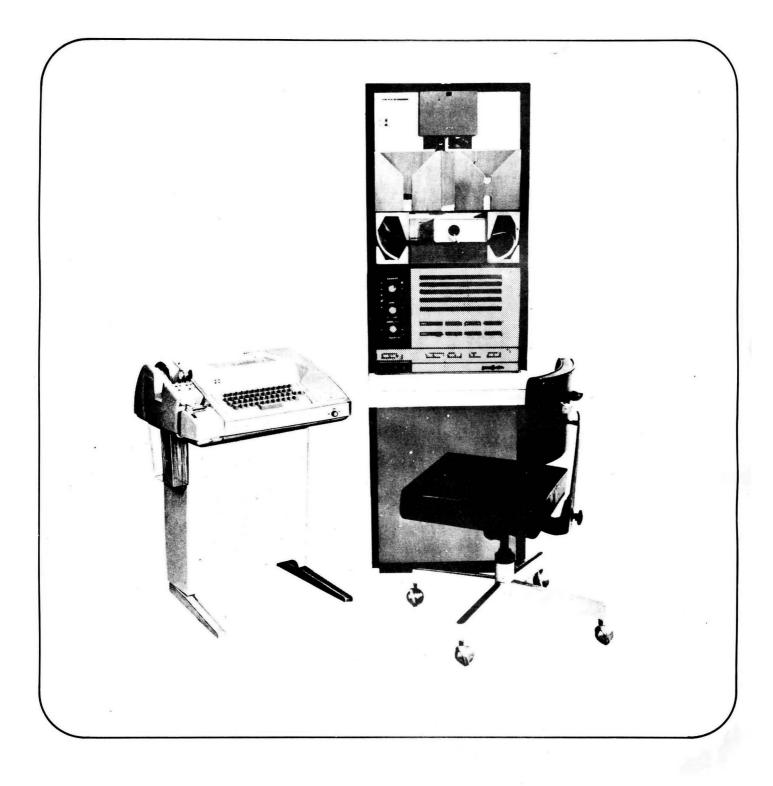

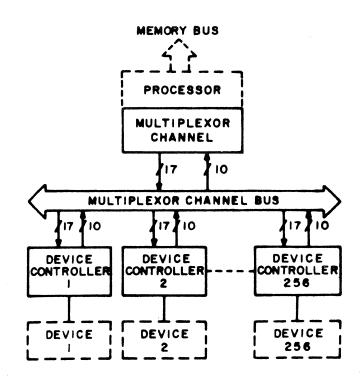

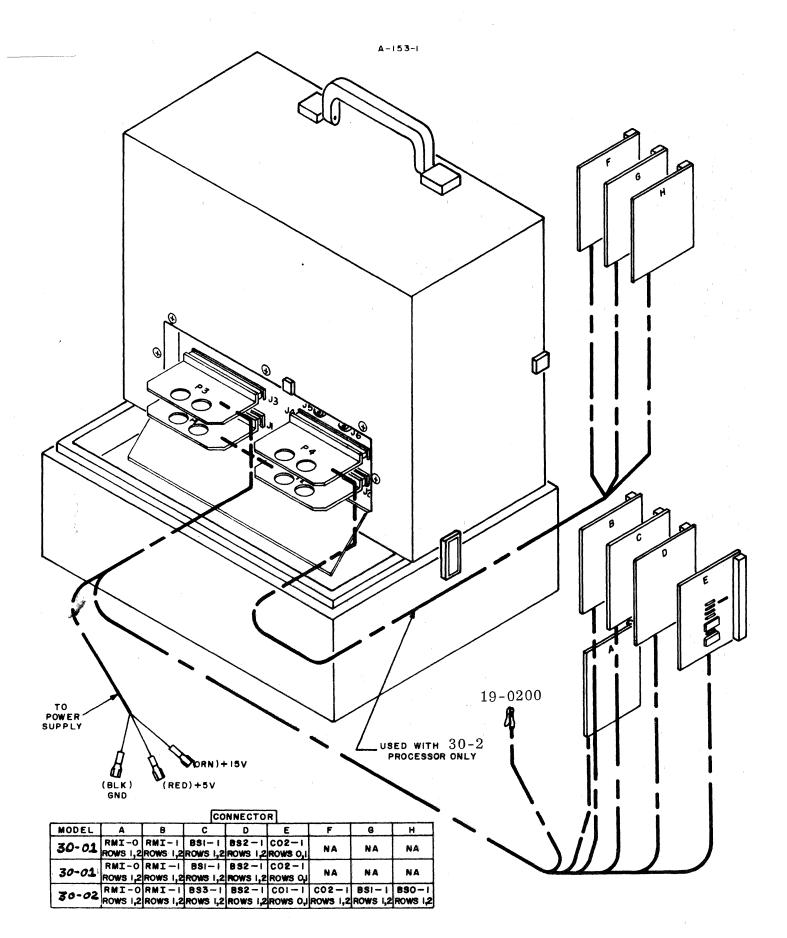

Figure 1-1. Typical GE-PAC 30 Digital System

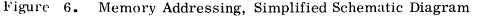

# GENERAL DESCRIPTION

# CONTENTS

| 1. | INTRODUCTION.                                                                                          | •••• | 1 |

|----|--------------------------------------------------------------------------------------------------------|------|---|

| 2. | SCOPE OF MANUAL                                                                                        |      | 1 |

| 3. | SYSTEM ORGANIZATION                                                                                    |      | 1 |

|    | <ul> <li>3.1 Physical Organization</li></ul>                                                           |      |   |

| 4. | DOCUMENTATION                                                                                          |      | 9 |

|    | <ul> <li>4.1 Number Notation</li> <li>4.2 Part Numbering System</li> <li>4.3 Drawing System</li> </ul> |      | 9 |

# ILLUSTRATIONS

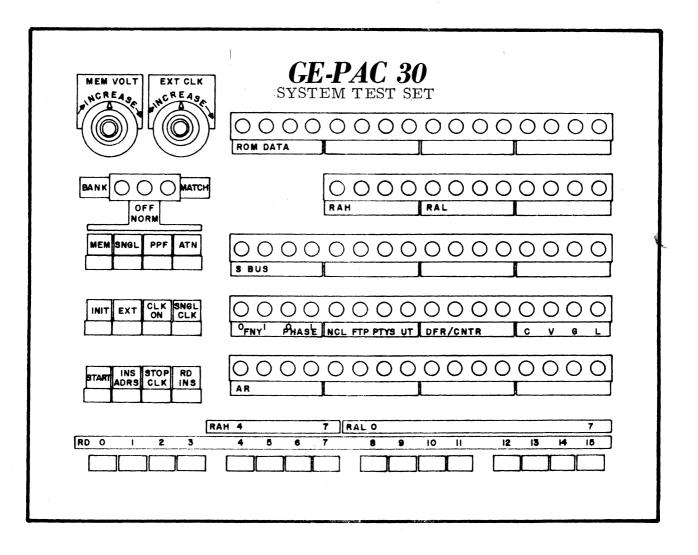

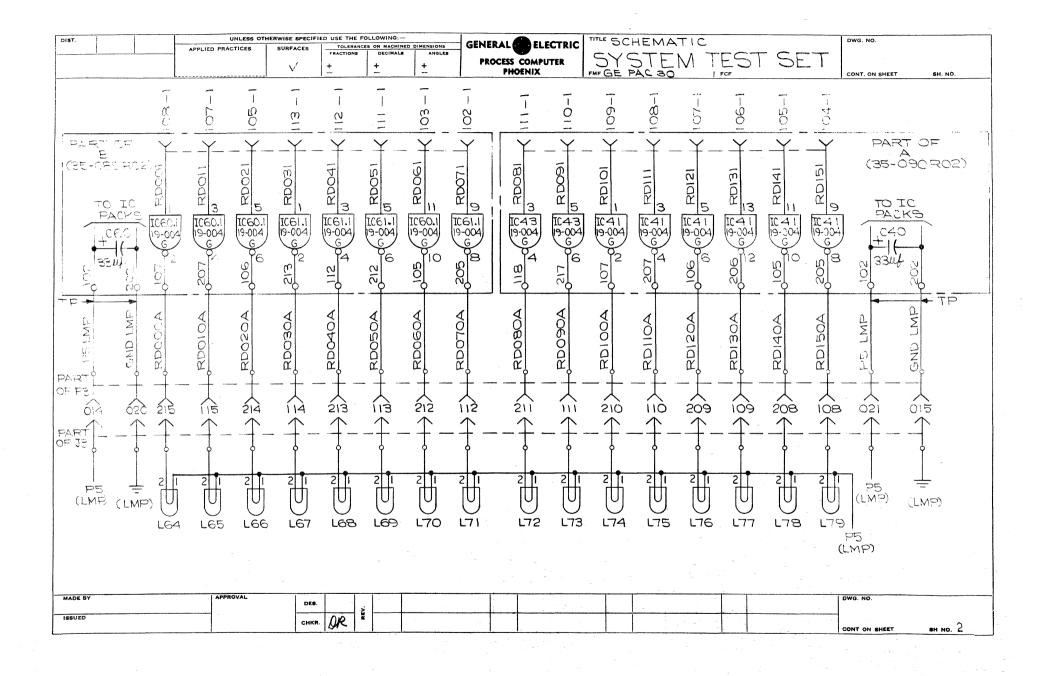

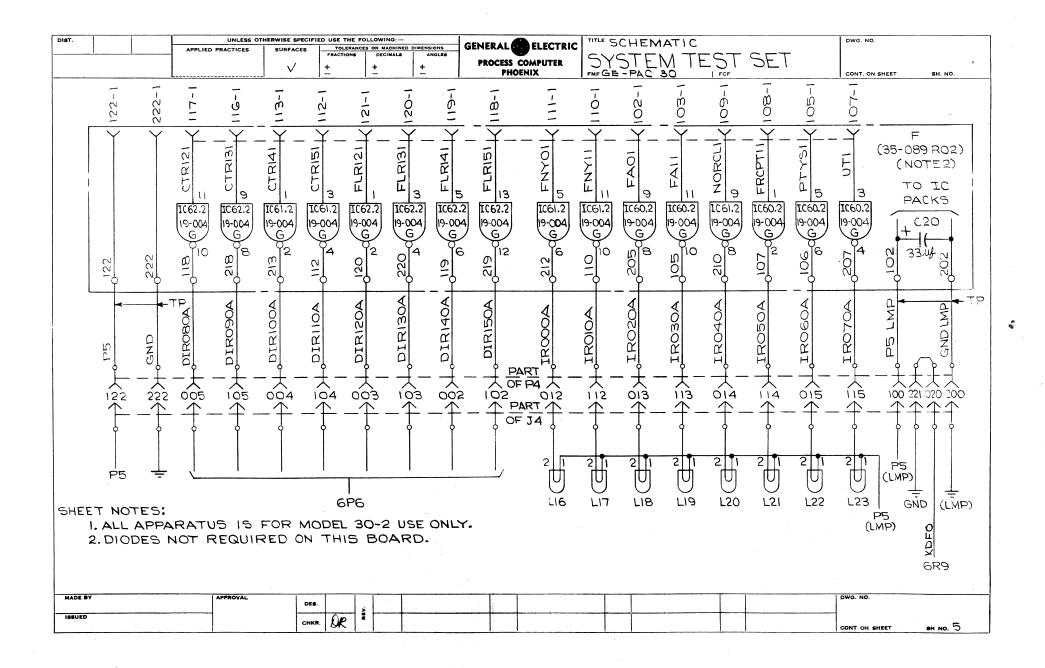

| 1.  | Typical GE-PAC 30 Digital Systemii                        |

|-----|-----------------------------------------------------------|

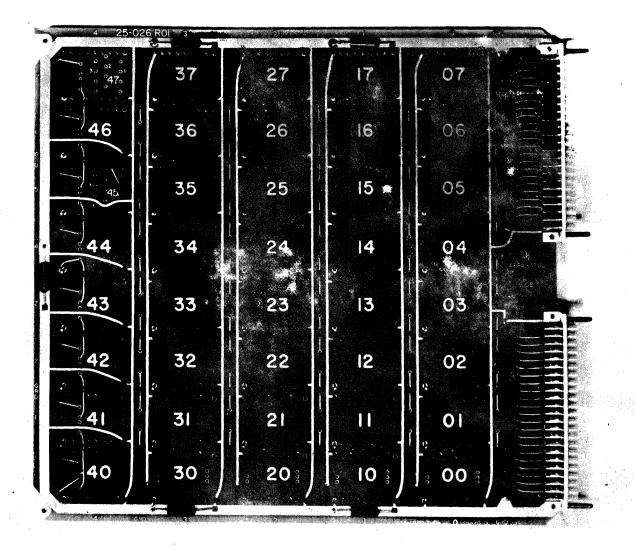

| 2.  | Mother-Board Layout 3                                     |

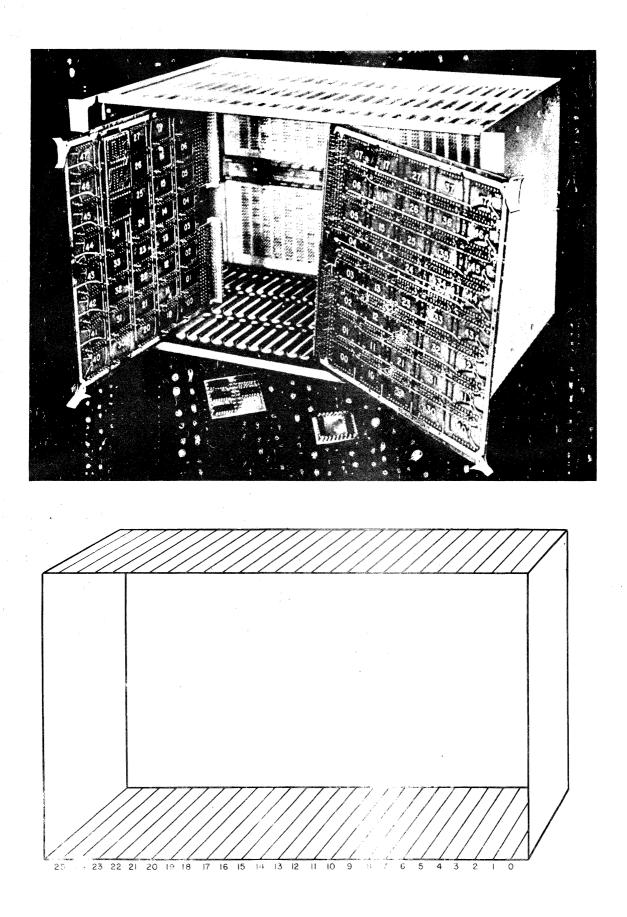

| 3.  | Typical GE-PAC 30 Rack, Three-Quarter Front View 4        |

| 4.  | Daughter-Board Layout 5                                   |

| 5.  | Typical GE-PAC 30 Rack, Back Panel Layout 6               |

| 6.  | Mother-Board Connector Layout 7                           |

| 7.  | Typical GE-PAC 30 Rack, Interface Cable Layout            |

| 8.  | GE-PAC 30 Digital System Basic Block Diagram 8            |

| 9.  | Part Number Format10                                      |

| 10. | Three-Input NAND Gate Symbol, Wire Wrap Mother-Board14    |

| 11. | Power Gate Symbol, Copper Mother-Board14                  |

| 12. | Typical Copper Mother-Board, Component Location Diagram15 |

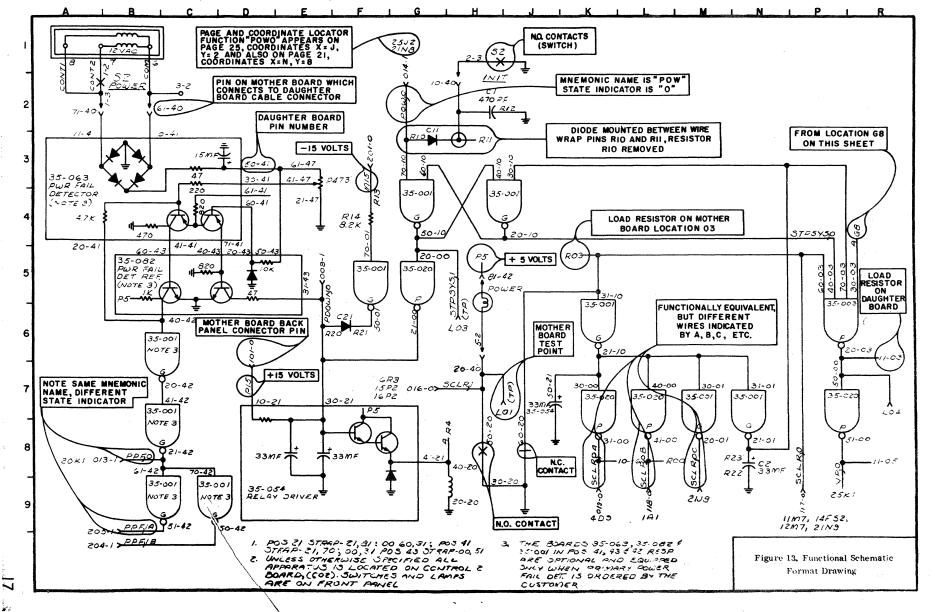

| 13. | Functional Schematic Format Drawing17                     |

ř

#### 1. INTRODUCTION

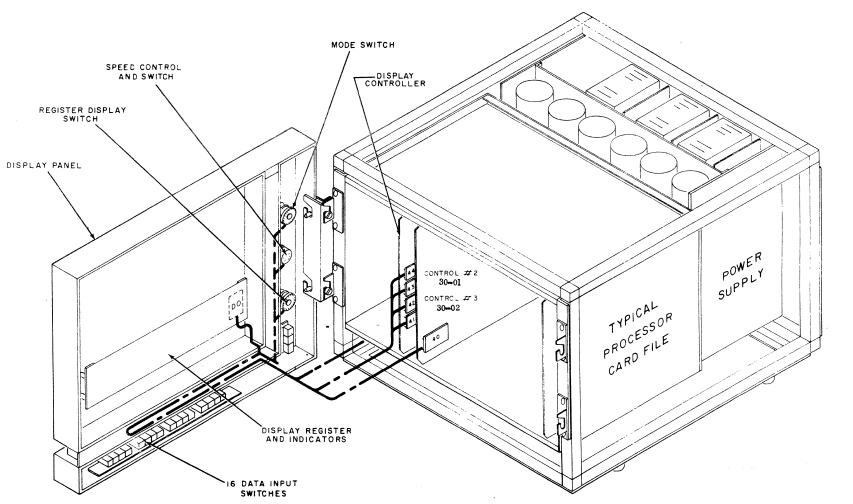

Figure 1 shows a typical GE-PAC\* 30 Digital System. The GE-PAC 30 is a general purpose, low cost system, versatile enough to perform a wide range of both industrial control and scientific computation. These third generation systems use integrated circuits for reliability, and feature a modular expansion system which permits an economical approach to the specific requirements of each installation.

A high speed, 16-bit halfword memory is addressable and alterable to the 8-bit byte level. Memory is field expandable to 65,536 bytes. All memory is directly addressable with the primary instruction word, no paging or indirect addressing is required.

Sixteen General Registers, each 16-bits long, can be used as Index Registers or accumulators.

Register-to-register instructions permit operations between the 16 General Registers, eliminating redundant loads and stores.

A comprehensive instruction set includes efficient byte processing instructions, single instructions for loop control to increment-test-branch on index values, as well as instructions that test the condition code and branch directly to any location in memory.

Logical and arithmetic shift instructions can shift up to 15 positions with a single instructions.

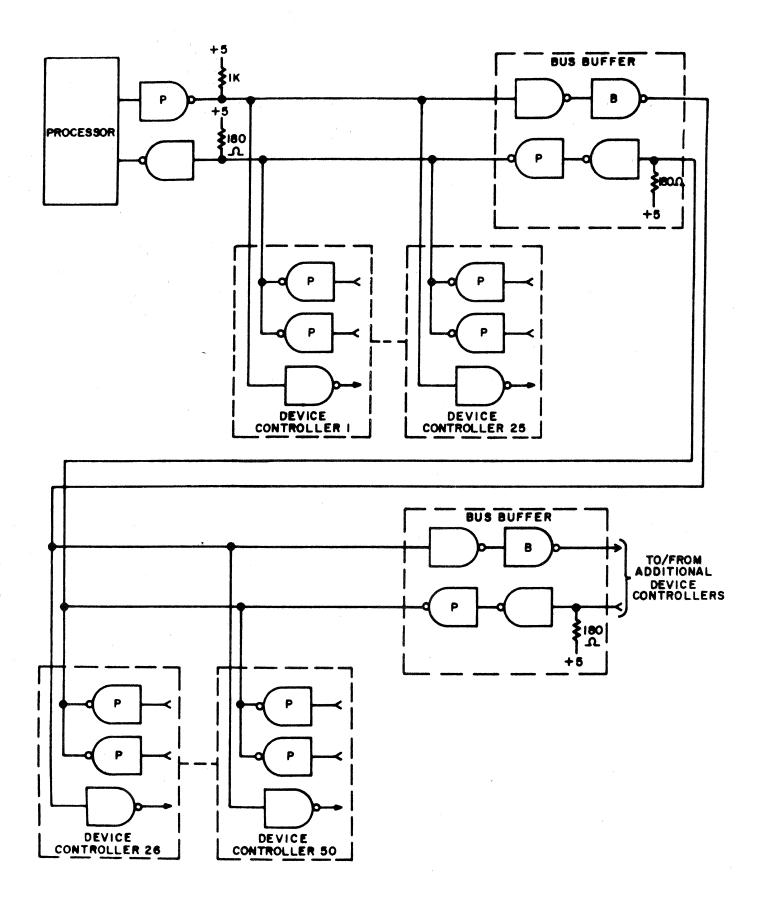

Flexible, multiplexed input/output systems include an integrated priority interrupt facility and provide for direct addressing of up to 256 devices.

High speed memory access channels permit cycle stealing input/output to byte oriented peripherals or 16-bit halfword special purpose devices.

#### 2. SCOPE OF MANUAL

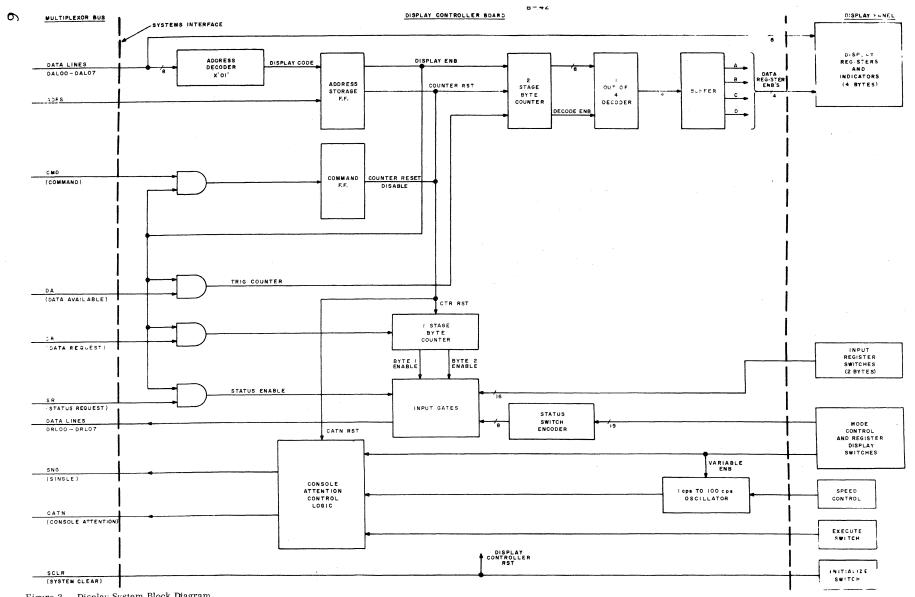

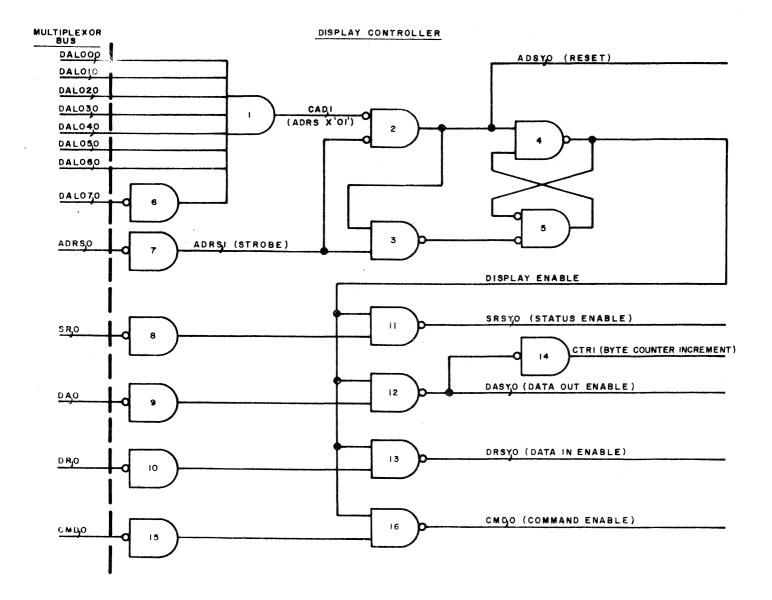

This two volume maintenance manual is planned to enable an experienced digital technician to learn the theory of operation and maintenance of the GE-PAC 30 Digital System. This Volume, Volume 1, provides the theory and maintenance text. Volume 2 provides installation data and drawings. This Section of this Volume provides an introduction to both the system and to the documentation. The second Section describes the Processor. The Display System, including operating information is decribed next. The fourth Section describes the Input/Output (I/O) system. The core memory is described next. The Read-Only-Memory (ROM) is described next, followed by the Power System. General References are provided in the last Section.

Other GE-PAC 30 publications which may be of interest to readers of this manual are listed in Table 1.

#### 3. SYSTEM ORGANIZATION

This Section describes the organization of a typical GE-PAC 30 Digital System from both the physical, and the functional standpoints.

#### 3.1 Physical Organization

GE-PAC 30 Digital Systems employ a unique mechanical layout and wiring configuration which simplifies expansion of the system. Expansion consists of simply plugging in additional logic boards; no back plane wiring additions are normally required.

A GE-PAC 30 Digital System Consists of a basic card file which may be mounted in a standard 19" RETMA rack, and additional expansion card files mount up to 25 9.5" X 10.5" circuit boards designated motherboards. Two types of mother-boards are available: the standard copper motherboard and a wire-wrap mother-board. The copper mother-boards require one slot in the card file. Copper mother-boards provide a system in which most components

| Title                                                               | Publication<br>Number |

|---------------------------------------------------------------------|-----------------------|

| GE-PAC 30-1 Digital System (C) Maintenance Manual-Volume 2-Drawings | 29-027                |

| GE-PAC 30-2 Digital System (C) Maintenance Manual-Volume 2-Drawings | 29-035                |

| System Interface Manual                                             | 29-003                |

| Reference Manual                                                    | 29-004                |

| Logic Module Handbook                                               | 29-005                |

| Programming Manual 30-1                                             | 29-013                |

| Programming Manual 30-2                                             | 29-013R01             |

| Micro-Instruction Reference Manual 30-1                             | 29-017                |

| Micro-Instruction Reference Manual 30-2                             | 29-032                |

#### TABLE 1. RELATED PUBLICATIONS

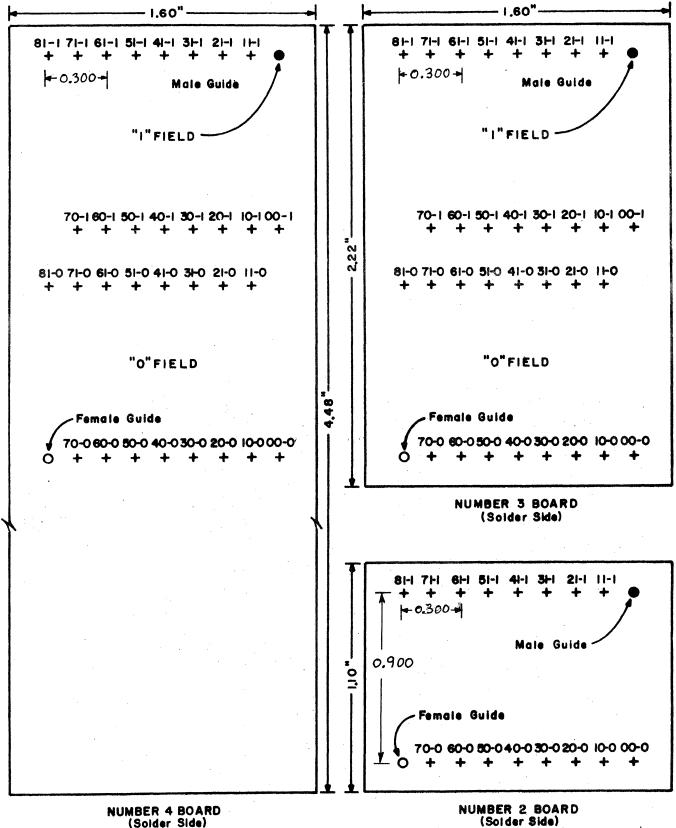

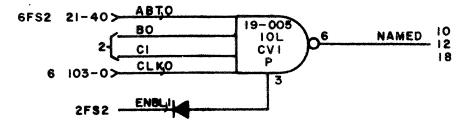

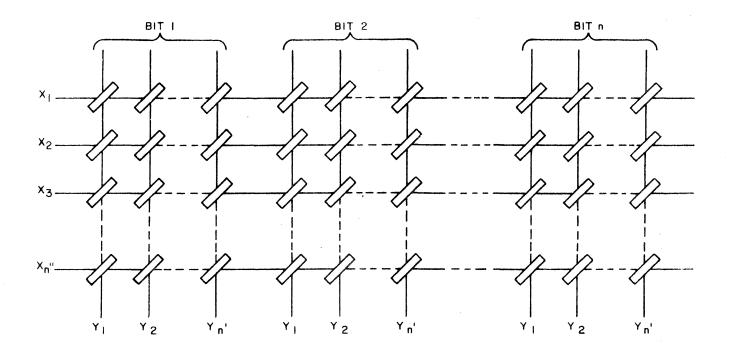

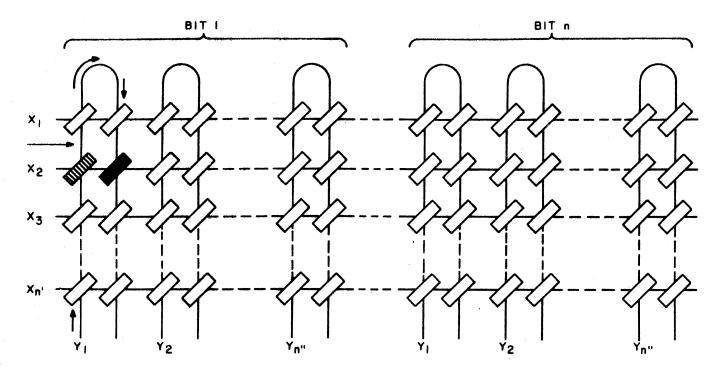

are soldered directly to the motherboard. Wire-wrap mother-boards are used for special applications, and in areas where the number of motherboards used does not warrant generation of a copper mother-board. Because of the wire-wrap pins on the back of these mother-boards, two slots in the card file are required for the wire-wrap mother-board. Each wire-wrap mother-board may mount up to 40 smaller component boards designated daughter-boards. Daughterboards plug into mother-boards via a set of 16 pins. The mother-board is divided into 40 fields as shown on Figure 2. Figure 3 illustrates a card file, mother-boards, and daughter-boards. A series of daughterboards which provides a variety of standard logic functions is available

from GE-PAC 30. Mother-boards with provisions for mounting potentiometers, relays, indicator lamps, capacitors, and resistors are also available. These general purpose components are described in the Logic Module Handbook, GE-PAC 30 Publication Number 29-005.

Note on Figure 3 that there are three sizes of daughter-boards. Figure 4 illustrates the size and pin designations for each of the three daughter-board sizes.

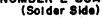

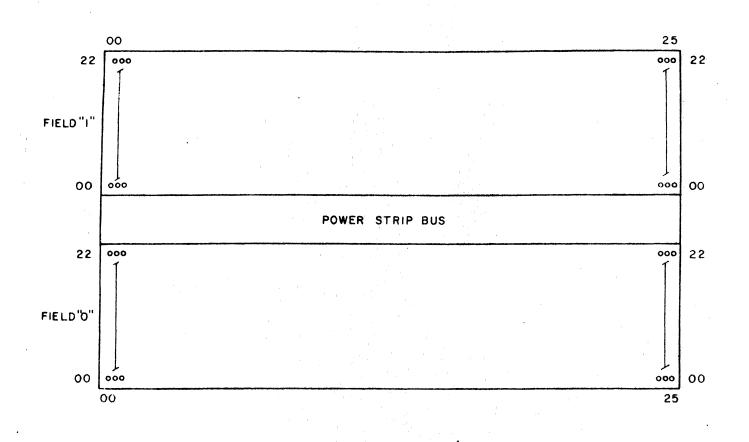

Each mother-board may have two 69-pin connectors. The back panel of a card file is shown on Figure 5. Note that the connectors are numbered from left to right on the wiring side. The lower row of connectors is designated Field 0; the upper row is designated Field 1. A strip power bus

Figure 2 Mother-Board Layout

is provided between the two fields. Figure 6 shows the pin numbering system. The first digit of the pin number specifies the column number, from 0 to 2. The second two digits specify the row number, from 00 to 22. The dash number at the end specifies the connector field.

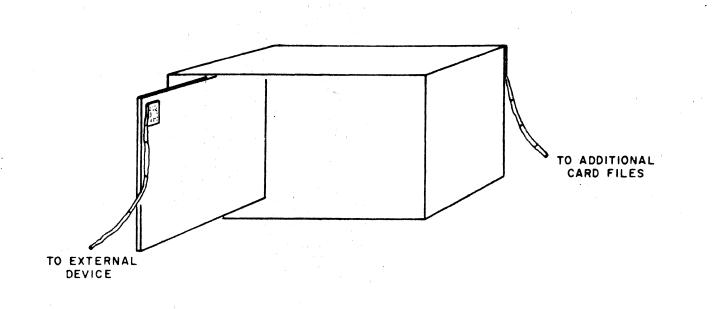

Wiring between card files is via plug in cables which mate with the wiring side of the mother-board connectors. Wiring between a card file and an external device is via a plug in cable which mates with one set of the daughter-board connectors on a mother-board. Figure 7 illustrates the interconnections between card files and external devices.

#### 3.2 Functional Organization

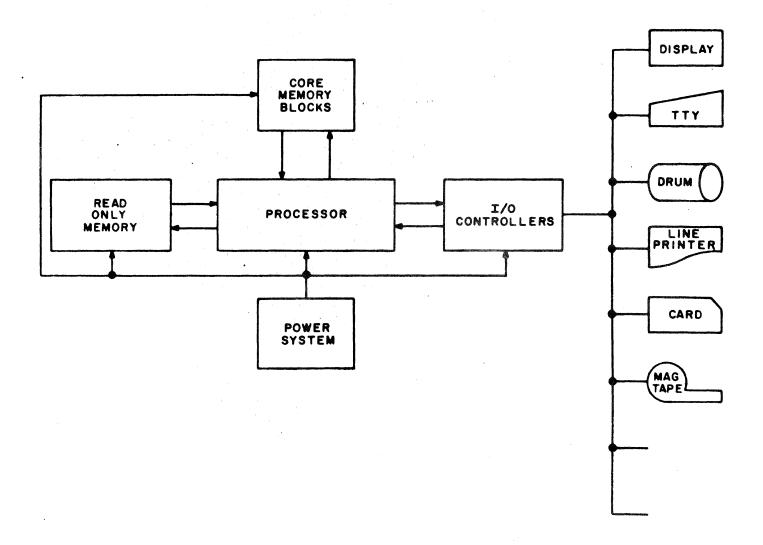

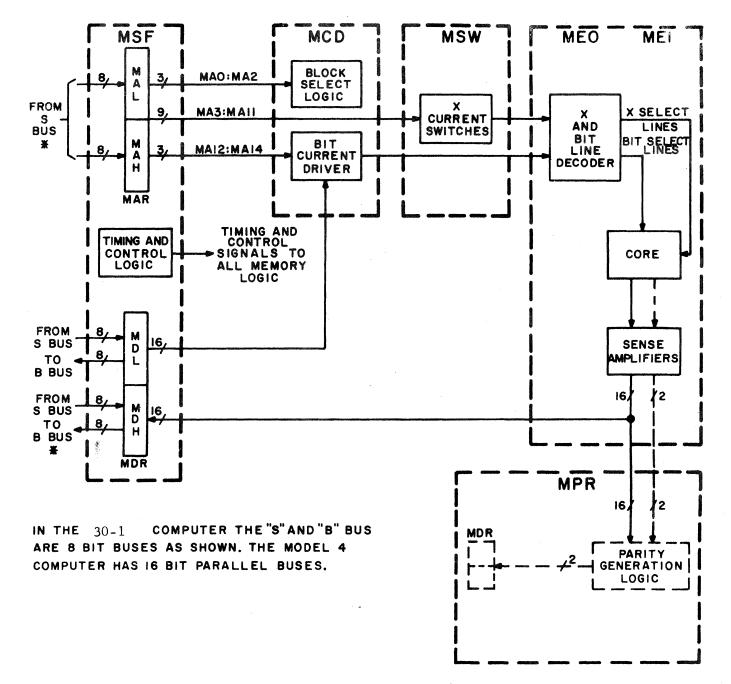

GE-PAC 30 Digital Systems are modularly structured to provide a high degree of flexibility in configuring application oriented systems. The basic building blocks used in the organization of a system are the Processor, Memory Modules, a Read-Only-Memory (ROM) Control Unit, and the Input/Output (I/O) Controllers which interface to peripheral devices. The various elements of an GE-PAC 30 Digital System are organized around the primary controlling unit - the Processor. See Figure 8.

Figure 3 Typical GE-PAC 30 Rack, ' Quarter Front View

#### Figure 4 Daughter-Board Layout

Figure 5 Typical GE-PAC 30 Rack, Back Panel Layout

The Processor contains facilities for:

- 1. Arithmetic and logic processing of data.

- 2. Sequencing instructions in the required order.

- 3. Addressing memory.

- 4. Fetching and storing information.

- 5. Initiating and controlling communications with external devices.

- 6. Taking action in response to interrupts.

These operations are performed as directed by instructions in the user's program.

The Processor and ROM provide a combination of hardware and firmware for decoding and executing user's instructions. GE-PAC 30 Processors are designed to execute ten basic micro-instructions. These microinstructions are programmed into subroutines that are permanently wired into a Read-Only-Memory (ROM). Each subroutine (or firmware) micro-program in the ROM executes a simple operation. Combinations of these subroutines perform the more complex operations that make up each user's instruction. (See the Reference Manual GE-PAC 30 Publication Number 29-004 for detailed descriptions of user's instructions.)

Figure 6 Mother-Board Connector Layout

The ten basic micro-instructions the GE-PAC 30 Processor is hardware wired to execute are:

1. Add (A)

2. Subtract (S)

- 3. Exclusive OR (X)

- 4. AND (N)

- 5. Inclusive OR (O)

- 6. Load (L)

7. Command (C)

8. Test (T)

9. Branch On Condition (B)

10. Do (D)

(See the Micro-Instruction Reference <u>Man-ual</u> for a detailed description of micrinstructions.)

The Processor has two-way communication channels with the Input/Output controllers and core memory system. These communication channels and the Processor internal registers employ an eight bit word length. Data is transferred within the Processor via eight bit B and S buses. The Processor performs micro-instructions by gating information from one location to another internally, or by sending signals to the units it controls.

Basically, the Processor executes successive micro-instructions read from the ROM. Together, these micro-instructions make up a micro-program which reads a user instruction out of core memory, decodes it, executes it, and then repeats the process for the next user instruction.

FIELD "I"

Figure 7 Typical GE-PAC 30 Rack, Interface Cable Layout

This Section describes the style and conventions used with GE-PAC 30 documentation.

#### 4.1 Number Notation

The most common form of number notation used in GE-PAC 30 documentation is hexadecimal notation. In this system, groups of four binary digits are represented by a single hexadecimal digit. Table 2 lists the hexadecimal characters employed.

To differentiate between decimal and hexadecimal numbers, hexadecimal numbers are preceded by the letter "X", and the number is enclosed in single quotation marks. Examples of hexadecimal numbers "rep: X'1234', X'5EC6', X'A340', X'EEFA', and X'10B9'.

#### 4.2 Part Numbering System

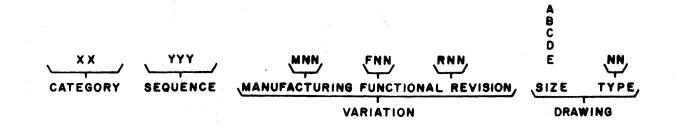

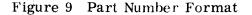

GE-PAC 30 parts, drawings, and publications employ a common numbering system. The part number and drawing numbers for drawings which describe the part are related. The publication number is also often related to the part number of the device or program described. Figure 9 shows the format used for GE-PAC 30 part numbers. The fields are described in the following paragraphs. 4.2.1 <u>Category Field</u>. The 2digit Category number indicates the broad class or category to which a part belongs. Typical examples of category number assignments are:

01 - Basic Hardware Systems

- 02 Basic Hardware Expansions

- 03 Basic Software Systems

- 04 Basic Software Expansions

- 05 Major Application Programs

06 - Self-contained Utility Programs

- 07 Subroutines of General Utility

- 10 Spare Parts Packages

- 12 Card File Assemblies

- 13 Panels

- 17 Wire and Cables

- 19 Integrated Circuits

- 20 Transistors

- 27 Peripheral Equipment

- 29 Manuals

#### TABLE 2. HEXADECIMAL NOTATION DATA

| Binary                                       | Decimal               |                       | č                                            |                        | Hexadecimal                | č –                          | 1. Sec. |                  |

|----------------------------------------------|-----------------------|-----------------------|----------------------------------------------|------------------------|----------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|

| 0000<br>0001<br>0010<br>0011<br>0100<br>0101 | 0<br>1<br>2<br>3<br>4 | 0<br>1<br>2<br>3<br>4 | 0110<br>0111<br>1000<br>1001<br>1010<br>1011 | 6<br>7<br>8<br>9<br>10 | 6<br>7<br>8<br>9<br>A<br>P | 1100<br>1101<br>1110<br>1111 | 12<br>13<br>14<br>15                                                                                            | C<br>D<br>E<br>F |

34 - Power Supplies

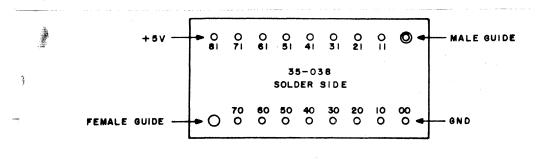

35 - Assembled Printed Circuit Boards

36 - Electro-Mechanical Devices

1.2.2 <u>Sequence Field.</u> The Sequence number identifies a particular item within the category. Sequence numbers are assigned serially, and have no other significance.

#### NOTE

The Sequence Field, like all other part number fields, may be lengthened as required. The field lengths shown on Figure 9 are minimum lengths (insignificant zeros must be added to maintain these minimums).

1.2.3 <u>Manufacturing Variation</u> <u>Field.</u> The optional Manufacturing Variation Field consists of the letter "M" followed by two digits.

#### NOTE

A part number must contain a Category number and a Sequence number. All other fields are optional.

The M Field is used to distinguish between parts which are electrically and mechanically equivalent (interchangeable), but which vary in method of manufacture. For example, if leads are welded instead of soldered on an assembly, the M Field changes.

An important exception to the meaning of the M Field exists for categories related to software. Here the M Field number, when used, indicates the form in which a particular program is presented. For example, define a program as a set of machine instructions. These same identical instructions may be presented on punched cards, paper tape, or magnetic tape; and for any of these they could be in symbolic form. Thus, there are many ways to present the same identical program. These ways are identified by the M Field numbers as follows:

M01 - Symbolic Punched Cards

M02 - Relative Binary Punched Cards

M03 - Absolute Binary Punched Cards

M04 - Symbolic Magnetic Tape

M05 - Relative Binary Magnetic Tape

M06 - Absolute Binary Magnetic Tape

M07 - Symbolic Punched Paper Tape

M08 - Relative Binary Punched Paper Tape

- M09 Absolute Binary Punched Paper Tape

- M10 Bootstrap Binary Object Punched Paper Tape

- M11 Read-Only-Memory (ROM) Absolute Binary Object Punched Paper Tape

- M12 ROM Wiring and Test Set (ROMWATS) Wiring Punched Paper Tape

- M13 ROMWATS Check Punched Paper Tape

- M14 Binary 8-bit Paper Tape

4.2.4 <u>Functional Variation</u> <u>Field</u>. The optional Functional Variation Field consists of the letter "F" followed by two digits. The F Field is used to distinguish between parts which are not necessarily electrically or mechanically equivalent, but which are described by the same set of drawings. For example, a power supply may be strapped internally to operate on either 110 vac or 220 vac. Except for this strap, all power supplies of this type are identical. The strapping option is easily described by a note on the assembly and test specification drawings. Therefore, this is a functional variation.

4.2.5 <u>Revision Field</u>. The optional Revision Field consists of the letter "R" followed by two digits. The R Field is used to indicate minor electrical or mechanical changes to a part which do not change the part's original character. R Field changes often reflect improvements. Parts with different R Fields are not necessarily electrically or mechanically interchangeable.

4.2.6 <u>Drawing Field</u>. The optional Drawing Field consists of a letter from "A" to "E" followed by two digits. The letter indicates the size of the original drawing. The sizes for each letter are:

$\begin{array}{l} A &= 8\frac{1}{2} \text{''} X 11 \text{''} \\ B &= 11 \text{''} X 17 \text{''} \\ C &= 17 \text{''} X 22 \text{''} \\ D &= 22 \text{''} X 34 \text{''} \\ E &= 34 \text{''} X 44 \text{''} \end{array}$

The two digits indicate the drawing type as follows:

01 - Parts Lists

- 02 Machining Details

- 03 Assembly Details

- 04 Lettering Details

- 05 Art Details

- 06 Wire Run Lists

- 07 Revision Control

- 08 Schematics

- 09 Test Specifications

- 10 Specifications

- 11 Bill of Materials

- 12 Information

- 13 Program Listings

- 14 Abstracts

- 15 Program Descriptions

- 16 Operating Instructions

- 17 Design Specifications

- 18 Flow Charts

4.2.7 Examples. The following list provides some examples of the part numbering system. The numbers were arbitrarily selected, and in most cases are fictitious.

35-060

The 60th printed-circuit board assigned a part number under this system.

35-060M01

A printed-circuit board electrically and mechanically interchangeable with the 35-060, but differing in method of manufacture.

A printed-circuit board not electrically and mechanically interchangeable with the 35-060, but described by the same set of drawings.

35-060R01

35-060F01

A revised 35-060 printedcircuit board, not necessarily electrically and mechanically interchangeable with the 35-060. Probably supercedes the 35-060.

35-060A01

The  $8\frac{1}{2}$  by 11 inch parts list for a 35-060.

35-060R01B08 The 11 by 17 inch schematic for a 35-060R01.

06-072The 72nd utility program<br/>assigned a part number.

06-072M03 An absolute binary deck of punched cards for the 06-072 program. 06-072A12

An  $8\frac{1}{2}$  by 11 inch information drawing on the 06-072 program. Probably a manual describing the program.

29-060

The 60th manual assigned a number under this system. Note that this number is not referenced in any way to the part number of equipment described in the manual.

4.3 Drawing System

This Section describes the drawings provided with GE-PAC 30 equipment. Note that drawings provided with peripheral devices and other purchased items may vary from the system described in this Section.

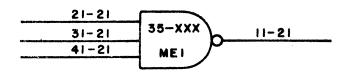

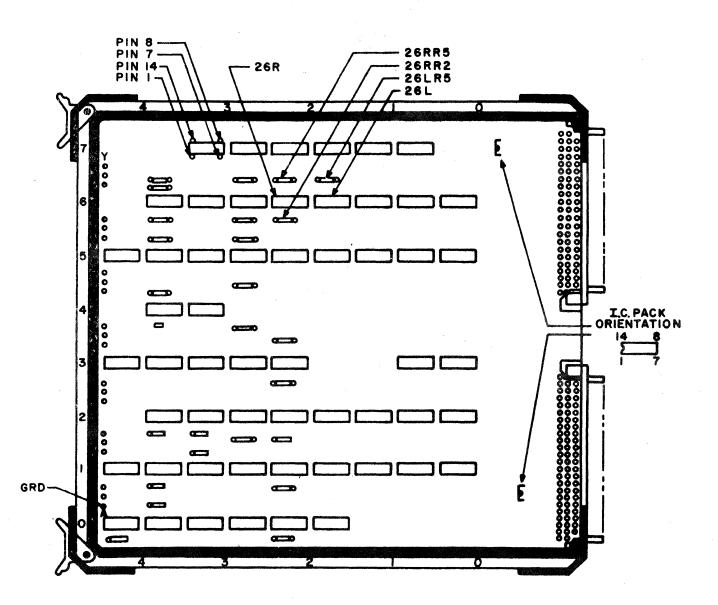

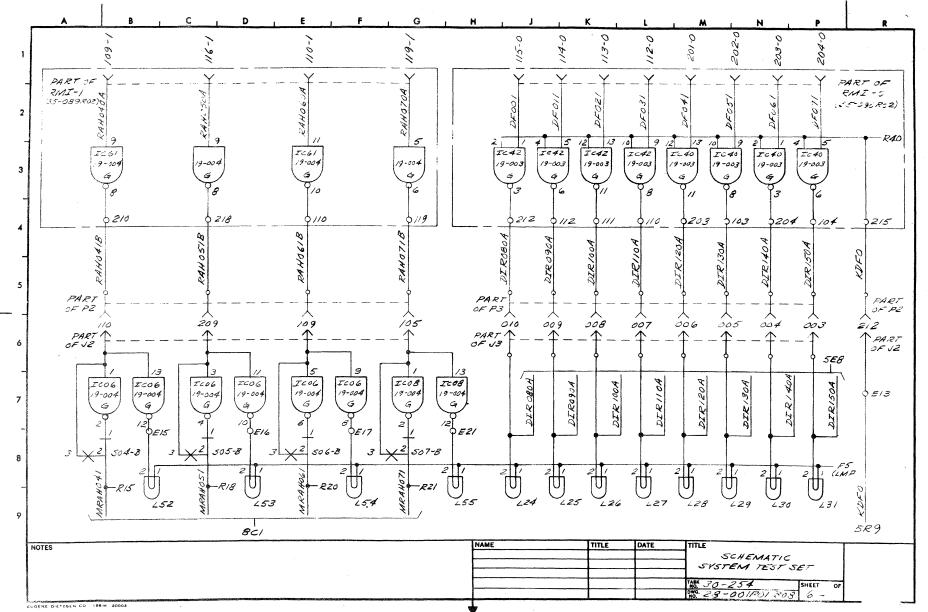

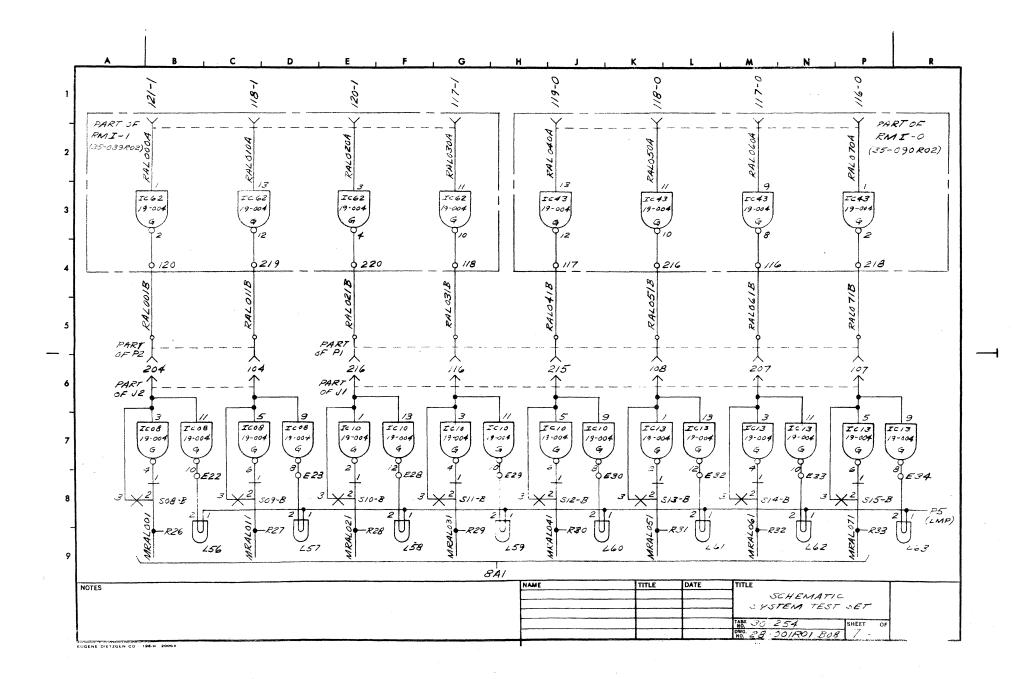

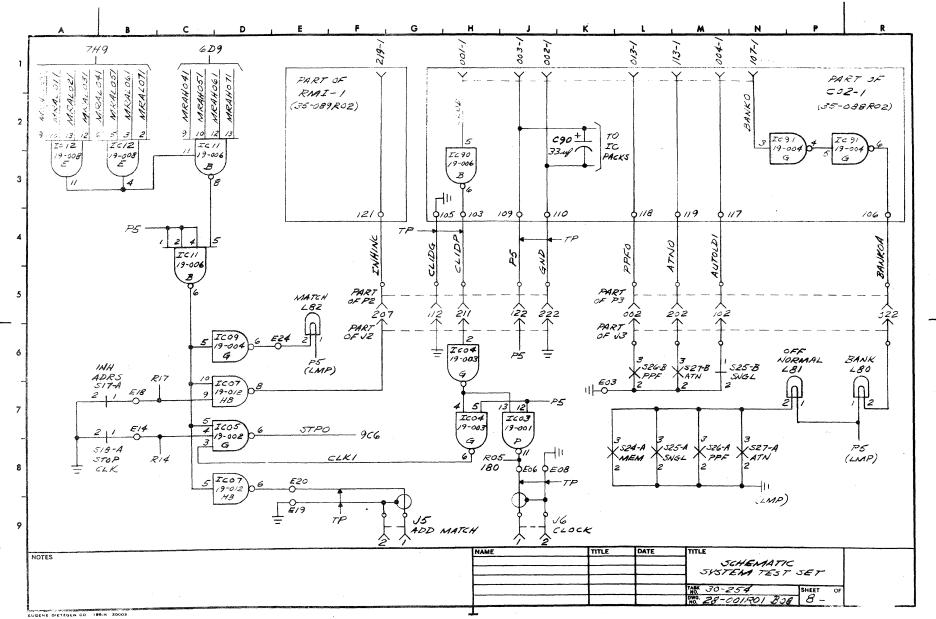

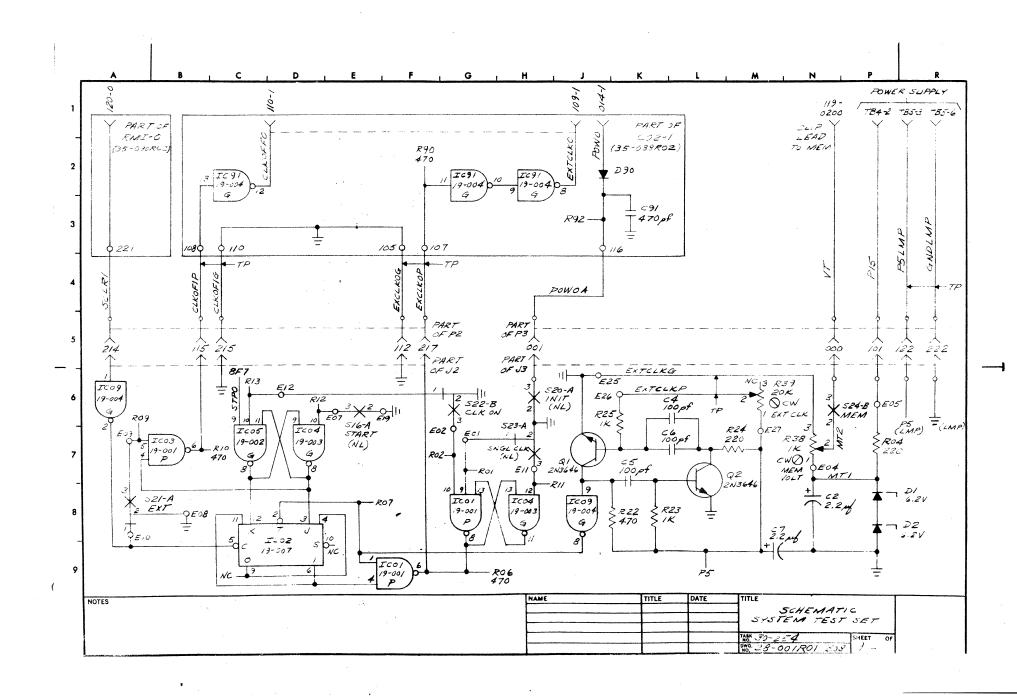

A digital system may be divided into a collection of functionally independent cirucits such as core memory, processor, I/O device controllers, read-only-memory, etc. These circuits may or may not be saleable units in their own right, but in the electrical sense they are essentially self contained and capable of performing their function with minimum dependence on other functional circuits in the system. Hence a functional circuit is treated as a building block. Each functional circuit is described electrically by a detailed Functional Schematic (FS). Each FS contains a variety of information including type and location of daughter-boards or discrete intergated circuits (IC's), pin connections, all interconnections within the FS, mother-board connector pin numbers and connections to other FS's. Further, the FS's are drawn to reflect, in an orderly fashion, all logical operations performed by the circuits.

Generally, symbols used on FS's conform to MIL-STD-806B. All pins are numbered as shown earlier in this Chapter on Figures 4 and 6. In FS drawings, a daughter-board is treated as a disposable package in the same sense that an IC or a transistor is considered as disposable. Thus, symbols for daughter-boards are presented on a daughter-board terminal basis. This does not necessarily reflect the actual physical layout of the board. For example, if only two diodes and the collector of a 4-input NAND gate are available at pins on the daughter-board, the symbol used on the FS drawing for that gate indicates a two input NAND.

Specific IC pin numbers within a daughterboard are considered inaccessible as far as FS drawings are concerned. The daughter-board pins on the other hand are accessible. Therefore, the daughter-board pins are shown on the FS. If any connection is contained completely within the daughterboard, no pin numbers are indicated. Where IC's, transistors, or other discrete components are mounted directly on the mother-board, symbolic notation and pin numbering conform with the standards established by the industry.

Registers are named according to the following rules:

- 1. The register mnemonic name has a maximum of three letters, excluding "I, O, Q, and Z".

- Each bit in the register is numbered, usually starting at 00 on the left, and continuing to N-1 on the right, where N is the number of bits in the register.

- 3. The 00 bit is the Most Significant Bit and the N-1 is the Least Significant Bit.

The components on any given mother-board may be contained on plug-in daughterboards, they may be connected directly to the mother-board, or there may be a combination of both. The technique for identifying and locating the components, and their pin numbers, is described in the following paragraphs.

First consider the case where all components are mounted on daughter-boards. In a few cases, one descriptive symbol can be assigned to a complete daughter-board. Generally though, it is more convenient to draw discrete logic elements (gates, flipflops, etc.) rather than to develop specialized symbols for each and every daughterboard. Regardless of the symbol, all pin numbers and device identification numbers are relative to the daughter-board rather than to the specific IC's, transistors, etc. No specific information is shown on the FS that locates a device internally on a daughter-board. Four different pieces of information are indicated for a logic symbol when the device is contained on a daughter-board.

- 1. Daughter-Board Type

- 2. Mother-Board Location

- 3. Daughter-Board Pin Numbers

- 4. Daughter-Board Location

The daughter-board type is identified by its part number (category and sequence field). All daughter-boards have the number 35 in the category field. Following the daughterboard type number are three or four characters used to identify which mother-board contains the daughter-board. (If all daughterboards on an FS sheet are on the same mother-board, the mother-board is identified in a footnote.) If possible, the motherboard is located absolutely by the back panel connector number that it plugs into. However, in many cases an absolute location cannot be specified for a mother-board, particularly in the case of I/O control cards and memory, where the same mother-board may be used many times. I/O motherboards are identified mnemonically using three characters. Here the leading two characters are upper case letters, while

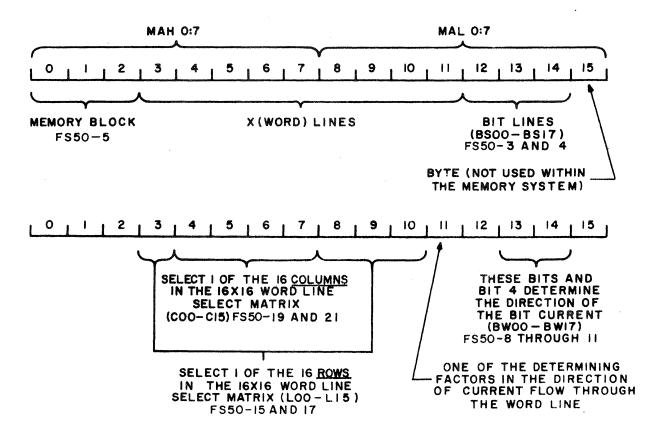

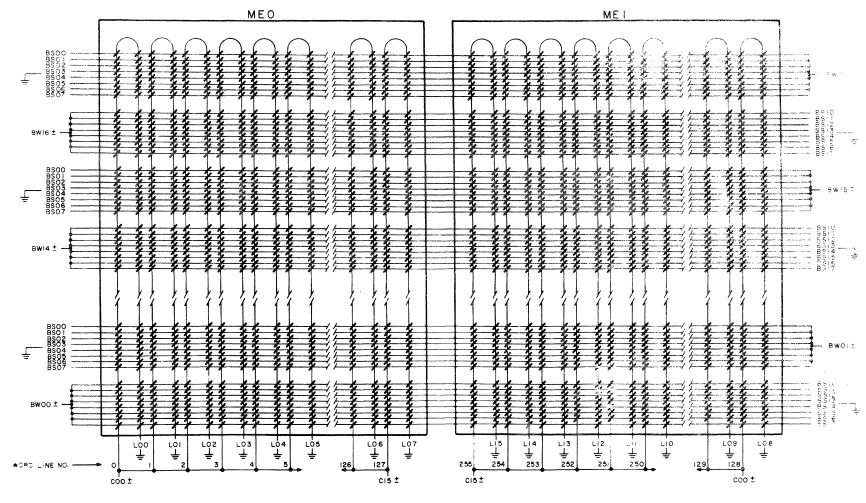

the last character may optionally be a number that specifies which mother-board in cases where more than one motherboard of that type is provided. For example, ME0 and ME1 for Memory boards 0 and 1 respectively. Figure 10 shows the symbol for a three-input NAND gate on the ME1 board. Note that 35-XXX is the daughterboard type, and ME1 is the mother-board containing the circuit. When possible, the designations are written inside the symbol as shown. The daughter-board type number must be shown for every symbol.

Figure 10 Three-Input NAND Gate Symbol,

Wire Wrap Mother-Board

As mentioned previously, only daughterboard pin numbers are shown on FS drawings. These pin numbers correspond directly with the mother-board pin numbers within a mother-board field. Every connection available to a device via a daughterboard pin is shown. This is done by writing the pin number first, followed by the mother-board field number that contains the pin. Therefore, the pin numbering system for FS drawings indicates the position of the daughter-board in terms of the mother-board field (s) that it covers) as well as the pin number within that field. Thus, the output from the gate on Figure 10 appears at mother-(and daughter-)board pin

number 11, in mother-board field 21 on the ME1 board. When IC's are mounted directly on the mother-board, they must be located in either the Left (L) or the Right (R) position within a mother-board field. Each symbol is labeled on the FS with the device part number (category and sequence). The category number for IC's is 19. Thus, a power gate mounted directly on a motherboard is indicated as shown on Figure 11. Note that the pin numbers correspond directly with the actual IC pin numbers. Note further that the mother-board field number is 10 and the the IC is in the Left position in that field. Figure 12 illustrates the method used to determine component location on a copper mother-board. Note that the same basic zone system employed on the wire-wrap boards is used on the copper mother-board as well. Use zone 26 as an example. Note that each zone is divided into two halves. The halves are designated Left and Right from the copper side. Therefore, the Left and Right zones are reversed, as indicated, if viewed from the apparatus side. Up to six other components (resistors, capacitors, and/or diodes) can be located in each half of the zone, in addition to the integrated circuit module. Three locations are provided above the integrated circuit module, and three locations are provided below the integrated circuit module. The locations are numbered one through six from bottom to top. As shown on Figure 12, the component designations take the form 26LR6, where 26 is the zone, L indicates the Left side of the zone as viewed from the copper side, R designates a resistor, and 6 is the component location. A capacitor in the same position would be

Figure 11 Power Gate Symbol, Copper Mother-Board

Figure 12 Typical Copper Mother-Board, Component Location Diagram

designated 26LC6; a diode would be designated 26LD6. Up to 21 test points are provided at the rear of the mother-board. The test points are lettered bottom to top from A through Y (omitting I, O, L and Q). The A test point is always ground.

A net is defined as an electrical connection between two or more points in a circuit. Ordinarily, a net has an originating end (usually a collector where the signal is generated) and one or more terminating ends. Often it is convenient to assign descriptive mnemonic names to nets as a way of identifying them on FS's. Whether a net is named or not is sometimes arbitrary. However, a net is always assigned a name if:

- 1. The net is contained on one drawing sheet but is not shown as a complete solid line on that sheet.

- 2. Part of the net appears on more than one sheet.

- 3. Part of the net connects with a different FS.

4. Part of the net leaves a mother-board.

If a net is named, the following rules are observed.

- 1. All mnemonic names are a maximum of five characters.

- 2. All decimal digits and upper case letters except the letters "I, O, Q, and Z" are permitted.

- 3. No other characters permitted.

- 4. Where possible, mnemonics are descriptive. However, it should be recognized that descriptive names are not always possible and a danger of misinterpreting a mnemonic exists.

- 5. Mnemonic names are not repeated within an FS.

- 6. Every mnemonic is suffixed by a state indicator. This indicator consists of the digit "1" for the logically true state, or the digit "0" for the logically false state. For example, the set side of a flip-flop would have the "1" state indicator, while the reset side would have the "0" state indicator. The state indicator for a function changes each time that function is inverted. Thus, the state indicator permits assigning the same mnemonic to functions that are identical except for an inversion.

- When a logical function is inverted, an inversion indicator is added after the state indicator. This allows for functionally equivalent, but electrically

different nets to have the same mnemonic name. For example, assume a signal NAME1. NAME1 may be inverted to produce NAME0. If NAME0 is then inverted, NAME1A is produced. NAME1 and NAME1A are functionally equivalent, but physically different nets.

Sometimes a net fans-out to many sheets in an FS. It is also possible for a net to fanout to sheets in different FS's. In these situations, the net is assigned a mnemonic name. The net is also "zoned" from sheet to sheet to allow for properly identifying the originating and terminating ends of the net. The originating end of a net is defined as the collector at which a signal is generated. All other points to which the net connects are called terminating ends. When a lead leaves a sheet at the originating end, it is zoned to each and every sheet on which the net reappears, by indicating first the page number, followed by the FS number that contains that page. For example, assume that the gate shown on Figure 11 is on FS1, sheet 20. The output, NAMEO, appears on sheets 10, 12 and 18 of FS1. Note that the FS1 is implied. When a net enters a sheet from another sheet, it is labeled with the same mnemonic name, and is zoned back to the originating end of the net only. Thus, on Figure 11, the ENBL1 may, however, have many other terminations in addition to the one shown. Generally then, when a net leaves the sheet where it originates, it is zoned to every other sheet where the net terminates, while the terminating end is zoned only to the orignating sheet.

When a lead leaves a mother-board, it usually does so through a mother-board back panel connector pin. These connector pins must be shown on the FS even if the complete net is shown on one drawing sheet. Only the connector pin number need be indicated under the pin symbol, since the connector number itself is implied by the

8. a.J. : **6**. a

mother-board location number in the logic symbol or in the footnote. Thus, on Figure 11, CLK0 enters the CU1 mother-board on pin 103 of the lower connector.

Sometimes, particularly in the I/O area, cables enter and leave via special daughterboards plugged directly into the motherboard. Here the same symbol is used, but it is labeled as standard daughter-board pins. For example, on Figure 11, ABT0 enters CU1 via a cable connected to a daughter-board plugged into Field 40, to Pin 21. Figure 13 is a typical FS sheet with call-outs illustrating many of the conventions described in this Section.

The FS drawings for the basic Digital System and some of the more common expansions are included in Volume 2 of this manual. FS drawings for other expansions are included with the expansion or in publications which describe the expansions.

# THE GE-PAC 30-1 PROCESSOR

### TABLE OF CONTENTS

| 1. | INTF                       | RODUCTI                                                     | ON 1                                                                                                                                                                                                                     |  |  |  |

|----|----------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2. | BLOCK DIAGRAM ANALYSIS 1   |                                                             |                                                                                                                                                                                                                          |  |  |  |

| 3. | 3. FUNCTIONAL DESCRIPTIONS |                                                             |                                                                                                                                                                                                                          |  |  |  |

|    | 3.1<br>3.2<br>3.3          | Initializ                                                   | control.       4         ce Control.       7         sor Registers       9                                                                                                                                               |  |  |  |

|    |                            | 3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8 | ROM Data Register9ROM Address Lower Register10ROM Address Higher Register11ROM Address Slave Register (RAS)12DO Flag Register (DF)12Register Stack15Arithmetic Register16System Control Register16System Data Register17 |  |  |  |

|    | 3.4                        | 3.4.1 $3.4.2$ $3.4.3$ $3.4.4$ $3.4.5$ $3.4.6$ $3.4.7$       | etic Logic Unit18Load, Load Immediate, Branch, Command And Test20Shift Left20Shift Right20Load One's Complement20AND And AND Immediate21OR And OR Immediate21Exclusive OR And Exclusive OR Immediate21Add and Subtract22 |  |  |  |

|    | 3.5                        | I/O Con                                                     | trol23                                                                                                                                                                                                                   |  |  |  |

| 4. | MAI                        | NTENANG                                                     | CE                                                                                                                                                                                                                       |  |  |  |

|    | 4.1<br>4.2                 |                                                             | iming                                                                                                                                                                                                                    |  |  |  |

| 5. | PRO                        | CESSOR                                                      | MNEMONICS                                                                                                                                                                                                                |  |  |  |

i

### ILLUSTRATIONS

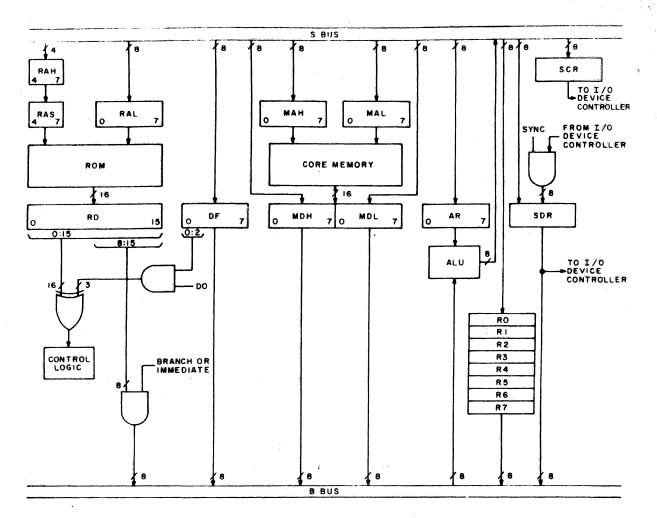

| Figure 1. | GE-PAC 30-1 Digital System, Block Diagram 2     |

|-----------|-------------------------------------------------|

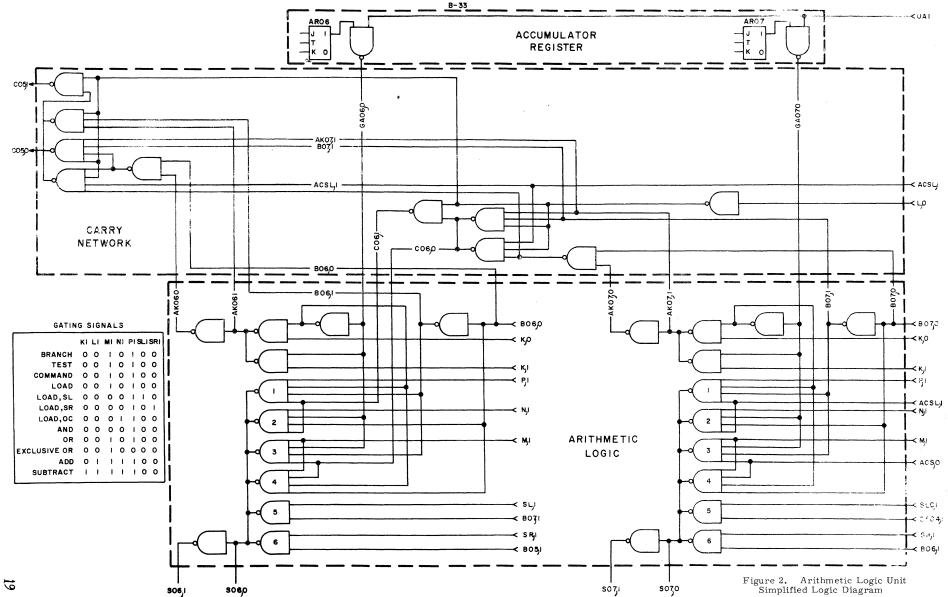

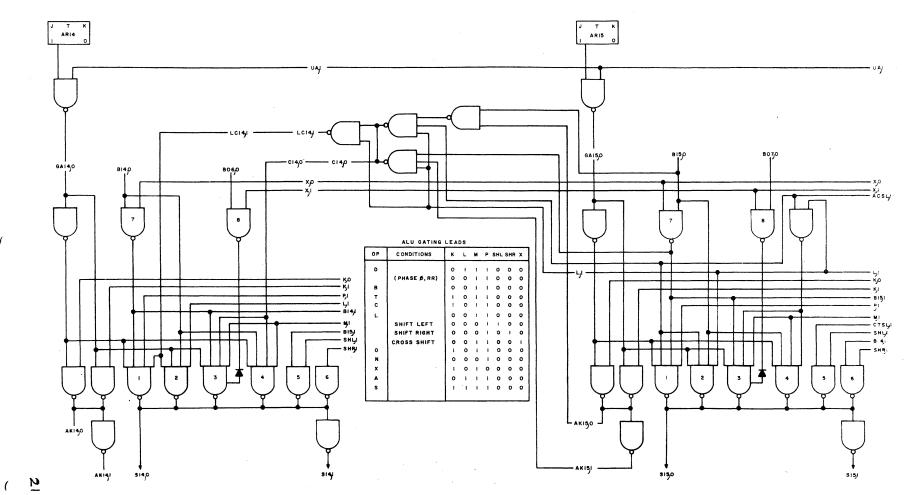

| Figure 2. | Arithmetic Logic Unit, Simplified Logic Diagram |

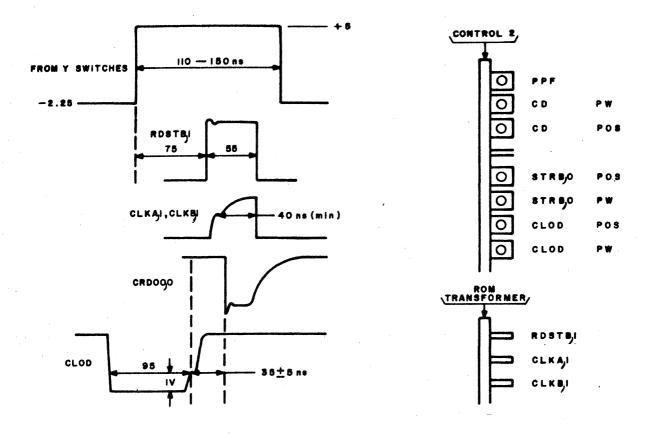

| Figure 3. | Processor Timing Data                           |

#### 1. INTRODUCTION

This Section describes the 30-1 Processor. Refer to the General Description Section earlier in this manual for a description of the functional organization of a GE-PAC 30-1 Digital System. This Section includes a block diagram analysis, functional descriptions which reference schematics provided in Volume 2 of this manual, maintenance information, and a mnemonic list.

#### 2. BLOCK DIAGRAM ANALYSIS

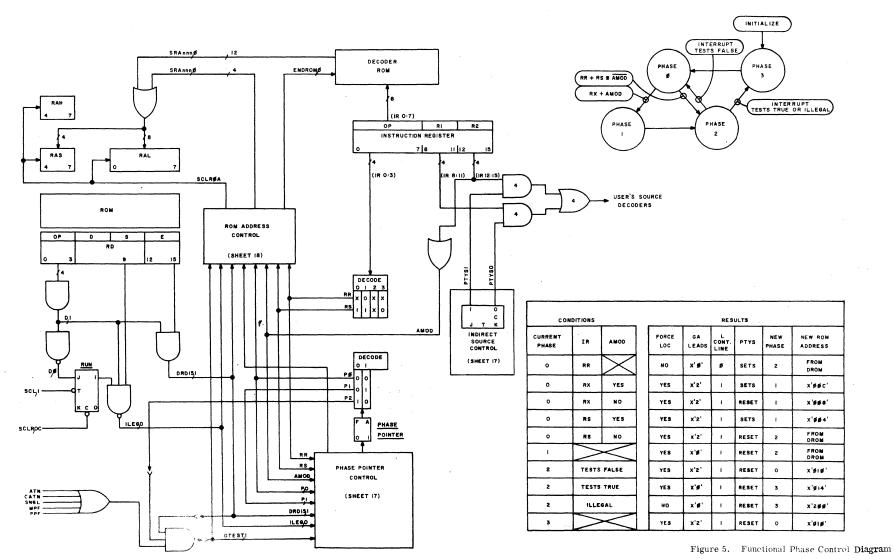

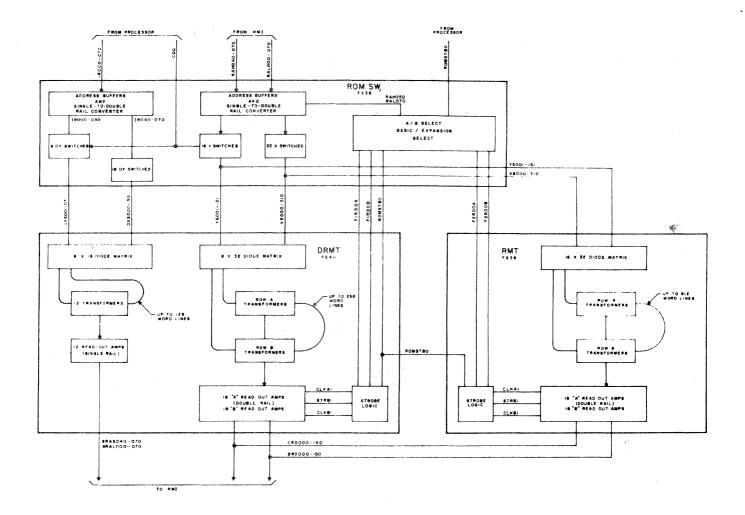

Figure 1 is a block diagram of the 30-1Digital System. The heart of the 30-1 is the Read-Only-Memory (ROM). The ROM permits micro-programming the to appear as though it has the capa-30-1 bilities of a much larger computer. The operation of the 30-1 is directed by a program wired into the ROM. When executing the instructions of the emulated computer, the micro-program directs the hardware to read the next instruction to be executed from core memory. The microprogram then decodes the emulated (user's) instruction by performing logical and arithmetic operations on the data that was obtained from memory. Having decoded the instruction, the micro-program then enters a micro-subroutine that has been designed to perform the emulated instruction. The loop is then closed by incrementing an emulated instruction counter and returning to the point in the micro-program that will fetch the next instruction from memory. By adding the logic necessary to start, stop, and select a starting address for the microprogram, the machine is made to appear much larger.

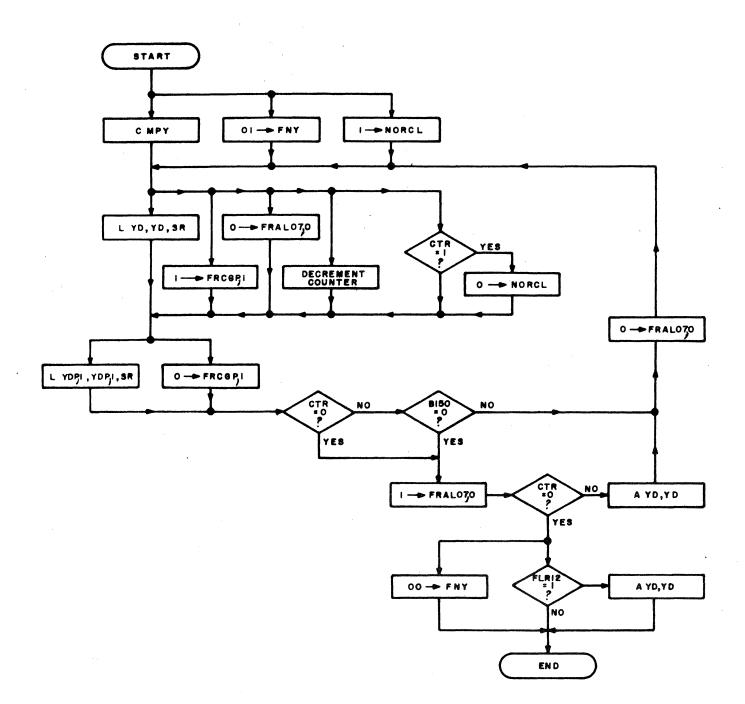

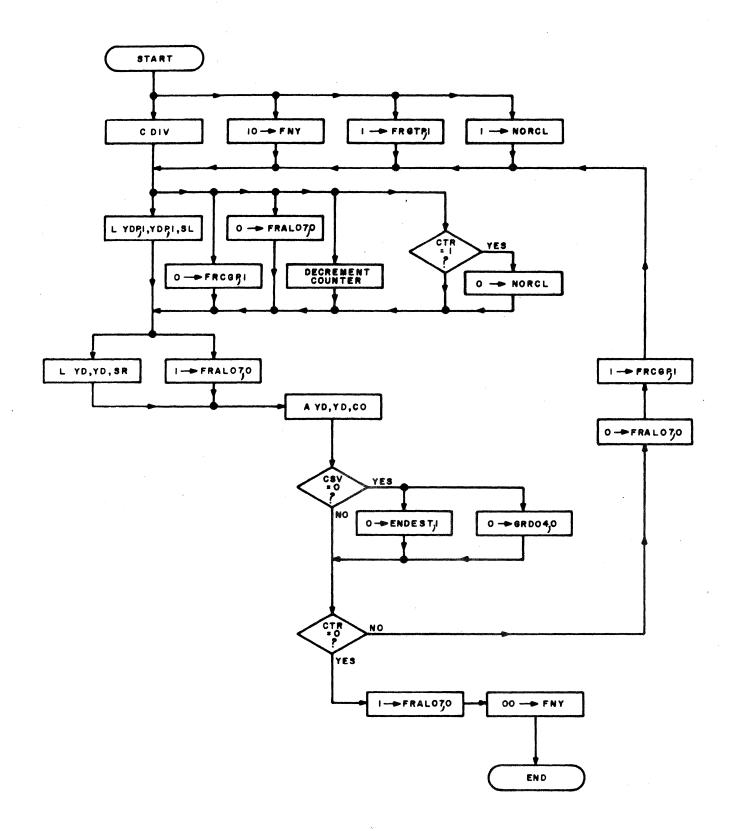

The micro-program wired into the Read-Only-Memory consists of combinations of 16 micro-instructions. The 16 microinstructions the 30-1 executes, and their operation codes, are listed below. For a detailed explanation of each instruction, refer to the <u>Micro-Programming Reference</u> Manual, Publication Number 29-017R01.

| INSTRUCTION            | OP-CODE |

|------------------------|---------|

| DO                     | 0000    |

| Branch                 | 0001    |

| Test                   | 0010    |

| Command                | 0011    |

| Load                   | 0100    |

| Load Immediate         | 0101    |

| OR                     | 0110    |

| OR Immediate           | 0111    |

| AND                    | 1000    |

| AND Immediate          | 1001    |

| Exclusive OR           | 1010    |

| Exclusive OR Immediate | 1011    |

| Add                    | 1100    |

| Add Immediate          | 1101    |

| Subtract               | 1110    |

| Subtract Immediate     | 1111    |

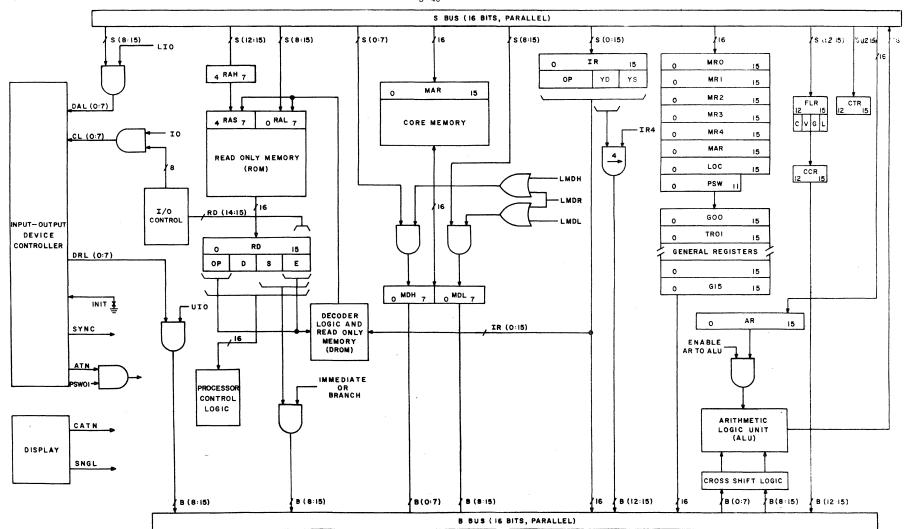

Figure 1. GE-PAC 30-1 Digital System, Block Diagram

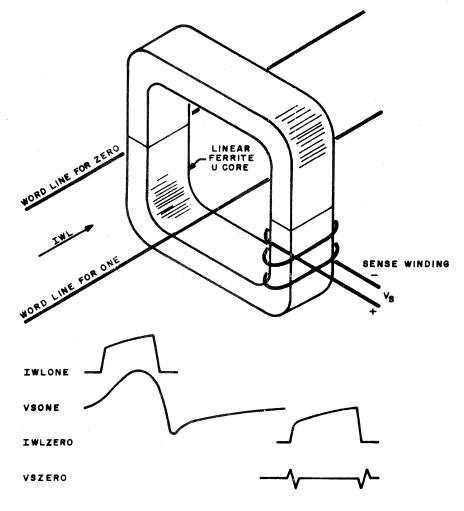

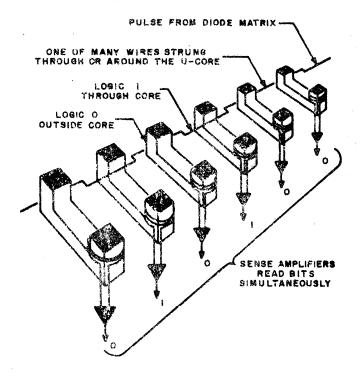

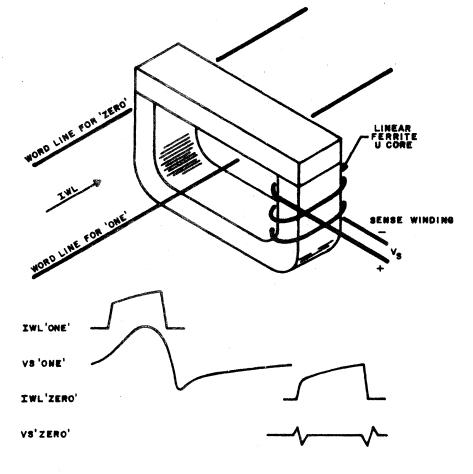

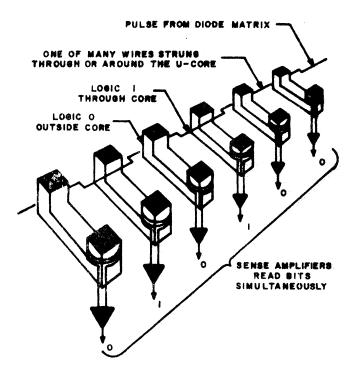

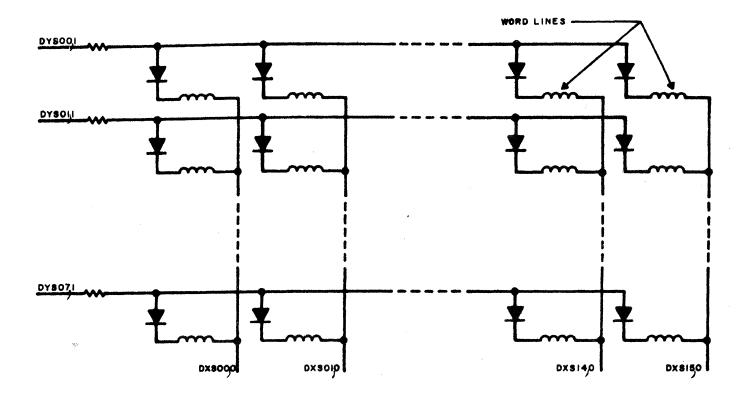

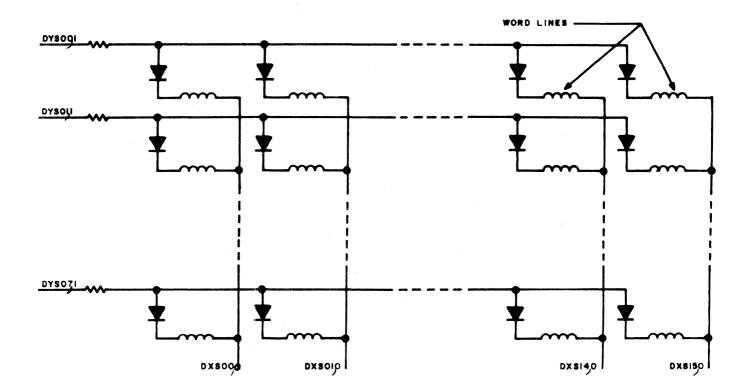

The Read-Only-Memory (ROM) contains the micro-code program to fetch, decode and execute the user's instructions stored in the Core Memory. The ROM is a high speed, non-volatile, memory made up of pulse transformers. (See the ROM section of this manual.)

The Processor executes micro-instructions extracted from the Read-Only-Memory (ROM) by gating data through the Arithmetic Logical Unit (ALU). All data is transferred within the Processor on the eight bit B and S Buses shown on the top and bottom of Figure 1.

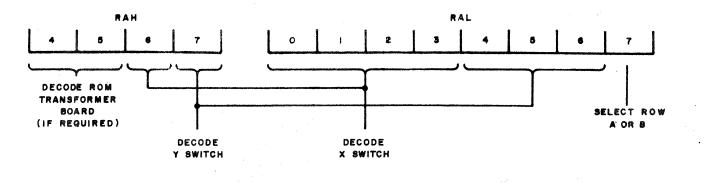

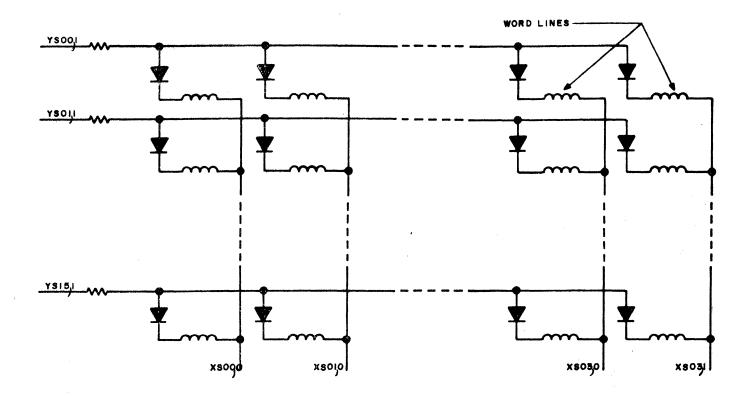

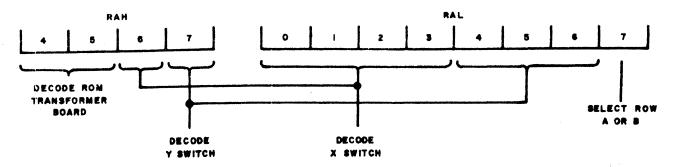

The location of the micro-instruction extracted from the ROM is designated by the twelve bit address contained in the ROM Address Lower register (RAL), and the ROM Address Slave register (RAS). RAL is an eight bit micro-instruction location counter. It is loaded with the contents of the S Bus during a Branch instruction or when specified as a Destination register, and incremented by one between execution of all other instructions. RAS is a four bit register that holds the ROM page address. It is loaded with the contents of the ROM Address Higher register (RAH) whenever RAL is loaded from the S Bus. Neither the RAS nor the RAL are involved in the incrementing of the RAL. Therefore, to transfer from one page of 256 words of ROM to another, the destination page number is first loaded into the RAH from the S Bus. When the location address is loaded into RAL. RAS is loaded with the contents of RAH. This insures that the new location address and page address are sensed in the ROM address decoders simultaneously.

Every micro-instruction extracted from the ROM is placed in the ROM Data Register (RD) where it remains while the instruction is executed. RD is a 16 bit micro-instruction register. It is reloaded from the ROM at the completion of each micro-instruction. The outputs from RD are DC inputs to the Control Logic. The Control Logic directs the Processor actions based on the contents of RD.

in synappi

Within the Control Logic, the instructions are decoded to activate gating leads to the ALU. The Source and Destination address are decoded, and the signals to unload registers to the B Bus and load registers from the S Bus are generated. Core memory actions are initiated from Control and the signals directing the clock system and initialize circuits are also maintained. RD bits 0:3 are decoded as the operation code of the micro-instruction being executed, except during a DO instruction. During a DO instruction, bits 0:2 of the DO Flag Register are decoded as the operation code.

RD bit 3 determines Immediate instructions. An Immediate instruction is one that has the specific data to be manipulated appended to the instruction word itself. During execution of an Immediate instruction or a Branch instruction, RD bits 8:15 are gated onto the B Bus and treated as data. Since bit 3 of the DO Flag Register is not decoded during a DO instruction, Immediate instructions cannot be implemented.

The D field (4:7) of the RD register specifies the destination of the micro-operation performed in the ALU. The result of the microoperation is placed on the S Bus by the ALU and then gated from the S Bus to the destination register specified by the D field.

The S field of the RD register (8:11) selects the register to be gated to the B Bus. This register is the source of one operand to be used in arithmetic and logical operations. The source of the other operand is always assumed to be the A Register (AR). The E field of the RD register (12:15) is an extended micro-operation modifier. This field permits control of such things as flags and carries, or shifting and one's complementing operations.

The DO Flag Register (DFR) serves as an eight bit general purpose register, in addition to being the memory for flags indicating the results of the micro-instructions and the source of op-codes during execution of DO instructions. The DFR can be loaded with the contents of the S Bus or unloaded onto the B Bus. The DFR can be considered as two separate four bit registers. The flag register portion (bits 4:7) contains four flags: Carry (C), Overflow (V), Greater (G), and Less (L). These flags may be set or reset upon conclusion of arithmetic and logical operations and tested by the Branch microinstruction. The DFR bits 0:3 form a four bit register. The most significant two bits are used as the Op-Code of the micro-operation when a DO micro-instruction is loaded into the RD register. The DO micro-instruction therefore directs the micro-processor to execute the micro-instruction located in the DFR. This provides a means of performing multiple functions with a single micro-subroutine.

The register stack consists of eight general purpose registers (R0 through R7). These registers are each eight bits long and may be considered as a high speed working memory for the micro-computer. Designating one of these registers in the Source field (S) of a micro-instruction causes its contents to be placed on the B Bus. Designating one of these registers in the Destination field (D) causes it to be loaded with the data present on the B Bus.

The Arithmetic Logic Unit (ALU) normally performs the micro-instruction in RD. The specific operation executed, is determined by the gating leads activated as the Control Logic decodes the micro-instruction. The B Bus is always input as one operand to the ALU. The other operand is taken from the A Register (AR). The AR is an eight bit register that can be loaded from the S Bus and input to the ALU as an operand, if specified by the instruction being executed. Therefore, the ALU manipulates data received only from the B Bus, or data received from both the B Bus and the AR. The output from the ALU is gated onto the S Bus.

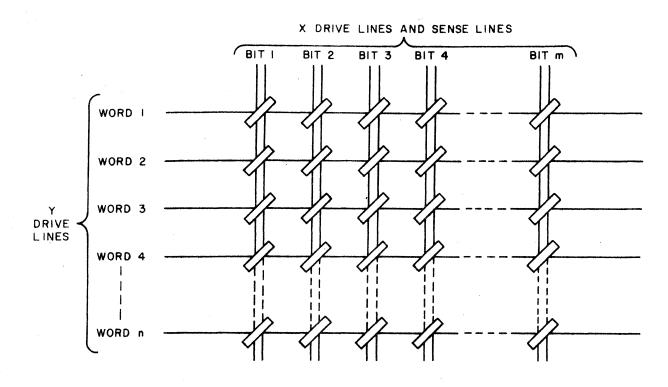

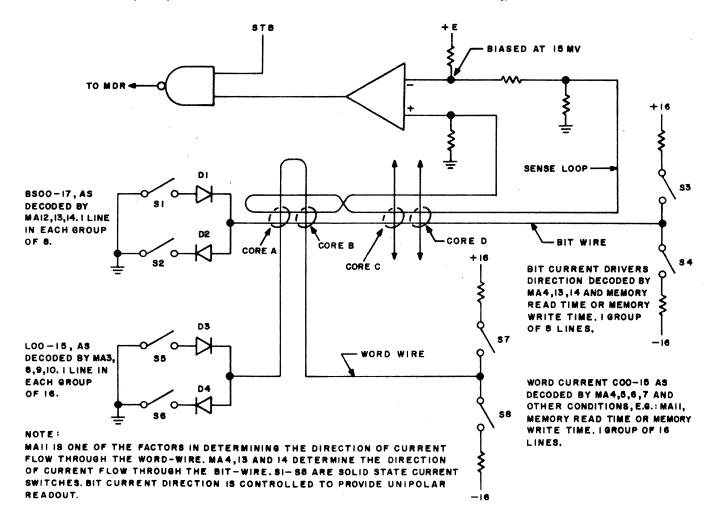

The Core Memory is the source of User instructions and data constants. It consists of ferro-magnetic cores and contains from 2K to 32K 16 bit locations. (See the Core Memory Section of this manual.) Memory operations are initiated by the Control Logic during execution of a Command micro-instruction. The location extracted from core memory is designated by the two eight bit memory address registers, MAH and MAL. Memory Address Higher (MAH) contains the most significant eight bits. MAH and MAL are loaded from the S Bus prior to the memory operation. Together, MAH and MAL form the 16 bit memory address. The core memory reads and writes 16 bit words. The two eight bit Memory Data Registers (MDH, MDL) hold the 16 bits read from, or written into, memory. Memory Data Higher (MDH) and Memory Data Lower (MDL) can be loaded from the S Bus in preparation for a memory write operation, or unloaded onto the B Bus following a memory read operation. Memory timing considerations are resolved by the Processor. If the micro-program tries to unload the Memory Data Registers immediately following a memory read, the Processor simply waits until the data is available. Non-memory directed microoperations may be interleaved with the memory operations for maximum speed.

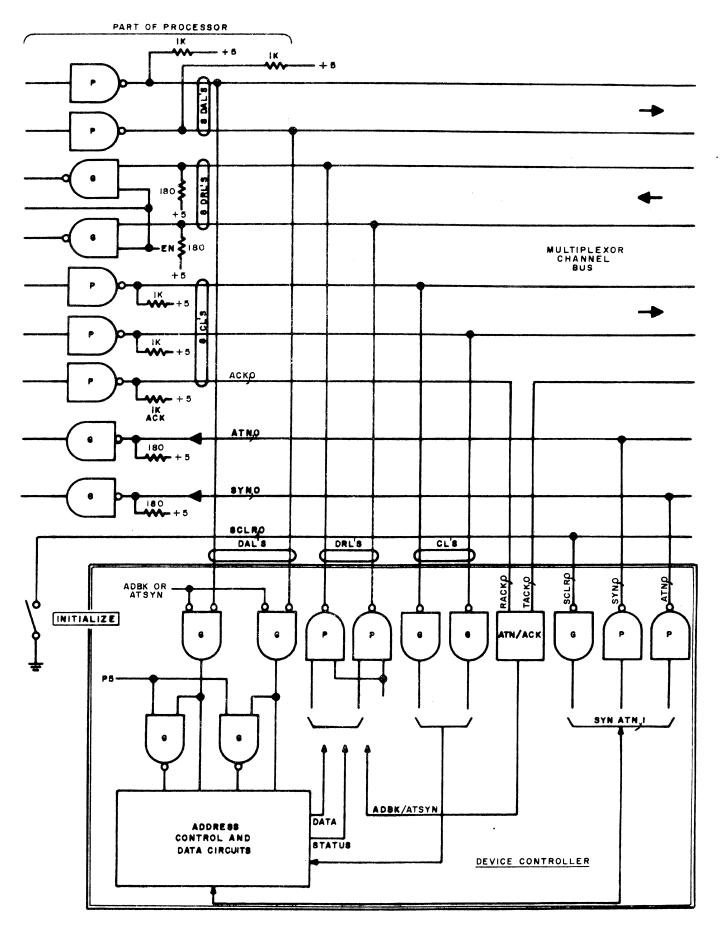

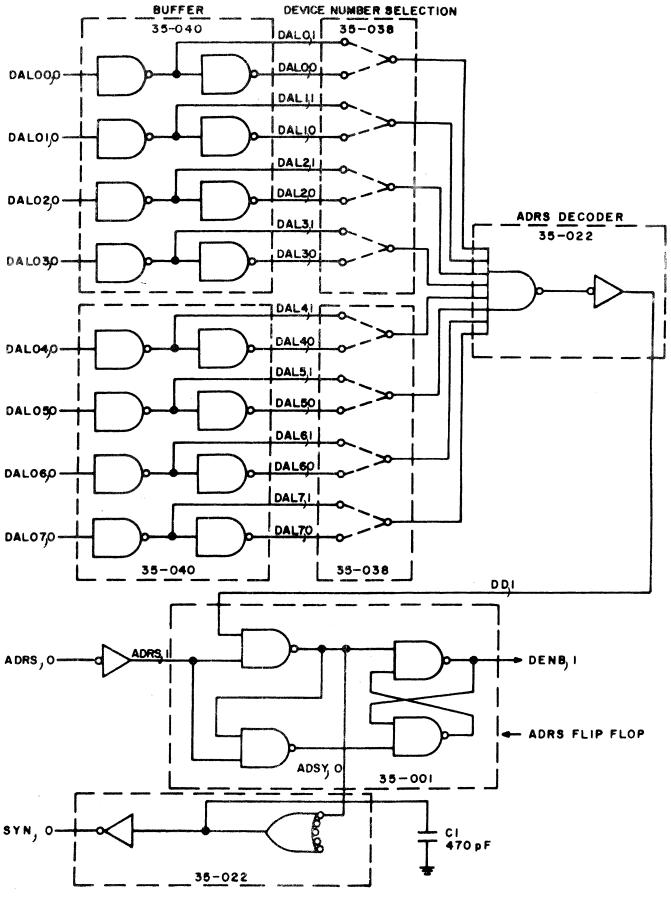

The System Control Register is an eight bit instruction register for the device controllers. It is loaded with the contents of the S Bus and output to the device controllers. Each bit of the SCR directs the device controllers to load data into, or accept data from, the System Data Register (SDR). The type of data to be loaded or unloaded is determined by the bits of the SCR. When the device has performed the function indicated by the SCR, it responds by raising the Sync line. The status of this line, and others, may be ascertained by the Test micro-instruction.

The System Data Register (SDR) serves as a buffer between the Processor and device controllers. During Write operations, SDR is loaded from the S Bus, and output to the device controllers. During Read operations, data is gated into SDR with the returning Sync pulse, and then unloaded onto the B Bus by the micro-code.

#### 3. FUNCTIONAL DESCRIPTIONS

This Section provides descriptions of the major Processor functional groups. The descriptions reference both simplified drawings provided in this Section, and Functional Schematics provided in Volume 2 of this manual.

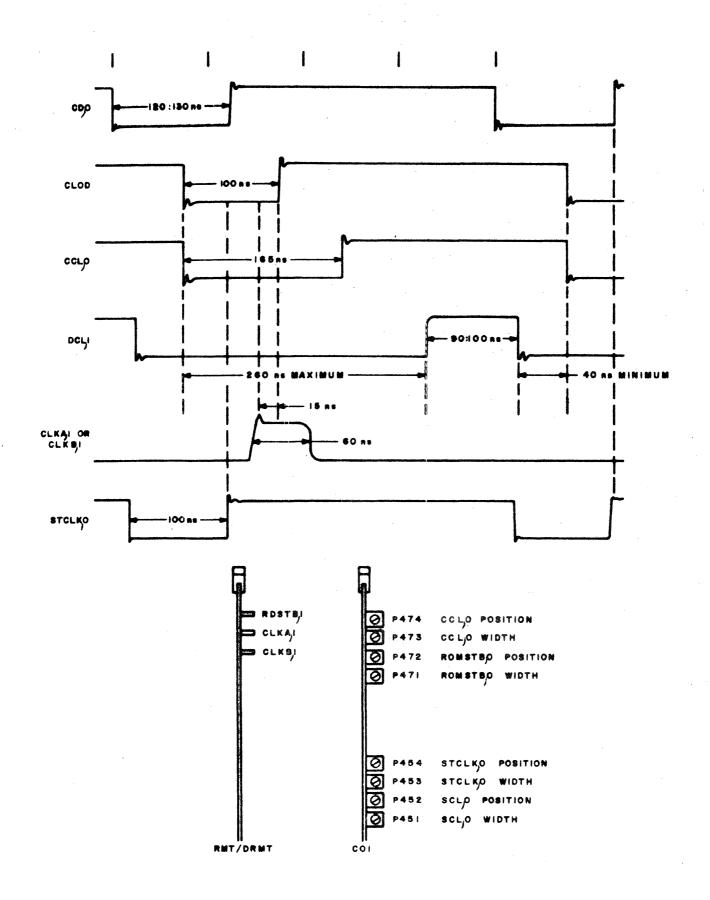

#### 3.1 Clock Control

The clock generator and the clock skipping circuits are shown on FS22-28, and are located on the CO2 mother-board. The clock system for the 30-1 employs a crystal-controlled 2.7MC oscillator. The crystal itself is mounted with a voltage divider on the daughter-board in location 37. The output from the crystal circuit feeds the oscillator in location 36, which amplifies the crystal output. The amplified sinusoidal output, OSC1 on pin 10 of the oscillator, varies between ground and +5V.

OSC1 is connected to the T input of a JK flip-flop. When the flip-flop is reset, the high output CLKOFE0 is ANDed with OSC1 to develop the RAWCLK input to the pulse shapers. When the flip-flop is set, CLKOFE0 goes low, preventing OSC1 from developing RAWCLK, and inhibiting the clock outputs. The J input of the CLKOFF flip-flop is tied to ground on the back panel. The K input is designated VP0. When the system is initialized, SCLR0 and VP0 go low. SCLR0 sets the CLKOFF flip-flop. As long as VP0 is low, the negative transition of OSC1 cannot reset CLKOFF, and clock pulses are inhibited until the initialize sequence is terminated. At this time VP0 and SCLR0 go high. CLKOFF resets on the next negative going transition of the oscillator output, enabling OSC1 to develop the RAWCLK input to the pulse shapers.

The low going result of ANDing OSG1 and RAWCLK is ORed with the normally high EXTCLK0 lead. This lead is provided so that an external clock may be used to run the system during trouble-shooting or marginal testing. This is accomplished by grounding the CLKOFE0 lead at pin 110-1 on the back panel to disable the internal oscillator, and then pulsing EXTCLK0 with a low-going output from an external oscillator. The external oscillator used should meet the following specifications:

- 1. square wave oscillator

- logic levels 0 to + 0.45 vdc for logic ZERO, 2.6 to 5 vdc for logic ONE

- 3. frequency up to 2.7 MC

- 4. output drive 6 milliamps

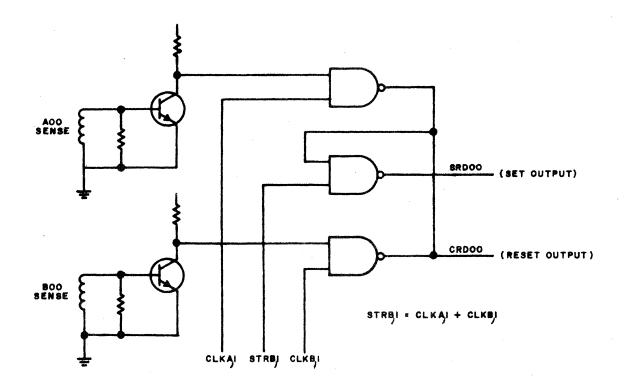

The output of the OR gate, RAWCLKO, is available at Test Point V on CO2. RAWCLK is next applied to 3 pulse shapers. The pulse shapers each contain two potentiometers. One potentiometer varies the pulse width, the other potentiometer varies the delay time. The procedure for adjusting these potentiometers is explained later is this Section. The outputs from the pulse shapers occur at the clock frequency, and are inhibited only when the system is initialized. The output from the pulse shaper in position 46 is inverted to form the Current Drive pulse (CD0) for the ROM. CD0 is available at Test Point G on CO2. The output from the pulse shaper in position 35 is ANDed with LRALO and CLKSTPO to develop STRBO, the strobe pulse for the ROM. STRBO is available at Test Point D on CO2. The output from the pulse shaper in position 44 is ANDed with LRALO and CLKSTPO to develop the system clocks, CLOD and CLOE. CLOD is available at Test Point E on CO2. CLOD is used primarily to gate data into the Processor registers. CLOE is used to gate information into the memory registers.

Two other inputs are used to develop CLOD, CLOE, and STRB0: LRAL0 and CLKSTP0. These are clock inhibits used to prevent generation of timing functions at specific times.

The normally high CLKSTB0 lead becomes active (low) when a memory operation is attempted and the memory is not ready. This inhibits the ROM strobe (STRB0) and the system clocks (CLOD and CLOE), allowing the Processor to wait for the memory operation to be completed. The CLKSTB0 signal is controlled by the two JK flip-flops shown at the top of FS22-28.

The flip-flop on the left inhibits CLOD, CLOE, and STRB0 if the micro-code program directs the Processor to unload the Memory Data Higher (MDH) or Memory Data Lower (MDL) registers after a memory cycle has been initiated and the data is not yet available. The low active, Unload Memory Data Higher (UMDH0) and Unload Memory Data Lower (UMDL0) signals are ORed and then ANDed with the set output of the JK flip-flop shown on the left. The state of this flip-flop is controlled by the Memory Data Available signal (MDAV0) coming from the core memory.

MDAV<sub>0</sub> is low if there is no memory operation in progress, or if a memory read is being executed and the readout is available in the Memory Data Register (MDR). MDAV0 resets the flip-flop, preventing it from inhibiting the clock outputs. If memory is in the first half cycle of a memory read, MDAV0 is high causing the JK to set at the trailing edge of the next system clock. If the micro-code program attempts to unload the Memory Data Register with this flipflop set, the CLKSP0 signal goes low, stopping the clock. When memory data becomes available, MDAV0 goes low, the JK flip-flop resets, and CLKSTB0 goes high, enabling clock pulses to be generated to unload the Memory Data Register.

Notice that the clock which triggers the flipflop is not inhibited by CLKSTB0. As soon as memory data becomes available, the flip-flop is reset on the trailing edge of the next pulse. Since STRB0 was inhibited by the CLKSTB0 signal, the next ROM instruction word was not read out and UMDH0 or UMDL0 remained low while the clock was stopped.

Since memory operations are asynchronous with the system clock, the flip-flop guarantees that a clock pulse will not be shortened when data becomes available.

The other JK flip-flop capable of developing CLKSTP0 also has an input from memory. This lead, Memory Busy (MBY1A), is normally low, holding the flip-flop reset. MBY1A goes high and sets the flip-flop when any memory operation is initiated, and then remains high for the full memory cycle. If the micro-code program attempts to load any memory register or initiate another read or write cycle, the LMST<sub>1</sub> lead (FS22-28J2) goes high. LMST<sub>1</sub> is ANDed with the set output of the JK flip-flop to develop the CLKSTP0 signal which prevents generation of CLOD, CLOE, and STRB0. At the conclusion of the initial memory operation, the MBY1A lead goes low, allowing the next clock pulse to reset the flip-flop. With the

flip-flop reset, CLKSTB0 goes high enabling CLOE, CLOD, and STRB0. The pending memory operation is then executed.

The other function which inhibits CLOD, CLOE, and STRBO is the LRALO function. LRALO is normally high, and goes low to stop the clock when one of the following micro-ops is being executed.

- 1. Load RAL

- 2. Branch

- 3. Add

- 4. Subtract

- 5. Unload SDR

Stopping the clock for the first two microops permits sufficient time for the new address to be decoded in the ROM decoding matrix. Stopping the clock for Add and Subtract permits sufficient time for the 'worst case" carries to propagate through the arithmetic system. Stopping the clock for the last micro-op insures sufficient time for the data register to be loaded by the returning sync pulse, following a data request.

The flip-flop shown on FS22-28C7 provides the capability of skipping one clock pulse while performing Add, Subtract, Branch, Unload SDR, or Load RAL micro-ops. The J input to the flip-flop is normally low and becomes high if any one of the five microinstructions listed previously is executed. The J input is fed by two NAND gates whose outputs are tied together. A low signal is required at the input of each gate to make the output go high. During a Branch instruction, BRA0 is low, forcing both NAND gate outputs high. During Add or Subtract, LO is low, forcing both outputs high. During a Load RAL instruction, LR140 is low, causing one NAND gate output to be high. BANKO is high forcing the other NAND gate output high. While unloading the System Data Register, USD0 is low, and forces both outputs high. The high preset on the J input of the flip-flop is ANDed with the reset output from the flipflop, which is high until the trailing edge of the next clock pulse. The output from this

gate, LRAL<sub>0</sub>, goes low and inhibits CLOE, CLOD, and STRB<sub>0</sub>. With a high on the J input to the flip-flop and the K input tied to +5 volts, the flip-flop complements on the next clock pulse. With the flip-flop set, the reset output goes low, forcing LRAL<sub>0</sub> high and once again CLOE, CLOD, and STRB<sub>0</sub> are enabled. Note, however, that one clock pulse has been skipped. LRAL<sub>0</sub> and its complement LRAL1 are also wired to the RM1 mother-board to inhibit the incrementing of RAL and enable the gates from the S Bus to RAL.

During a Branch or a Load RAL micro-op, the information is gated into RAL from the S Bus with the RA clock (RCL $\rho$ ). During Add, Subtract, or Unload SDR, RCL $\rho$  is also skipped. This is accomplished by ORing L $\rho$ and USD $\rho$  at the gate shown in area A7.

If either  $L_0$  or USD<sub>0</sub> is low, this gate produces a high output. This high is ANDed with the reset output from the flip-flop to produce a low into the gate that generates RCL<sub>0</sub>, thus inhibiting it. Notice that another input to the gate which generates RCL<sub>0</sub> is CLKSTE<sub>0</sub>. This input is used to inhibit RCL<sub>0</sub> from being generated to increment the address register during a memory clock stop sequence. During Branch or Load RAL, L<sub>0</sub> and USD<sub>0</sub> are both high inputs to the gate, forcing the output low. This low produces a high output from the gate shown in area D<sub>9</sub>, enabling RCL<sub>0</sub> to be generated

In summary, all clocks are inhibited during an initialize sequence. If a memory operation is attempted when memory is busy, or if data is not yet available from memory; CLOD, CLOE, RCLO, and STRBO are inhibited. If a Branch or Load RAL is executed, CLOD, CLOE, and STRBO skip one pulse. If an Add, Subtract, or Unload SDR is executed; CLOD, CLOE, STRBO, and RCLO all skip one pulse.

#### 3.2 Initialize Control

The Initialize Control logic is shown on FS22-27. This logic provides an orderly system shutdown when the system is initialized. When an initialize sequence occurs, the following actions take place:

- 1. Stop Clock

- 2. Reset RAL

- 3. Reset RAH

- 4. Reset DFR

- 5. Reset Bank flip-flop

- 6. Reset Utility flip-flop

- 7. Reset RD

- 8. Reset SCR

- 9. Provide Reset Signals for Memory and I/O

- 10. Set Wait Alarm

The system is initialized as a result of one of the following conditions:

- 1. INITIALIZE Switch depressed

- 2. Command Power Off

- 3. AC Input (optional), P15, N15, or P5 falls below minimum operating level

The master reset signal, SCLR1, is active whenever the initialize relay is released by the PDOWN0 signal generated at FS22-27F5. During normal operating conditions, PDOWN0 is high, permitting the Darlington circuit controlling the initialize relay to conduct, and keeping the relay energized. PDOWN0 goes low to start an initialize sequence whenever one of the three conditions mentioned previously occurs.

When the normally open INITIALIZE Switch (H1) is depressed, a ground level sets the STPSYS1 flip-flop (G4 - H4). The 470 Pf capacitor and 1K pull-up resistor filter the higher frequency components of the switch bounce.

The STPSYS1 flip-flop is also set if a Command Power Down is executed. The Processor tests for Primary Power Fail between execution of each user instruction. The test micro-instruction sets the Greater Than flag in the DO Flag register, if the latching POWER Switch is released or if the optional Primary Power Fail Detector determines that the AC voltage is lost. If the Greater Than flag is set upon conclusion of the Test micro-instruction, the micro-code program transfers to a Command Power Down. The Command instruction generates the low signal POW0 at FS22-24N4. POWJ0 causes the STPSYS1 flip-flop to set.

When the STPSYS flip-flop sets, PDOWN0 goes low. When PDOWN0 goes low, it removes the positive potential on the input of the Darlington circuit, causing it to turn off, and thus de-energizing the Initialize relay. The reset output from the STPSYS flip-flop generates the signal VP1, area R6. VP0 goes low and holds the K input to the CLKOFF flip-flop (FS22-28K4) low, preventing it from ' setting until the initialize sequence is terminated.

The third instance when PDOWN goes low to remove the positive potential from the input to the Darlington circuit and drop out the Initialize relay, is when one of the voltages, +5v, +15v, -15v, or the AC input is lost. If the N15 supply voltage is lost, the output from the gate in area F5 goes low and drives PDOWNO low. If the +5v is lost, the collector supply for the Darlington circuit is removed, causing the Initialize relay to drop out.

If the AC input is lost, the PDOWN0 lead is also forced low, causing the Initialize relay to drop out. The AC input is sampled from the secondary of a 12VAC transformer and rectified. The pulsating DC voltage is applied to Potentiometer P473 (area E3). The potential picked off by the potentiometer is applied to the optional Power Fail Detector. The following description of the Primary Power Fail Detector assumes that the two transistors on the 35-063 daughter-board are Q1 and Q2 left to right, and that the two transistors on the 35-082 daughter-board are Q3 and Q4 left to right.

Initially, Transistor Q1, Q3 and Q4 are off and Transistor Q2 is conducting. With Transistor Q2 conducting, a high enough positive potential on the base of Q4 keeps Q4 cut off, and applies about +6v to the emitter of Q1. The potential picked off Potentiometer P473 (approximately 8v) is applied to the base of Q1. If the AC input is lost, or fluctuates enough, the potential on the base of Q1 becomes more negative and Q1 conducts.

When Q1 conducts, it places a positive potential on the base of Q3, turning Q3 on. This causes the potential on the emitter of Transistor Q2 to become less positive, turning Q2 off. When Q3 conducts, its collector goes to ground, generating the low signal PPE0. PPE0 is tested between execution of user instructions to determine if a Power Fail is in progress.

When Transistor Q2 turns off, the positive potential is removed from the base of Q4. Transistor Q4 then conducts, grounding the PDOWNO lead, turning the Darlington circuit off, and dropping out the Initialize relay. The Initialize relay, which is a dry reed relay with SPDT contacts, is shown with the relay not energized.

When the relay releases, the SCLR1 contact opens, causing SCLR1 to go high. This removes the ground for the POWER lamp. The SCLR0 contact goes to ground. This metalic ground sets the Wait Alarm, resets, DFR, and is distributed to memory and I/O for initialize controls. SCLR0 also holds VB0 at ground to inhibit the clock. SCLR<sub>0</sub> is inverted through the gate in area K6. This node will rise to +5 with a time constant determined by the 19-004 internal resistor and the 33uf capacitor. When SCLR<sub>1</sub> reaches the input threshold of the four gates it feeds, it turns them on, causing the outputs to go low. The output SCLR<sub>0</sub>A resets RAS, RAH, and RAL. SCLR<sub>0</sub>B resets RD, and SCLR<sub>0</sub>C resets the Bank and Utility flip-flops. When the remaining gate (area N7) goes low, its output resets the STPSYS flip-flop and holds VB0 at ground.

When the STPSYS flip-flop is reset, the STPSYS0 input to stop the system clock, goes high. Resetting the flip-flop also removes the ground on the input to the Darlington circuit if the Initialize sequence resulted from depressing the INITIALIZE Switch. This allows the 66uf capacitor to clowly charge. When the threshold of the input transistor is reached, the Darlington circuit turns on, and energizes the relay.

When the SCLRJ contact closes, it provides the ground return for the POWER lamp. The SCLRJ contact opens and removes the reset functions for DFR, memory, and I/O controllers; and removes the set signal on the Wait Alarm. When this occurs, the output from the gate at K6 goes to ground immediately. This removes the reset signals SCLRJA, SCLRJOB, and SCLRJC. The output from the gate at N7 will have to charge up the 33uf capacitor. This delayed function removes the reset on the STPSYS flip-flop, and also removes the final clock inhibit.

The previous description applies for a Command Power Off, or manual Initialize, since these are the only sources to set the Initialize flip-flop.

For the case where Initialize is caused by a failure of P5, N15, P15, or Power is removed, the relay de-energizes and remains in that state until the fault is corrected. When power is turned on, the system is initialized in an orderly fashion by the following mechanism. The SCLRO contact of the relay stays at ground enabling the reset signals SCLROA, SCLROB, SCLROC. This holds the clock off initially. As the P5 reaches normal operating levels, the Initialize flip-flop is reset after a delay. This insures that the PDOWNO node is not forced to ground and permits the 66 uf capacitor at the input to the Darlington to charge slowly. The relay then energizes.

#### 3.3 Processor Registers

The Processor executes micro-instructions received from the ROM. This is accomplished, primarily, by moving data from one place to another and modifying it in the ALU. In order to manipulate data and execute the instructions received, the Processor uses a number of internal registers. Most of these are eight bit registers. Some registers perform special functions, but most are general purpose. Data is transferred between registers and other system elements via the eight bit B and S Buses in the Processor. Each register is described in the following paragraphs.

3.3.1 ROM Data Register. The ROM Data Register (RD) is a 16-bit register located on the ROM Interface board (RMI). The schematic drawings for this register are on FS44 - 1:3. The ROM Data Register can be thought of as an instruction register. Each bit of RD has double rail inputs from the ROM. Every micro-instruction extracted from the Read-Only-Memory is placed into the RD register, where it remains while the instruction is executed. A thorough knowledge of the ten basic micro-instructions and their instruction word formats is necessary to fully understand the RD register. (See the Micro-Instruction Reference Manual, Publication Number 29-017R01 for a detailed explanation.)

In most instances bits 0-3 of RD are decoded as the op-code of the micro-instruction being executed. RD3 = 1 defines Immediate instructions. An Immediate instruction is one that has the specific data to be manipulated appended to the instruction word itself. During the performance of an Immediate instruction, bits 8:15 of RD are gated onto the B Bus and treated as data, instead of being decoded as Source and Extended Fields, Test Code, or Command Code. The only instance when RD (0:3) is not used to determine the micro-instruction to be performed, is during execution of a DO instruction. During a DO instruction, bits 0:2 of the DO Flag Register are decoded as the op-code. Since bit 3 of the DO Flag Register is not decoded, it is impossible for the DO instruction to cause an Immediate instruction to be executed.

Bits 4:7 are normally decoded as the destination register address. This identifies the register designated to contain the result upon completion of the micro-instruction being performed. When a Branch instruction is executed, bits 4:7 define the condition that the Processor will branch on. If the Processor decodes a Test or Command instruction, bits 4:7 are part of the Command or Test Code.

Bits 8:11 are decoded as the source register address for micro-instructions in the Register to Register format. The Source register contains one of the operands to be used. If a Branch instruction is decoded, bits 8:11 are part of the branch address. If the Command or Test micro-op is decoded, bits 8:11 are decoded as part of the Command code. If an immediate instruction is decoded, bits 8:11 are part of the data.

Bits 12:15 normally make up the extended field for Register to Register instructions and are decoded to specify options for specific instructions. The extended field designates the function of carry, whether to shift or complement the operand manipulated, whether to set flags, or whether to enable the A Register input to the ALU. During other instructions, bits 12:15 are part of the Command code, or data.

Other than the double-rail inputs from the ROM. the only other input to the RD register is SCLROB. SCLROB goes low and clears the entire RD register when the system is initialized. The set and reset outputs from RD 0:2 are inputs to individual power gates. During all micro-instructions except DO, these gates reflect the contents of bits 0:2 in RD. When RD 0:3 contains 0000 (the opcode for a DO instruction), the output from the gate in area A5 of FS44-1, goes low. This low forces DRD001, DRD011, and DRD021 high. With a DO instruction in RD, the output from the four OR tied power gates shown on the right hand side of the page goes high, enabling the state of DO Flag Register bits 0:2 to be reflected in the DRD outputs. All of the outputs from the bits in the RD register appear directly in the Control logic so that the various op-codes and options can be decoded and the proper gating leads to the ALU can be activated. The set outputs of RD bits 8:15 feed individual power gates that generate the false B Bus outputs (low if a logic 1) if RD 03 is set, indicating an Immediate instruction.

3.3.2 <u>ROM Address Lower</u> <u>Register</u>. The ROM Address Lower Register (RAL) is an 8 bit register that contains the least significant portion of the address of the location to be extracted from the Read-Only-Memory. The schematics for RAL are located on FS44-4 and 5.

During performance of the major portion of the micro-program, micro-instructions are selected from successive locations in the Read-Only-Memory. The RAL register is wired as a standard up-counter to facilitate the selection of successive locations. The RAL is incremented to read successive ROM locations except during a Branch micro-instruction when the specified condition is true, or if RAL is designated as a Destination Register. In either of these cases, the RAL increment signal is disabled and the new address is loaded into RAL from the S Bus.

The RAL register is cleared by the SCLR0A signal when the system is initialized. The RCLO signal is used to increment the RAL register or to gate the information from the S Bus into RAL. The RCLO signal is inverted and applied to the T input of each flip-flop in RAL as RCL1. If a Branch or a Load RAL instruction is performed, LRALO is low and LRALI is high. LRALI is NANDed, bit for bit, with the S Bus to enable the J and K inputs to each of the flip-flops in the RAL register. If any inputs from the S Bus are high, the K input is forced low and the J input is forced high on the corresponding bit in the RAL register, causing it to set at clock time. If an S Bus input is low, the K input is forced high and the J input is forced low, causing the RAL flip-flop to reset.

When the Processor is not executing a Branch or Load RAL, LRAL0 is high and LRAL1 is low. With LRAL1 low, the inputs from the S Bus are disabled and the RAL register is incremented by one on each negative transition of RCL1. The RAL is incremented by complementing each bit of the register if all previous least significant bits are set. RAL07 complements every time. RAL06 complements if RAL07 is set. RAL05 complements if RAL07 and RAL06 are both set and so on. This is accomplished by NANDing the set output of each flip-flop with all previous bits to enable the J and K inputs for the next significant bit. If all previous bits are set, the J and K inputs to the next stage are high, allowing that bit to complement. If any of the previous bits are not

set, the J and K inputs are low, preventing that flip-flop from changing state.

3.3.3 ROM Address Higher

Register. The ROM Address Higher Register (RAH) is shown on FS44-6. RAH is a 4-bit extension of RAL which increases the ROM addressing capability to 4096 locations. This register is independent of the RAL register from both the programming and the hardware viewpoint. RAH holds the ROM page address and RAL holds the ROM location address. RAL is normally incremented to fetch micro-instructions from successive ROM locations. When RAL is equal to its highest address (hexadecimal FF), the next increment pulse causes it to recycle to an address of all zeros, but no carry is propagated into the least significant bit of RAH. For this reason RAH must be loaded independently each time a Branch or Load RAL selects a different page.

The RAH register is composed of RS flipflops with single-to-double rail converters on the inputs. This register has inputs only from the S Bus. A new address is loaded in RAH at clock time from the S Bus when RAH is specified as the Destination register of a Load instruction. To address the RAH register, the Bank flip-flop must be reset. Signal LRA1 gates the contents of the S Bus into RAH. LRA1 is developed by the three inverters whose outputs are AND tied in the upper left hand corner of Sheet 6. The input: to the three inverters are RCLO, BANK1 and LRAHO. BANK1 is low when the BANK flipflop is reset. RCL0 varies with the system clock. LRAH0 is low when the destination address decoder decodes the address X'D'. When the three inputs are low, LRA1 goes high, gating the S Bus into RAH. The only other input to RAH is SCLR0A. SCLR0A is normally high and becomes low to clear the RAH register when the INITIALIZE button on the Display Panel is depressed, a Power Down command micro-instruction is executed, or the power is turned off.

3.3.4 <u>ROM Address Slave Register</u> <u>ter (RAS)</u>. The ROM Address Slave Register is a 4-bit register shown on FS44-6. RAS is slaved to the 4-bit RAH register. The single rail buffered outputs of RAS are decoded as the four most significant bits of the page of the ROM address to be selected.

The contents of RAH are loaded into RAS every time RAL is loaded from the S Bus. This allows the correct page address to be loaded into the RAH register prior to a Branch or Load RAL micro-instruction. When RAL is loaded with a new address as a result of executing a Branch or a Load RAL, the correct page is gated into RAS from RAH. In this way all 12 bits of the new ROM address arrive at the ROM address decoder simultaneously (allowing for slight variations in the circuit delays).

LRAS1 gates RAH into RAS. LRAS1 is developed by the two inverters collector AND tied on the left hand side of Sheet 6. The two inputs are RCL0 and LRAL0. LRAL0 is the signal used to gate the S Bus into RAL. LRAL0 is low during a Branch or a Load RAL micro-instruction. When LRAL0 is low, LRAS1 varies with RCL0 and gates RAH into RAS on the negative transition.

The only other input to RAS is the normally high SCLR0A signal which goes low when the system is initialized to clear RAS. SCLR0A is the same signal that clears RAL.

#### 3.3.5 DO Flag Register (DF).

The DO Flag Register (DF) is an 8-bit register located on the BS1 and BS2 mother-boards. The schematic drawings are on FS22-10:12. The DF register is a general purpose register in addition to being the memory for flags indicating the results of instructions, and the source of op-codes during performance of DO micro-instructions.

The DF register is cleared by the SCLR0 signal. SCLR0 goes low when the system is initialized. SCLR0 is connected to the C inputs of the DF register flip-flops and jams them all into the reset state when it goes low. When the DF register is used as a General Register, it is loaded with the contents of the S Bus or unloaded onto the B Bus. When the hexadecimal address F is decoded in the destination address coder, LDF,0 becomes low and LDF,1 becomes high. LDF,1 is NANDed with each bit of the S Bus. If any bit of the S Bus is high, the K input on the corresponding bit in the DF register goes low and the J input high, allowing the flip-flop to set on the next negative going clock transition. If the S Bus input is low, K goes high, and J goes low, allowing the flip-flop to reset.

Since the DF register is used to hold the flags indicating the result of micro-instructions, there are instances when individual bits will be set or reset independently. To facilitate this independence, different gating pulses are developed for individual bits. When the DF register is loaded from the S Bus, LDE0 is used to generate all of the enables.

The DF register is unloaded onto the B Bus when the Source Register Decoder decodes the hexadecimal address F, causing the signal UFD1 to go high. UFD1 is NANDed with the set output of each bit of the DF register to generate the B Bus leads B000-B070. If any bit of the DF register is set, the corresponding bit on the B Bus goes low. Conversely, any bit of the DF register that is reset causes the corresponding bit on the B Bus to go high. The B Bus is a false bus and carries logic ONEs as low signals, and logic ZEROs are high signals.

The set and reset outputs of DF register bits (0:2) are direct inputs on the RM1 motherboard for use during execution of a DO instruction. (Reference FS44-1.) During a DO instruction, the op-code is taken from DF bits 0:2 instead of from the ROM data register. DF03 is not gated to RMI; thus immediate instructions cannot be implemented through the use of the DO instruction.

In addition to being loaded from the S Bus, DF register bit 4 is used as the Carry Store flip-flop (C). DF04 is set or reset to reflect whether or not a carry or borrow resulted upon conclusion of an Add or Subtract micro-instruction, or to reflect the state of the bit shifted out following a Load microinstruction designating the shift left or a shift right option. The gates which control setting or resetting DF04 are shown on  $\Sigma$ S22-10.

PT04 is set when the signal SDF40 is low. SDF40 is generated by three NAND gates collector OR tied. The inputs to the first NAND gate are SVSC1, SR, and B071. SVSC1 is developed on the Control motherboard (FS22-25). SVSC1 will be high and SVSC0 low if the Processor decodes a Load micro-instruction and ROM data register bit 15 is set, indicating that the carry out of the ALU is desired. SR1 will be high when the Processor is doing a Load microinstruction and the E field specifies a shift right option. B071 will be high if the least significant bit of the data present on the B Bus is a logic ONE.

The second NAND gate capable of driving SDF4,0 low has the inputs SVSC,1, SL,1, and B001. SVSC1 was just discussed. SL1 is high if the Processor is performing a Load micro-instruction whose E field designates the shift left option. B001 is high if the most significant bit of the information carried on the B Bus is a logic ONE. The third instance when SDF4,0 is low occurs when SVAC1 and CSV1 are both high. SVAC1 is high during an Add or Subtract, if the E field designates the carry out of the ALU option. CSV1 is high if a final carry or a borrow resulted during Add or Subtract. SDF40 is applied to the K input of DF register bit 4, and inverted as an input to the J input. The gating pulse is developed by SVAC0 and CLOD during Add or Subtract operations, and by SVSC0 during Load instructions with shift options.

DF register bit 5 serves as the Overflow flag (V). The gating which controls setting or resetting DF05 is shown on Sheet 10. DF05 is set when SDF50 is low. SDF50 is generated by two NAND gates collector OR tied. One of the inputs to both NAND gates capable of generating SDF50. STF50 is generated on FS22-25. STE0 is low when the Processor is performing any instruction that is not a Test, Load, or Immediate instruction, and bit 13 of the E field of the instruction word is set specifying the Set Flags option. STE0 is inverted and NANDed with L1 to generate the low signal STFL0 during Add and Subtract.