A Mini-Based Computer System

# GENERAL DESCRIPTION

GET-6227 5/72 (1M) \$4.50

A Mini-Based Computer System

# GENERAL DESCRIPTION

General Electric reserves the right to make changes in the equipment or software, and its characteristics or functions, at any time without notice.

Copyright (C) 1971, 1972 by General Electric Co.

# TABLE OF CONTENTS

- SECTION 1 INTRODUCTION

- 1.1 MAJOR FEATURES OF THE GE-PAC\* 3010/2 COMPUTER SYSTEM

- 1.2 SCOPE

- REFERENCES 1.3

- SECTION 2 SOFTWARE

#### SECTION 3 GENERAL INFORMATION

- 3.1 ENVIRONMENTAL SPECIFICATION

- 3.2 INPUT POWER

- 3.2.1Peripheral Devices

- 3.2.2 Process I/O Termination Cabinets

- 3.2.3 Drum Cabinet

- 3.3 CABLING

- 3.4 CONSTRUCTION

- 3.4.1 Cabinets

- 3.4.2 Printed Wire Boards

- 3.4.3 Modularity

- 3.4.4 Maintainability

## SECTION 4 CENTRAL PROCESSOR

- DATA AND INSTRUCTION WORD 4.1 FORMATS

- 4.2 FUNCTIONAL DESCRIPTION

- 4.2.1 Principal Processor Components

- 4.3 CORE MEMORY

- 4.3.1 Core Memory Format and Addressing

- 4.3.2 Parity Option

- 4.3.3 Automatic Memory Protect Option

- 4.4 INTERRUPTS

- 4.4.1 Protect Mode

- 4.4.2 I/O Interrupts

- 4.4.3 External Interrupt Module

- 4.5 PROGRAMMING AND MAINTENANCE CONTROL CONSOLE

- 4.5.1 Function Switches

- 4.5.2 Data Switches

- 4.5.3 Initialize Switch and Keyswitch

- 4.5.4 Wait State

- 4.6 INPUT/OUTPUT SUBSYSTEM

- 4.7 POWER FAILURE DETECTION AND AUTOMATIC RESTART OPTIONS

\*Registered Trademark of General Electric Company

| 4.8       | SYSTEM ALARMS OPTION                         |

|-----------|----------------------------------------------|

| 4.8.1     | Stall Alarm                                  |

| 4.8.2     | Hardware Alarm                               |

| 4.8.3     | Relay Driver Outputs                         |

| 4.9       | UNIVERSAL CLOCK                              |

| 4.9.1     | PIC Operating Sequence                       |

| 4.9.2     | External Clock                               |

| 4.9.3     | LFC Operating Sequence                       |

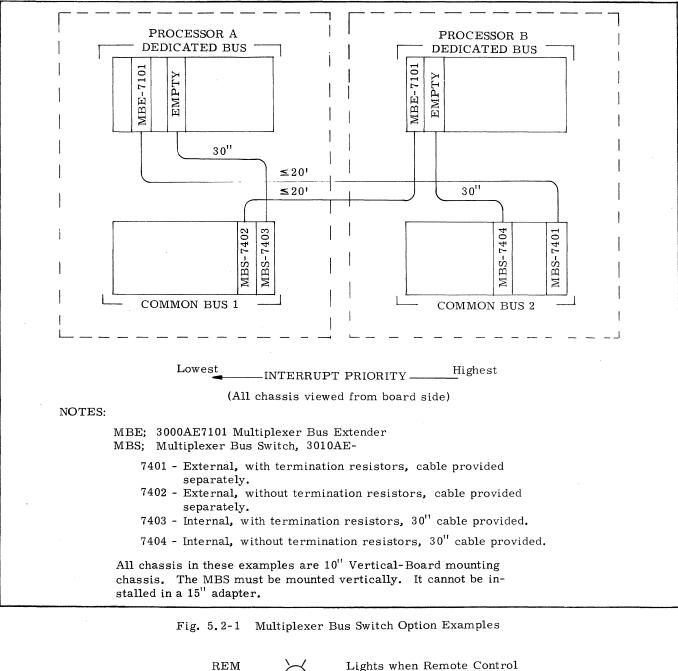

| SECTION 5 | MULTIPLEXER BUS EXTENSION AND<br>SWITCHING   |

| 5.1       | BUS EXTENSION                                |

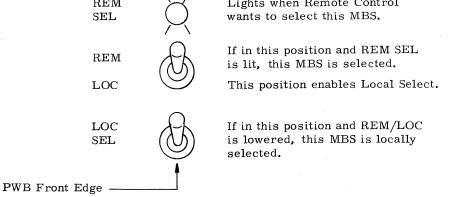

| 5.2       | MULTIPLEXER BUS SWITCHING                    |

| 5.2.1     | MBS Options                                  |

| 5.3       | SELECTOR CHANNEL BUS EXTENSION AND SWITCHING |

| 5.4       | CENTRAL PROCESSOR FAILURE<br>RECOVERY        |

| SECTION 6 | SELECTOR CHANNEL                             |

| 6.1       | FUNCTIONAL DESCRIPTION                       |

| 6.2       | OPERATING SEQUENCE                           |

| 6.2.1     | Initialization                               |

| 6.2.2     | Status Sensing                               |

| 6.2.3     | Output Commands                              |

| 6.2.4     | Transfer Sequence                            |

| 6.2.5     | Termination                                  |

| 6.2.6     | Final Address Verification                   |

| 6.2.7     | Selector Channel Address                     |

| SECTION 7 | DRUM MEMORY                                  |

- 7.1

- FUNCTIONAL DESCRIPTION

- 7.2 PRINCIPAL FEATURES

- 7.2.1 Average Access Time

- 7.2.2 Accuracy

- 7.2.3 Start Time

- 7.2.4 Transfer Rate

- 7.2.5 Write Protection

- 7.2.6 Parity Check

#### 7.3 OPERATING SEQUENCE

| 7.3.1     | Initialization                     |

|-----------|------------------------------------|

| 7.3.2     | Status                             |

| 7.3.3     | Output Commands                    |

| 7.3.4     | Drum Starting Address              |

| 7.3.5     | Device Address                     |

|           |                                    |

| SECTION 8 | DISC MEMORY                        |

| 8.1       | FUNCTIONAL DESCRIPTION             |

| 8.2       | PRINCIPAL FEATURES                 |

| 8.2.1     | Access Times                       |

| 8.2.2     | Start Time                         |

| 8.2.3     | Transfer Rate                      |

| 8.2.4     | Write Protection                   |

| 8.2.5     | Parity Check                       |

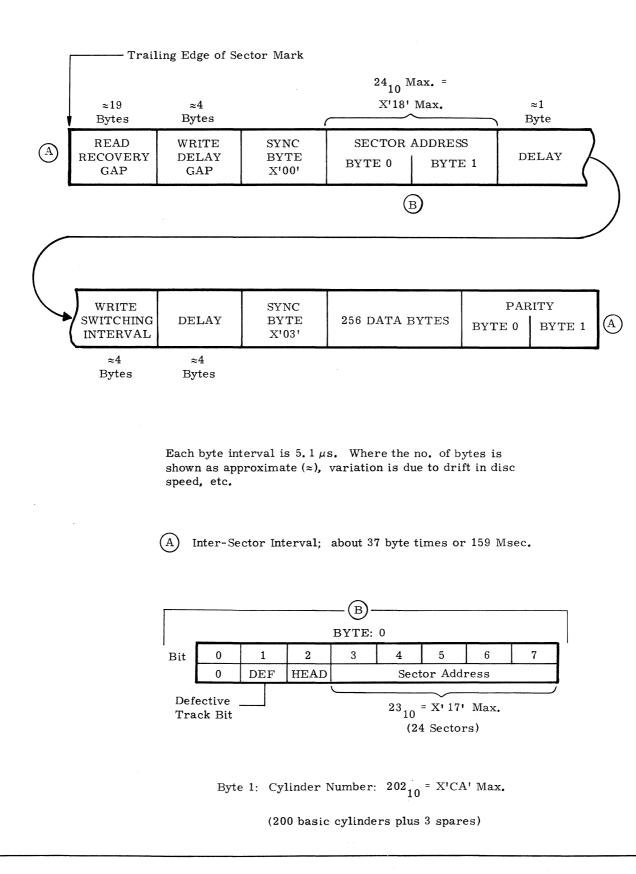

| 8.2.6     | Sector Format Writing and Checking |

| 8.2.7     | Environment                        |

| 8.3       | OPERATING SEQUENCE                 |

| 8.3.1     | Cylinder Seek                      |

| 8.3.2     | Transfer Sequence                  |

| 8.3.3     | Device Addresses                   |

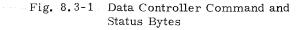

| 8.3.4     | Output Commands to Data Controller |

| 8.3.5     | Data Controller Status             |

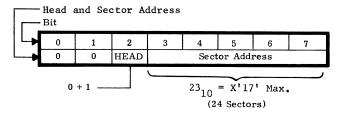

| 8.3.6     | Sector Address to Data Controller  |

| 8.3.7     | Data Byte From Data Controller     |

| 8.3.8     | Output Commands to Disc Unit       |

| 8.3.9     | Disc Unit Status                   |

| 8.3.10    | Disc Subsystem Interrupts          |

|           |                                    |

| SECTION 9 | MAGNETIC TAPE SUBSYSTEM            |

| 9.1       | FUNCTIONAL DESCRIPTION             |

| 9.1.1     | Options                            |

| 9.2       | PRINCIPAL FEATURES                 |

| 9.2.1     | Tape Speed                         |

| 9.2.2     | Transfer Rate                      |

| 9.2.3     | Tape Supply                        |

| 9.2.4     | Parity Checking                    |

| 9.2.5     | Environment                        |

| 9.3       | OPERATING SEQUENCE                 |

| 9.3.1     | Device Address                     |

| 9.3.2     | Output Commands                    |

| 9.3.3     | Status Sensing                     |

| 9.3.4     | Data Transfers                     |

| 9. | З. | 5 | Interrupts |

|----|----|---|------------|

|----|----|---|------------|

### SECTION 10 PERIPHERAL DEVICES

| 10.1   | TYPERS                 |

|--------|------------------------|

| 10.1.1 | TermiNet* 300 Printers |

| 10.1.2 | Teletypewriters        |

| 10.2   | PAPER TAPE PUNCH       |

| 10.3   | PAPER TAPE READER      |

| 10.4   | CARD READER            |

| 10.5   | CARD PUNCH             |

| 10.6   | LINE PRINTER           |

|        |                        |

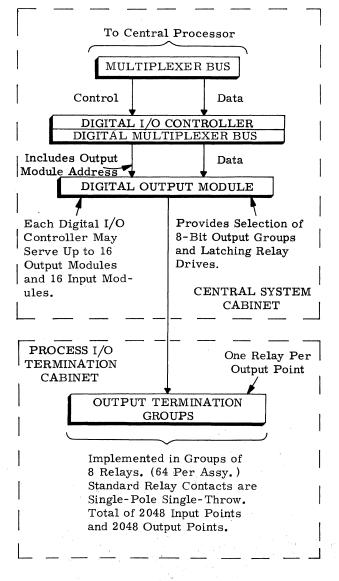

## SECTION 11 DIGITAL I/O SUBSYSTEM

| 11.1 PRI | IMARY | DIGITAL | [/0 | SUBS | YSTEM |

|----------|-------|---------|-----|------|-------|

|----------|-------|---------|-----|------|-------|

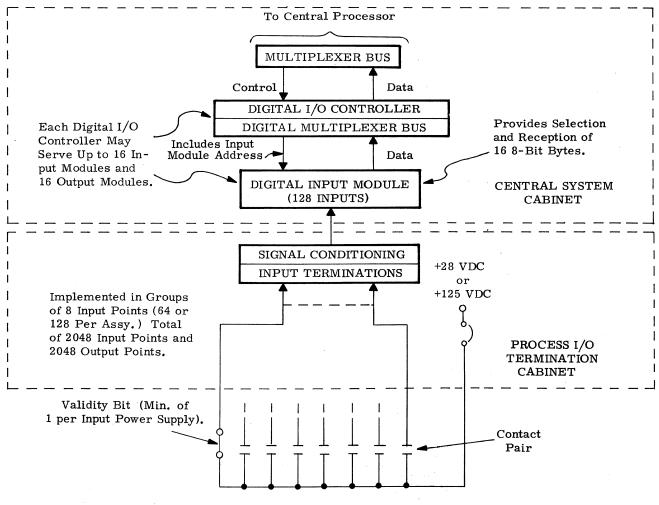

- 11.1.1 Digital Inputs

- 11.1.2 Digital Outputs

- 11.1.3 Digital I/O Operating Sequence

- 11.2 SMALL DIGITAL I/O SUBSYSTEM

- 11.2.1 Sense Line Module Inputs

- 11.2.2 Control Line Outputs

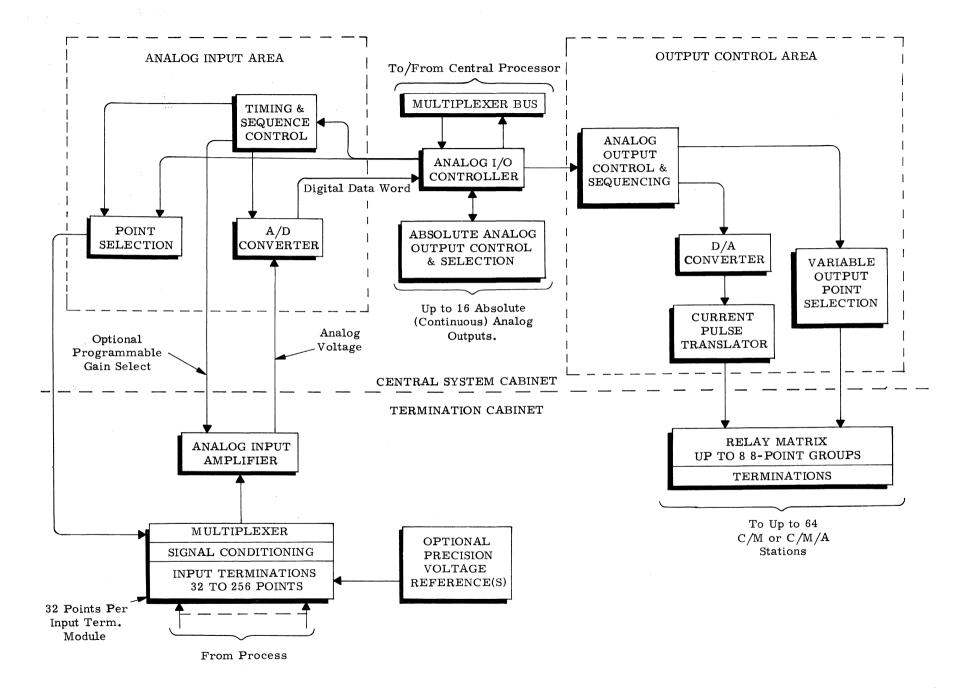

## SECTION 12 ANALOG INPUT/OUTPUT SUBSYSTEM

| 12.1   | ANALOG INPUTS              |

|--------|----------------------------|

| 12.1.1 | Analog Input Parameters    |

| 12.1.2 | Amplifier and Gain Options |

| 12.1.3 | Analog Input Terminations  |

| 12.2   | ABSOLUTE ANALOG OUTPUTS    |

| 12.3   | VARIABLE OUTPUTS           |

| 12.3.1 | Control Station Interface  |

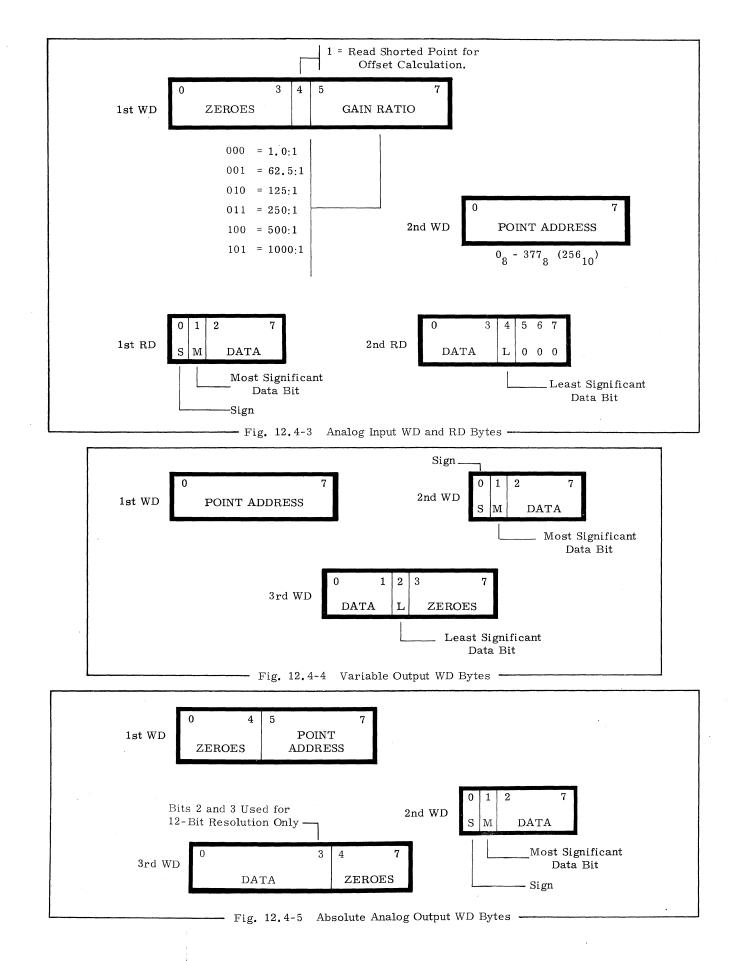

- 12.4 ANALOG I/O SUBSYSTEM OPERATING SEQUENCES

- 12.4.1 Analog Input Mode

- 12.4.2 Variable Output Mode

- 12.4.3 Absolute Analog Output Mode

#### SECTION 13 ALPHA-NUMERIC VIDEO DISPLAYS

- 13.1 OPTIONS

- 13.1.1 Display Controller Units

- 13.1.2 Display Terminals

- 13.2 OPERATIONAL FEATURES

- 13.2.1 Message Formats

\*Registered Trademark of General Electric Company

### SECTION 14 REMOTE COMMUNICATIONS

| 14.1 SYNCHRONOUS | DRIVE INTERFACE |

|------------------|-----------------|

|------------------|-----------------|

- 14.1.1 Speed

- 14.1.2 Data Format

- 14.1.3 Data Link Synchronization

- 14.1.4 SDI Operating Sequences

- 14.2 HIGH SPEED DATA LINK

- 14.2.1 Data Format

- 14.2.2 HSL Operating Sequences

- 14.3 GE-TAC\* COMMUNICATIONS COUPLER

- 14.3.1 Data Format

- 14.3.2 Speed

- 14.3.3 Operating Sequence

- 14.4 TELEMETRY COMMUNICATIONS COUPLER

- 14.4.1 Data Format

- 14.4.2 Speed

- 14.4.3 Operating Sequences

- 14.5 ASYNCHRONOUS DATA SET ADAPTERS

- 14.5.1 Data Format

- 14.5.2 Speed

- 14.5.3 Parity Option

- 14.5.4 Operating Sequence

#### APPENDIX A

ANALOG I/O SUBSYSTEM - DEFINITION OF TERMS

\*Registered Trademark of General Electric Company

#### **SECTION** 1

This manual contains a functional description of the GE-PAC\* 3010/2 process computer system, including all standard functional subsystems and options.

# 1.1 MAJOR FEATURES OF THE GE-PAC 3010/2 COMPUTER SYSTEM

The GE-PAC 3010/2 is a fully modular, cost/performance optimized, process computer system. The experience gained in producing the larger and more powerful GE-PAC 4000 series of process computers has led to the development of smaller and less expensive systems - the GE-PAC 3010 and the GE-PAC 3010/2. The 3010/2 offers functions and capabilities similar to the 3010, but utilizes a more modern, smaller, faster, and more powerful Central Processor.

The GE-PAC 3010/2 Central Processor features up to 65, 536 bytes of random access Core Memory, a powerful processor which implements a set of 113 instructions plus automatic housekeeping and I/O operation, an interrupt structure and I/O interface which may serve up to 255 device and process I/O controllers, a Control Console which allows programming and maintenance personnel to observe and control the Central Processor operations, and a built-in I/O teletypewriter interface. The physical size, complexity, and cost of the Processor are reduced through the use of a solid state non-volatile Read-Only Memory (ROM). The ROM contains a micro-program which emulates the 113 user instructions and performs the housekeeping and automatic I/O sequences.

The user instructions include full subsets of fixed point and floating point arithmetic instructions, shift instructions, list processing instructions, branch instructions, logical instructions, and the Supervisor Call instruction. Supervisor Call is used by the application programs to interface with the operating system, RTMOS-30. The GE-PAC 3010/2 is upwardly program compatible with the GE-PAC 30-1, 30-2, 30-2E, and the 3010. Programs which run on these earlier machines will run on the 3010/2 with little or no modification, and at increased speed.

User instructions which address Core Memory may specify any address up to the maximum of 64K bytes, and no paging or indirect addressing is required. The core cycle time is 1.0 microsecond.

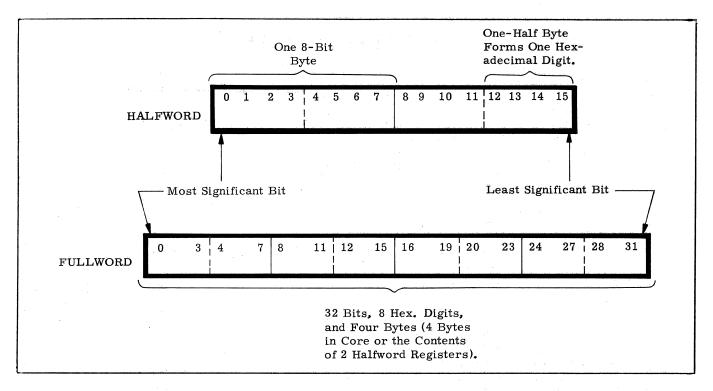

Sixteen hardware registers are available for temporary data storage and 15 of these registers may be used for indexing. The hardware registers store 16-bit halfwords. Thirty-two core locations are reserved as floating point arithmetic registers. These locations provide storage for eight 32-bit fullwords.

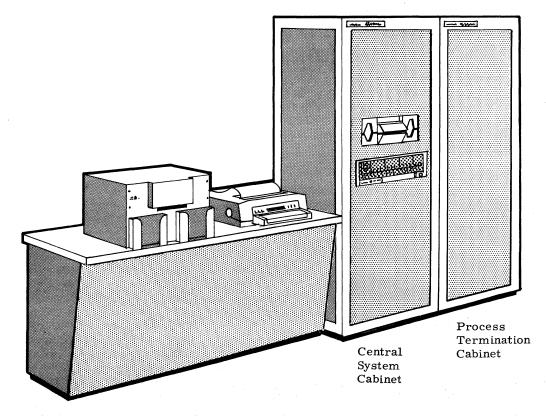

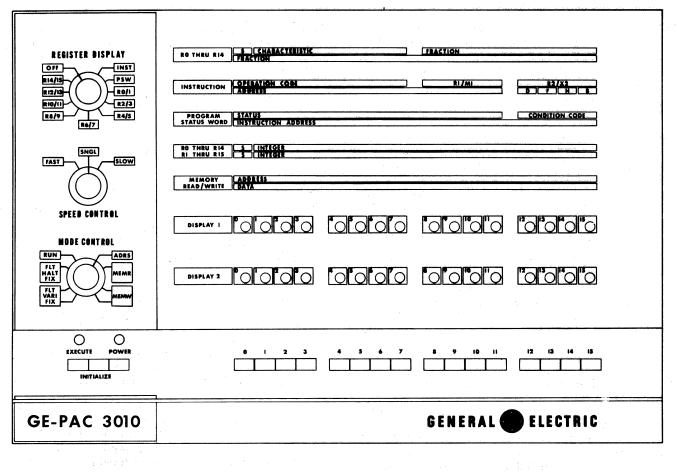

Fig. 1.1 GE-PAC 3010/2 Process Computer

Registered Trademark of General Electric Company

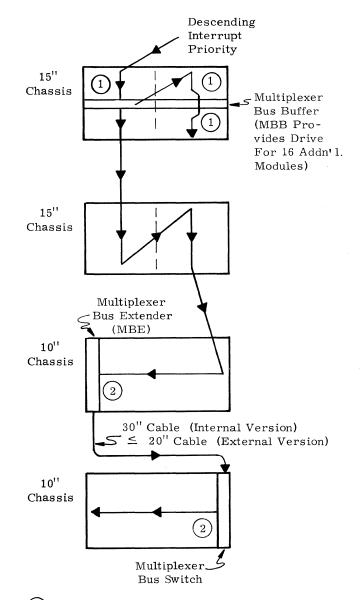

The principal interface between the Processor and the device and process I/O controllers is the Multiplexer Bus. Any controller may be implemented merely by plugging it into an available slot on the Multiplexer Bus and removing one jumper wire from the back panel. Interrupt priority for the controllers decreases as they are implemented in positions which are more distant from the Processor, so the controllers whose timely operation is more critical to the overall system operation are assigned positions nearer the Processor.

All optional system functions are fully modular and may be installed in the factory or in the field. A full line of peripheral devices, including typers, punches, readers, and video displays is available. The process I/O subsystems are capable of serving up to 2048 digital inputs, 2048 digital outputs, 256 analog input points, 16 absolute analog outputs, and 64 variable outputs to C/M or C/M/A stations. Additional process digital and/or analog I/O subsystems may be added to increase this capability.

# 1.2 SCOPE

This document defines the GE-PAC 3010/2 Computer System and its functional features. The features and performance of each module and subsystem available in the 3010/2 Computer System are described. The actual contents of any individual 3010/2 Computer System are described on the procurement documents for that system. General Electric reserves the right to modify at any time without notice to Customer the contents of this document or the design or functions of the system or any part thereof for reasons of improved performance and operational flexibility. If any conflicts exist between this General Description and General Electric Company's applicable Functional Design Specifications, the latter will take precedence. In a given transaction between General Electric Company and a customer, the provisions of the contract document will supercede this General Description and define General Electric Company's obligation to the customer.

# **1.3 REFERENCES**

A detailed functional description of the Central Processor is provided in the GE-PAC 3010/2 Central Processor Reference Manual, GET-6047. That manual describes Core Memory, the Processor, the Multiplexer Channel and Bus, the optional Selector Channel, each of the 113 user instructions, interrupts, and automatic I/O operations.

GET-6174 combines in one manual the same type of information for the 3010/2 as was provided in GET-6047, the 30/3010 Reference Manual, and PCP-126, the Systems Interface Manual, for 3010 systems.

The theory of operation for the overall system and detailed theory of operation for each functional subsystem are provided in the Theory of Operation manuals shipped with each 3010/2 system. Computer maintenance information is also provided, including preventive maintenance, performance testing, adjustment, troubleshooting, and repair instructions.

The GE-PAC 3010/2 System Hardware Configurator, PCP-230, provides instructions for using the GE-PAC 3010/2 Price List and the 3010/2 System Hardware Specification sheets to configure a system. This General Description describes the functional features and operating features of each standard system module. When the implementation of an option requires that some other function be implemented, such information is given. Users of the Hardware Configurator may refer to appropriate sections of this manual to aid in determining which hardware should be implemented.

The GE-PAC 3010/2 system software is described in manuals which describe the standard system software and in special documentation provided when the application programs are developed by the General Electric Company for specific systems. The standard software manuals include GET-6171, the GE-PAC 30/3010 Programming Reference Manual; GET-3083, RTMOS-30 Reference Manual (for systems with Drum Memory); and GET-3082, RTMOS-30 Reference Manual (for all-core systems).

# SOFTWARE

The GE-PAC 3010/2 software and hardware are designed to complement each other to the greatest extent possible, through careful consideration of which functions can be more efficiently and economically accomplished by hardware and by software. This feature is illustrated by the relation of RTMOS-30, the standard real-time multiprogramming operating system for the 3010, to such hardware features as the Processor's Protect Mode, which protects RTMOS-30 from interference from other programs. Another such feature is the user instruction set, which includes the powerful Supervisor Call instruction, SVC. SVC serves as the interface between RTMOS-30 and the programs which run under its control.

All of the standard software is fully modular, which greatly facilitates the compilation of the on-line programs for a system. The standard software may be divided into two classes: (1) programs which run while the computer is on-line and controlling the process, and (2) programs which run when the computer is off-line. All of the programs in the first group run under the control of RTMOS-30. The programs in the second group consist principally of assemblers, loaders, editors, and debugging programs. Hardware test programs might also be considered as members of the second class, but because they are used primarily by installation and maintenance personnel, they are supplied with the system maintenance materials, rather than with the system software.

The standard off-line programs are described in the GE-PAC 30/3010 Programming Reference Manual, GET-6171. This manual also describes much of the technique for using the system software, such as the assembler language, program loading, generation, and debugging. The system's instruction set, interrupt handling, programmed and automatic I/O sequences, and Display Panel operation are described in the GE-PAC 3010/2 Central Processor Reference Manual, GET-6174. The all-core version of RTMOS-30 is described in GET-3082. GET-3083 describes the Drum version of RTMOS-30.

This section provides general information which applies to all GE-PAC 3010/2 computer system equipment, unless specifically excepted in the detailed descriptions in Sections 4 through 12.

# 3.1 ENVIRONMENTAL SPECIFICATION

The detailed environmental specifications for the GE-PAC 3010/2 product line are described in the Functional Design Specifications and in the GE-PAC 3010/2 Environmental Specification. The system is designed to meet the performance specifications at any ambient temperature from 0° C to 50° C, provided that the relative humidity is such that no moisture condensation on the equipment occurs. If the following equipment options are implemented within or in the same environment as the Central System Cabinet, the operating temperature range is reduced as follows:

Drum Memory; 10° C to 40° C. Teletypewriter; 18° C to 29° C. TermiNet\* Printer; 0° C to 40° C. Magnetic Tape Transport; 2° C to 50° C. Disc Unit; 15.6° C to 32.2° C. Display Controllers/Terminals; 18°C to 29°C. Card Punch; 18° C to 29° C. Card Reader; 20° C to 27° C.

# **3.2 INPUT POWER**

The primary AC supply to the computer system is connected to the AC entry panel in the Central System Cabinet (CSC). This must be from a single phase source, 103V to 127 VAC, 60 Hz  $\pm 3.0\%$ , three wires (high, neutral, and safety ground), with harmonic voltage distortion no greater than 5%. It is strongly recommended that this supply be isolated from external noise sources by an isolation transformer which provides shielding between the source and load. Refer to the GE-PAC 3010/2 Site Planning Manual, GET-6046, for additional information.

## 3.2.1 Peripheral Devices

All of the peripheral devices plug into standard threepin wall sockets and require 115 VAC  $\pm 10\%$ . They should be supplied from the same distribution as the CSC.

## 3.2.2 Process I/O Termination Cabinets

The termination cabinets are supplied from the CSC. Voltage, frequency, and harmonic distortion requirements are as for the CSC.

## 3.2.3 Drum Cabinet

The Drum Cabinet requires 115 VAC  $\pm 10\%$ , 57 to 63 Hz, single-phase, three-wire power.

# 3.3 CABLING

Interconnecting cables between major assemblies, cabinets, and peripheral devices, are plug connected,

or connected via screw terminals. All cables with more than nine conductors are plug connected on at least one end.

## 3.4 CONSTRUCTION

## 3.4.1 Cabinets

All of the electronic circuitry in the computer system, except for that contained in peripheral devices, is housed in heavy duty cabinets suitable for use in an industrial environment. Where necessary to meet the environmental requirements, the cabinets are cooled by blower driven air. Air filters are provided in cabinets containing blowers to remove airborne dirt from the air supply. The following cabinets are employed as required (dimensions, approximate H x D x W): Central System Cabinet (75 x 28 x 30 inches), Process I/O Termination Cabinet (75 x 28 x 30 inches), Drum Cabinet (75 x 28 x 30 inches). The CSC provides for cable entry in an area at the bottom of the cabinet. The termination cabinet accepts cables either at the top or the bottom of the cabinet.

Where the CSC must be operated in a corrosive environment, the cabinet may be provided in an optional "purged air" version. When this option is implemented, the customer supplies fresh clean air at the top of the cabinet to maintain positive internal pressure, thereby prohibiting the entry of contaminated air (option no. 3010AJ4501).

## 3.4.2 Printed Wire Boards

The electronic components are installed on plug-in printed wire boards where practicable. The electronics are primarily monolithic integrated circuits.

## 3.4.3 Modularity

Most of the electronic modules in a 3010/2 system are located in the CSC. In addition to the CSC, 3010/2 systems typically have one or more process I/O termination cabinets, and several free-standing peripheral devices. The first Paper Tape Reader may be built into the front of the CSC. Systems with Drum, Disc, and Magnetic Tape Memory may have one or more bulk memory cabinets. All standard system options (except for some TermiNet Printer features) may be added in the factory or in the field by plugging-in or bolting-on the hardware and making minor wiring changes.

## 3.4.4 Maintainability

The system is designed for maximum availability. All system components are designed to permit quick and easy access to the internal hardware. Test programs, procedures, and test hardware are available, and they, and the system documentation are designed to minimize the degree of specialization required of maintenance personnel.

\*Registered Trademark of General Electric Company

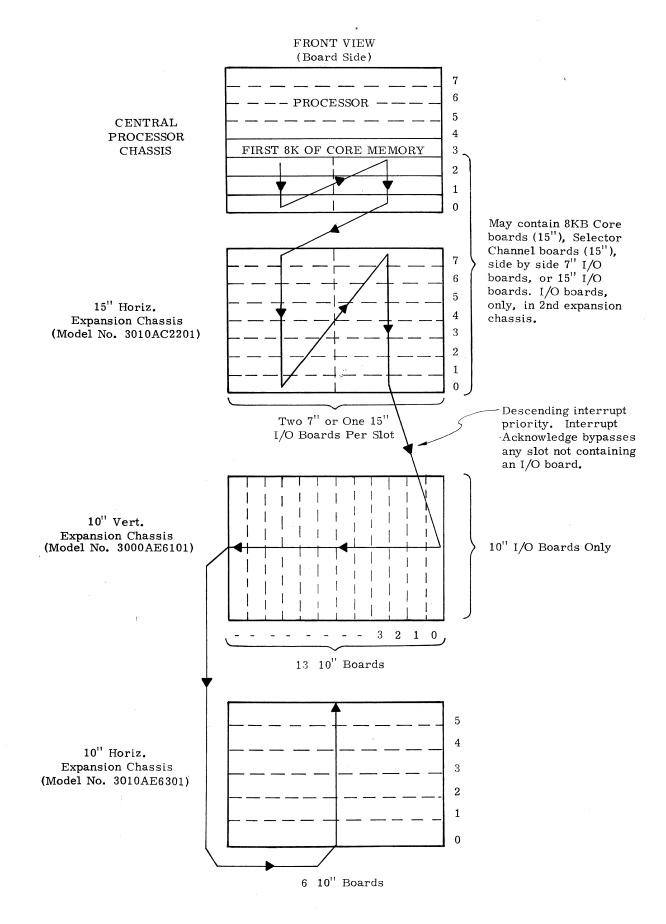

The Central Processor is the computational and control center for the GE-PAC 3010/2 computer system. The basic Central Processor is contained in a single ultra-compact unit, which includes a Processor, the first 8,192 bytes of Core Memory, and may include additional core modules. Selector Channels. or I/O controllers. This basic unit accommodates up to eight 15" printed wire boards, of which five are devoted to the Processor and the basic 8K core module. The basic Central Processor includes a Control Console.

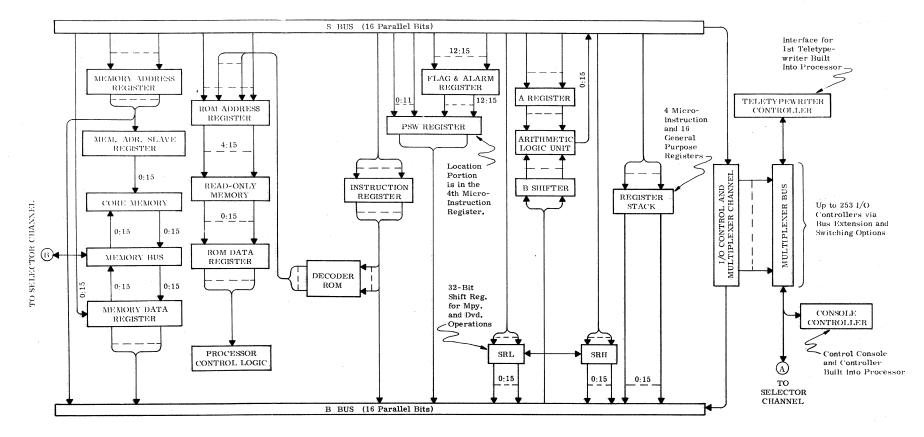

A block diagram of the Central Processor is provided on Fig. 4.1. The Central System Cabinet contains the basic Central Processor chassis, the basic System Power Supply, the system power control circuits. and may include one or more expansion chassis and System Power Supplies for the implementation of additional Core Memory, Selector Channel, or I/O controller boards.

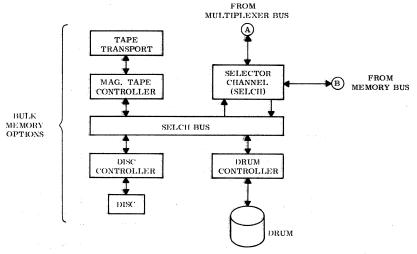

The Processor's interface with the optional Universal Clock, Automatic Memory Protect Controller, and all other peripheral device and process I/O controllers, is provided by the Multiplexer Channel and Bus. The Selector Channel and Bus provide the interface to the bulk memory subsystem options, including Drum, Disc, and Magnetic Tape subsystems.

The 3010/2 process computer system achieves a functional capability similar to much larger and more complex computers through the use of a solid state non-volatile Read-Only Memory (ROM). The ROM greatly reduces the complexity of the Processor logic by executing micro-instruction routines which implement the 113 user instructions, effect the automatic I/O sequences, and perform housekeeping operations such as interrupt monitoring, Control Console service, and automatic register storage and restoration during power-down/restart sequences.

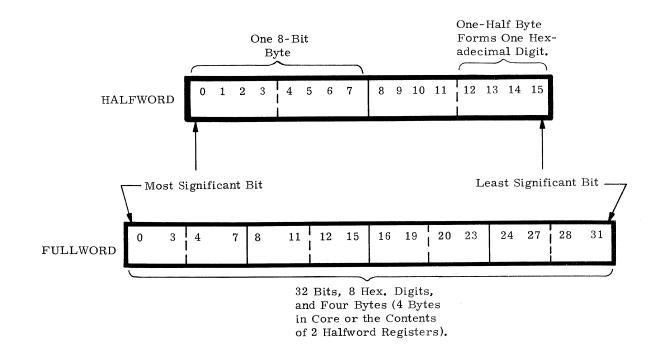

# 4.1 DATA AND INSTRUCTION WORD FORMATS

The Central Processor data and instruction words appear both in the hardware and in the documentation in the forms depicted on Fig. 4.1-1. These formats lend themselves to the use of hexadecimal notation, where each hexadecimal digit represents four binary bits  $(2^4 = 16)$ . The hexadecimal digit set and its relation to binary, octal, and decimal notation are described on Table 4.1-1.

Fixed point data are represented in the form of 16bit halfwords or 32-bit fullwords, where bit 0 is the sign bit. Positive numbers are represented as true binary numbers, with a sign bit of zero. Negative numbers are represented in two's complement form. with a sign bit of one.

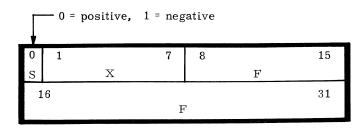

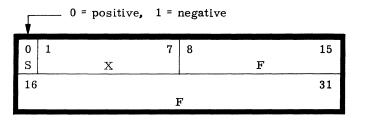

Floating point data are represented in fullword form, with bit 0 serving as the sign bit. The number consists of a signed exponent (X) and fraction (F), as on Fig. 4.1-2.

# 4.2 FUNCTIONAL DESCRIPTION

The overall sequencing of the Central Processor is controlled by a current Program Status Word (PSW). The PSW is a 32-bit fullword. The upper halfword defines the program status and resides in a 16-bit PSW register in the Processor (Fig. 4.2-1). The lower half of the PSW defines the location of the next user instruction and it resides in the fourth microprogram register in the Processor's register stack.

|                                         |       |             |              | 1       |  |  |

|-----------------------------------------|-------|-------------|--------------|---------|--|--|

| Binary                                  | Octal | Decimal     | Hexadeci     | mal     |  |  |

| 0000                                    | 0     | 0           | 0            |         |  |  |

| 0001                                    | 1     | 1           | 1            |         |  |  |

| 0010                                    | 2     | 2           | 2            |         |  |  |

| 0011                                    | 3     | 3           | 3            |         |  |  |

| 0100                                    | 4     | 4           | 4            |         |  |  |

| 0101                                    | 5     | 5           | 5            |         |  |  |

| 0110                                    | 6     | 6           | 6            |         |  |  |

| 0111                                    | 7     | 7           | 7            |         |  |  |

| 1000                                    | 10    | 8           | 8            |         |  |  |

| 1001                                    | 11    | 9           | 9            |         |  |  |

| 1010                                    | 12    | 10          | А            |         |  |  |

| 1011                                    | 13    | 11          | В            | 3       |  |  |

| 1100                                    | 14    | 12          | С            |         |  |  |

| 1101                                    | 15    | 13          | D            |         |  |  |

| 1110                                    | 16    | 14          | E            |         |  |  |

| 1111                                    | 17    | 15          | $\mathbf{F}$ |         |  |  |

| Binary                                  |       | Hexadecimal | Decimal      | Octal   |  |  |

| 0                                       | 15    |             |              |         |  |  |

| 011111111111                            | 1111  | 7FFF        | 32,767       | 77, 777 |  |  |

| 011400000000                            | 0000  | 7000        | 28,672       | 70,000  |  |  |

| 0000000001111                           | 1111  | 00FF        | 255          | 377     |  |  |

| 000000001000                            | 0111  | 0087        | 135          | 207     |  |  |

| 000000000000000000000000000000000000000 | 0111  | 0007        | 7            | 7       |  |  |

Table 4.1-1 Hexadecimal, Decimal, Octal and Binary Relationships

Fig. 4.1 3010/2 Central Processor

4-2

Fig. 4.1-1 Data and Instruction Word Formats

The PSW is automatically updated as program sequencing progresses, and it may be changed by the program.

The PSW is also involved in subroutine linkages and the servicing of interrupts. The program may load a new PSW or temporarily exchange the current PSW for a new one in order to initiate the execution of a new subroutine. Non-current PSW's are normally stored at core locations dedicated to specific interrupts. Interrupts may originate in the Processor or in external controllers, and each causes a PSW exchange, if it is not inhibited by the current PSW.

The Central Processor executes programs at two levels; the user level and the "micro" level. At the user level, the Central Processor accomplishes the work required by the user. For the purposes of this discussion, the user may be considered to be the people and the subsystems external to the Central Processor. The micro-level program executes micro-instructions in sequences which are built into the solid state Read-Only Memory (ROM). The operation code of each user instruction directs the Decoder ROM (DROM) to start the micro-program sequence which will emulate the user instruction. The DROM does this by loading the ROM starting address of the sequence into the ROM Address Register. Other micro-program sequences in the ROM handle the interrupt monitoring, Control Console, and housekeeping operations. The Processor control logic initiates the execution of these sequences.

The Processor hardware includes the logic necessary to execute the set of 16 micro-instructions as they are held in the ROM Data Register. The micro-program sequences are often referred to as "firmware" to indicate that they exist at some plane between "hardware" and "software".

For a more detailed description of the 3010/2 Central Processor, including a description of the user instruction set, interrupt handling, PSW control, and Control Console operating procedures, refer to the GE-PAC 3010/2 Central Processor Reference Manual, GET-6174.

## 4.2.1 Principal Processor Components

<u>S Bus and B Bus</u>. These two busses are 16-bit common tie points for the data destined to and from most of the registers and interfaces in the Processor. Most data is handled on a 16-bit halfword basis or in the form of an 8-bit byte. Usually the S Bus is the source of data destined to a Processor register. The B Bus is an intermediate destination for data from various Processor registers, core, and I/O interfaces, which may be modified by the B Shifter and the Arithmetic Logic Unit, on its way to a Processor register or core, via the S Bus.

Fig. 4.1-2 Floating Point Data

|                        |     | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                  |       |      | 1     | st H | alfw          | ord —                            |               |                                       | ·····      |     |                                     | - <sup>2nd</sup> Halfv              | vord – |  |

|------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|---------------|----------------------------------|---------------|---------------------------------------|------------|-----|-------------------------------------|-------------------------------------|--------|--|

| 0                      | 1   | 2                                                                                                                                                                                      | 3     | 4    | 5     | 6    | 7             | 8                                | 11            | 12                                    | 13         | 14  | 15                                  | 16                                  | 32     |  |

| WT                     | EI  | MM                                                                                                                                                                                     | DF    | AS   | FP    | QT   | $\mathbf{PM}$ | Zero                             | S             | С                                     | v          | G   | L                                   | Locatio<br>Counte:                  |        |  |

| ,<br>L                 |     |                                                                                                                                                                                        | Stat  | us - |       |      |               | 1. 2011 - 2020 - 2020 - 1022 - 1 | сис арар<br>, |                                       | Conc<br>Co |     | 1                                   | ana da nafor a santa an la companya |        |  |

| WT:                    | v   | Wait.                                                                                                                                                                                  | (See  | 4.5. | 4)    |      |               |                                  |               |                                       |            | * C | : C                                 | arry/Borro                          | w.     |  |

| EI:                    | J   | Respo                                                                                                                                                                                  | nd to | Exte | ernal | (1/0 | )) Int        | errupts.                         |               |                                       |            | V   | : O                                 | verflow.                            |        |  |

| $\mathbf{M}\mathbf{M}$ | : 1 | Respo                                                                                                                                                                                  | nd to | Mac  | hine  | Mal  | funct         | tion Inte                        | rrupt         | s.                                    |            | G   | : >                                 | Zero.                               |        |  |

| DF:                    | ]   | Respo                                                                                                                                                                                  | nd to | Fix  | ed Po | oint | Divid         | le Fault                         | Inter         | rupts                                 | 5.         | L   | : <                                 | Zero.                               |        |  |

| AS:                    | ]   | Enable Automatic I/O (EI must be set also). These bits have differing                                                                                                                  |       |      |       |      |               |                                  |               |                                       |            |     |                                     |                                     |        |  |

| FP:                    |     | Respond to Floating-Point Arithmeticmeanings with variFault Interrupts.structions. The cuPSW after a Machi                                                                             |       |      |       |      |               |                                  |               |                                       | urrent     |     |                                     |                                     |        |  |

| QT:                    | ]   | Respond to the Queue Termination Interrupt. function PSW swap reflects                                                                                                                 |       |      |       |      |               |                                  |               |                                       |            |     |                                     |                                     |        |  |

| PM:                    | 2   | Protect Mode. If reset, the Processor is in<br>Supervisory mode. This bit is set to protect<br>against the execution of Privileged Instructions the Condition Code bits as<br>follows: |       |      |       |      |               |                                  |               |                                       |            |     |                                     |                                     |        |  |

|                        |     |                                                                                                                                                                                        |       |      |       |      |               | ng and u<br>mory Pr              | •             |                                       |            |     | V: Core Parity Er<br>on Operand Fet |                                     |        |  |

|                        | (   | Option (4.3.3) is enabled when this bit is set.                                                                                                                                        |       |      |       |      |               |                                  |               | G: Core Parity Er<br>on Instruction I |            |     | •                                   |                                     |        |  |

|                        |     |                                                                                                                                                                                        |       |      | 3     |      |               |                                  |               |                                       |            |     | $\mathbf{L}$                        | Power Fai<br>Detected.              | ilure  |  |

Fig. 4.2-1 Program Status Word

Instruction Register. This register holds the user instructions while they are decoded and executed.

<u>Decoder ROM (DROM)</u>. The DROM translates the operation code of each user instruction held by the instruction Register to ROM addresses for entry into the micro-program sequence which emulates the user instruction. It contains 256 12-bit ROM address words.

Flag and Alarm Register. Four flag flip-flops record the result of user instruction execution for entry into the condition code of the current PSW. These flags are designated Carry/Borrow, Overflow, Greater than Zero, and Less than Zero, and reflect these conditions after arithmetic operations. The flag bits have differing meanings after execution of other user instructions. As an example, I/O instructions which cause the I/O controller status to be returned to the Processor copy the four least significant bits of the status byte into the condition code of the current PSW. Three alarm flip-flops record detected parity errors on operand fetches, instruction fetches, or a detected power failure. Any of these alarms causes a Machine Malfunction Interrupt and PSW swap. After the PSW swap, the new current PSW condition code reflects the type of malfunction, as indicated on Fig. 4.2-1. After a successful restart following a power failure detection, the condition code bits of the current PSW are all reset.

Register Stack. The register stack consists of 20 independent working registers for temporary data storage by the user program and the micro-program. Four of these 16-bit registers are dedicated for use by the micro-program only and the fourth of these stores the Location Counter halfword of the current PSW. The remaining 16 registers are General Purpose registers for use by the user program. All General Registers except General Register 0 may be used for indexing. General Register 0 cannot be used for indexing because the user instruction index field (bits 12 through 15) must be non-zero to specify indexing.

<u>A Register</u>. This register provides one 16-bit operand for the Arithmetic Logic Unit. The other ALU operand is derived from the B Bus via the B Shifter, Arithmetic Logic Unit (ALU). The ALU performs arithmetic and logical functions required by the microinstructions. The B Shifter manipulates the second operand prior to entry to the ALU, as required by the micro-instructions. The shifter may shift left, right, or may exchange the two byte in the B Bus halfword (cross shift).

Fullword Shift Register, SRH/SRL. SRH and SRL are interconnected to form a 32-bit shift register which is used in double precision operations such as shift, rotate, multiply, and divide.

<u>Read-Only Memory.</u> The ROM stores 1536 16-bit micro-instruction words. The micro-instruction words are loaded into the ROM Data Register from the address specified by the ROM Address Register. The ROM Data Register holds the micro-instruction word while it is interpreted and executed by the Processor control logic. The ROM consists of 24 high speed integrated circuits, each of which contains 256 4-bit digits. These are arranged into six pages, each of which contains 256 16-bit ROM data words. The data patterns are built into the integrated circuits. The micro-instruction cycle time is approximately 250 nanoseconds. The 256 12-bit DROM words are contained in three similar integrated circuits.

Multiplexer Channel and Bus. The Multiplexer Channel provides the Processor's interface to the Multiplexer Bus. The Multiplexer Bus is a universal interface to all of the 3010/2 system's I/O controllers except those connected to the Selector Channel Bus and possible custom designed Direct Memory Access Channels. The Multiplexer Bus provides an identical control signal and Data (D) Bus interface to all I/O controllers, including the Universal Clock (4.9), the Automatic Memory Protect Controller (4.3.3). all peripheral device controllers, remote communications controllers, and all process I/O controllers. The Multiplexer Bus control signals are actuated by the Processor control logic as directed by the microprogram. The D Bus is a 16-bit bidirectional bus which may transfer byte or halfword data in either direction. Output data is derived from the S Bus and input data is transferred to the B Bus. The physical location of the controllers on the bus determines the interrupt priority (4.4.2). The basic Multiplexer Bus may serve up to 16 I/O controllers. The Bus Extension and Switching options described in Section 5 of this manual may be used to extend the bus to the maximum of 253 controllers (in addition to the built-in Teletypewriter Controller and Control Console Controller) and to permit a common Multiplexer Bus section to serve more than one Central Processor.

Control Console Controller. The Programming and Maintenance Control Console is operated as a device and controller connected to the Multiplexer Bus. A micro-program sequence is dedicated to the operation of the console. The console controller is built into the Processor and is assigned device address X'01'\*. Refer to 4.5 in this manual for a description of the console and controller and to Section 7 of the 3010/2 Central Processor Reference Manual, GET-6174, for detailed operating instructions.

Teletypewriter Controller. The built-in Teletypewriter Controller provides a standard 20 milliampere current loop interface to a 3000AE12 ASR 33, ASR 35, or KSR 35 Teletypewriter. The controller is the second device on the Multiplexer Bus and is assigned device address X'02'. Teletypewriters and the operating sequence are described under 8.1 in this manual.

# 4.3 CORE MEMORY

Core Memory stores user instructions and data currently in use by the running program. If the system includes a bulk memory subsystem such as Drum or Disc Memories, user programs and data may reside in bulk memory, to be transferred to Core Memory as they are needed.

This memory is a three-wire, coincident current, random access, core memory. The basic Central Processor chassis contains the first 8K byte module (K =  $1024_{10}$ ) in each system. The maximum core size is 64K bytes, implemented as eight 8K memory boards (Model No. 3010AC1401 or AC1402). If implemented, the second, third, and fourth core modules are installed in the basic Central Processor Chassis. The fifth through eighth core modules are installed in a 15" universal expansion chassis, which is installed immediately below the Central Processor chassis in the Central System Cabinet.

The total Core Memory cycle time, including access and restoration, is 1.0 microseconds. The access time is 300 nanoseconds. Each 8K byte core module contains 4096 16-bit halfwords, and either byte in any halfword may be directly addressed by the Processor. Where both the Processor and a Selector Channel (Section 6 of this manual) are contending for memory access at the same time, the cycle is "stolen" from the Processor and the Processor waits while the Selector Channel is granted access. In addition to the core access channel used by the Processor, four other direct memory access channels are available. The Processor is always assigned the lowest priority and the Selector Channels (or possible custom designed direct memory interfaces) on the four direct access channels are assigned descending priorities from the first implemented to the fourth.

# 4.3.1 Core Memory Format and Addressing

Each of the possible 65,536 8-bit bytes in Core Memory is directly addressable by the Processor, as the user instruction operand addresses are all 16 bits in length. Each of the user instructions may require a byte, a halfword, or a fullword to be read from, or stored in core. However, each read or write cycle transfers one 16-bit halfword. The user instructions may utilize one byte from each halfword, the full halfword, or two successive halfwords.

<sup>\*</sup> The notation "X' ' ", indicates that the digits between the ' ' marks are expressed in hexadecimal form.

The core addresses are assigned as successive hexadecimal byte addresses starting with  $0000_{16}$  and ending with FFFF<sub>16</sub>. A group of bytes combined to form a halfword or fullword is addressed by the lowest numbered byte address in the group. Halfword or fullword operands in core must be positioned at even numbered byte addresses. Because of assembler and listing format considerations, all operand addresses, including byte addresses are even numbered. Table 4.3-1 provides some examples of the core addressing scheme.

Should a core location higher than any implemented in a system be addressed, the memory cycle will occur, but the data will be lost on a write operation and all zeros will be read on a read operation.

## 4.3.2 Parity Option

Each core module implementing the Parity Option (Model No. 3010AC1402) includes a seventeenth bit which stores an "odd ones" parity bit with each halfword. The Processor contains logic which stores a binary one in the parity bit if the number of "one" data bits is even on a Processor write operation. The Processor checks for correct parity on each Processor read operation. If parity error is detected on a read operation, and if the Machine Malfunction Interrupt is enabled (PSW bit 2 set), a Machine Malfunction Interrupt and PSW swap occurs. If the "Machine Malfunction - New PSW" is successfully retrieved, the new PSW initiates an error recovery routine. The condition code field of the new PSW indicates the type of error as indicated on Fig. 4.2-1.

It is possible to have a mixture of 8K-byte core modules containing the parity bit and 8K-byte modules without the parity bit in the same system.

## 4.3.3 Automatic Memory Protect Option

The Automatic Memory Protect Controller (Model No. 3010AB3401) is an I/O controller installed on the Multiplexer Bus. It stores a Core Memory protection pattern provided by a user program. The memory protect controller continuously monitors the seven most significant bits of the Processor's Memory Address Register, and when a non-privileged Core Memory write operation is attempted by the Processor into one of the protected areas, the memory protect controller causes the Processor to convert the write cycle to a read cycle, attempts to interrupt the Processor, and sets bits 3 and 5 of the Automatic Memory Protect controller status byte.

Normally, the Automatic Memory Protect Controller is wired to protect 64 blocks of 1024 Core Memory bytes per block. This provides programmable protection for the largest available 3010/2 Core Memory (64K). A simple wiring change may be made in the

|                        | FULLWORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |      |      | FULLWORD |      |          |      |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|----------|------|----------|------|--|

|                        | HALF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | WORD       | HALF | WORD | HALF     | WORD | HALFWORD |      |  |

|                        | BYTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BYTE       | BYTE | BYTE | BYTE     | BYTE | BYTE     | BYTE |  |

| HEXADECIMAL<br>ADDRESS | 0050                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0051       | 0052 | 0053 | 0054     | 0055 | 0056     | 0057 |  |

| CORE<br>CONTENTS       | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>2</b> 3 | 45   | 67   | 89       | AB   | CD       | EF   |  |

|                        | If a user instruction specifies an operand address of $0050_{16}$ :<br>For a byte-oriented instruction the operand is $01_{16}$ .<br>For a halfword-oriented instruction the operand is $0123_{16}$ .<br>For a fullword-oriented instruction the operand is $01234567_{16}$ .<br>If a user instruction specifies an operand address of $0052_{16}$ :<br>For a byte-oriented instruction the operand is $45_{16}$ .<br>For a halfword-oriented instruction the operand is $4567_{16}$ .<br>For a fullword-oriented instruction the operand is $4567_{16}$ . |            |      |      |          |      |          |      |  |

Table 4.3-1 Core Memory Addressing

factory or in the field to change the block size to 512 bytes or 2048 bytes. Protection for 64 512-byte blocks provides protection to the first 32K bytes of core. Since there is no core above 64K, only 32 blocks are available if the 2048-byte block size is chosen.

#### **Operating** Sequence

The program sets up the memory protect controller by issuing an appropriate Output Command to the controller (Fig. 4.3-1) and then issuing up to eight Write Data instructions that transfer the appropriate 64-bit protection pattern as eight 8-bit bytes. The standard device address for the controller is X'AE', but the address may be changed by jumper wiring on the controller board.

Any Output Command issued to the controller resets a Write Data byte counter in the controller, and the first Write Data byte transferred to the controller following the Output Command transfers the protection pattern for the first eight blocks of core. If the block size is 1024 bytes, this first byte covers the first 8, 192 core addresses (0000 through X'1777'). The first bit in the first data byte protects the lowest block of core, if it is set, and the remaining bits protect successively higher blocks. Subsequent 8-bit data bytes protect successively higher core areas of 8 blocks each. Should nine or more data bytes be transferred to the controller before the next Output Command, the protection pattern is overwritten, beginning with the lower core addresses.

Core Memory protection is activated only when the Processor is in the Protect Mode (PSW bit 7 set). Since the attempted execution of a privileged instruction while in the Protect Mode causes a Protect Mode violation interrupt before the instruction is executed (4.4.1), a memory protect violation can be detected only when a memory write is attempted during the execution of a non-privileged instruction. The Automatic Memory Protect Controller interrupts the Processor upon detection of a memory protect violation if bit 1 of the current PSW is set and if the last Output Command to the controller enabled the interrupt.

Since the program must use privileged instructions (4.4.1) to set up the memory protect controller and to respond to its interrupt, PSW bit 7 must be reset while instructions are issued to the controller. After the protection pattern has been specified, PSW bit 7 must be set to specify Protect Mode and to enable the detection of a memory protect violation.

Output Command instructions issued to the controller reset the data byte counter and transfer a command byte which specifies the modes of operation as follows (Fig. 4.3-1):

- Bits 0 and 1 = interrupt disarm and enable respectively. When enabled the interrupt queue flip-flop is set when a memory protect violation is detected. When disarmed, the memory protect controller's interrupt queue flip-flop is reset.

- Bit 2 = 1 = Protect On. PON specifies that the core areas specified by the protection pattern are to be protected. The 64-bit protection pattern may be changed by issuing up to eight data bytes to the controller via Write Data instructions.

- Bit 3 = 1 = Protect Off. POF overrides the memory protection. This command might be used to disable memory protection temporarily while the Processor remains in the Protect Mode.

Sense Status instructions issued to the controller cause a status byte to be returned to the Processor as follows (Fig. 4.3-1):

- Bit 2 = 1 = Protection On. PON is set when protection has not been overridden by a POF Output Command.

- Bit 3 = 1 = Protect Write Flag. PWF sets when a memory protect violation is detected. PWF is reset by an Output Command, an Acknowledge Interrupt instruction, or when the INT button on the Control Console is pushed to initialize the hardware.

- Bit 5 = 1 = Examine. EX = PWF.

When the system hardware is initialized (4.5.3), the memory protect controller interrupt is disarmed, protection is overridden, the PON and PWF status bits are reset, and the protection pattern is unchanged. A power failure, restart, and hardware initialization (4.7), leaves the protection pattern register in an uncertain state because it is not initialized. The program should reestablish the protection pattern following a power failure and restart.

| - Comm<br>- Status<br>- Bit | and Byte<br>Byte | e   |     |   |    |   |     |

|-----------------------------|------------------|-----|-----|---|----|---|-----|

| 0                           | 1                | 2   | 3   | 4 | 5  | 6 | 7   |

| 0                           | 0                | PON | PWF | 0 | EX | 0 | · 0 |

| DSAM                        | ENAB             | PON | POF |   |    |   |     |

Fig. 4.3-1 Automatic Memory Protect Controller Command and Status Bytes

# 4.4 INTERRUPTS

Interrupt signals request that the current Processor status be saved, and that the Processor branch to a service or corrective routine. Interrupts may originate within the Processor or outside the Processor. When the routine requested by the interrupt is completed, the status may be restored and the interrupted program may resume.

When an interrupt is serviced, the content of the Processor's PSW register is stored in a dedicated "old PSW" core location, and a new PSW pointing to the servicing routine is loaded into the PSW register. When the service routine is completed, the PSW register may be loaded with the old PSW and the interrupted program may resume.

The Processor's response to interrupts is under the control of the Program Status Words. The current PSW, which is stored in the Processor's PSW register, defines the current status, and controls the response to seven of the interrupt types. The following is a list of the types of interrupts and the PSW bits which control the seven inhibitable types. The program may permit interrupt servicing by setting the appropriate control bits and may inhibit interrupt servicing by resetting control bits. The I/O Controllers on the Multiplexer Bus store (queue) interrupts until they are acknowledged, unless they are disarmed by an Output Command issued to the controller. Output Commands may <u>disable</u> interrupts from some controllers, but allow the interrupt queue flip-flop to store the interrupt.

| Туре                               | Internal or<br>I/O Control | PSW<br>Control Bits |

|------------------------------------|----------------------------|---------------------|

| External                           | I/O                        | 1                   |

| Machine Malfunction                | Int.                       | 2                   |

| Fixed Point Divide<br>Fault        | Int.                       | 3                   |

| Automatic I/O<br>Service           | I/O                        | 4                   |

| Floating Point<br>Arithmetic Fault | Int.                       | 5                   |

| Channel Termination                | I/O                        | 6                   |

| Protect Mode<br>Violation          | Int.                       | 7                   |

| Illegal Instruction                | Int.                       | Not Inhibitable     |

| Termination Queue<br>Overflow      | I/O                        | Not Inhibitable     |

| Supervisor Call                    | Int.                       | Not Inhibitable     |

For a detailed description of the use of interrupts and the Central Processor's responses, see Subsection 2.4 of the GE-PAC 3010/2 Central Processor Reference Manual, GET-6174. The following paragraphs describe the aspects of interrupt configuration, servicing, and priorities of particular significance in relating the descriptions of the 3010/2 functional subsystems in this General Description to the interrupt structure.

## 4.4.1 Protect Mode

Where the on-line system programs are under the control of an operating system such as RTMOS-30, the operating system normally runs in the Supervisory Mode with bit 7 of the current PSW reset. This allows the operating system to execute privileged instructions and to write in any area of Core Memory. The user level programs controlled by the operating system normally run in the Protect Mode with bit 7 of the current PSW set, which enables the memory protect option (4.3.3) and prevents the execution of privileged instructions.

Normally, only the operating system has the privilege of executing the subset of I/O and system control instructions: Auto Load, Write Data, Read Data, Sense Status, Output Command, Acknowledge Interrupt, Exchange Program Status, Load Program Status, Simulate Interrupt, and all variations of these types of instructions. If, when in the Protect Mode, an attempt is made to execute one of these privileged instructions a Protect Mode interrupt occurs. If such an interrupt occurs, the instruction is not executed, the location counter in the current PSW is not incremented, and the old PSW stored as a result of the PSW swap points to the location of the privileged instruction which caused the interrupt.

If the Automatic Memory Protect Controller (4.3.3) is implemented, and should a program running in the Protect Mode attempt to write in an area defined for protection by the pattern held by the controller, the memory protect controller will attempt to generate an external interrupt. If the interrupt is not disarmed, and if the current PSW has bit 1 set, the interrupt will be serviced. Regardless of the memory protect interrupt status, the protection feature will prohibit writing in the protected area, and if the program is not interrupted, instruction sequencing will continue.

## 4.4.2 I/O Interrupts

The Central Processor can be interrupted by any of the I/O controllers on the Multiplexer Bus to which it can address instructions. Since all I/O controllers sense the address in a single 8-bit byte, the Central Processor may address up to 256 devices. Since every Processor has a built-in Control Console Controller and a Teletypewriter Controller, and since most 3010/2 systems implement the Universal Clock Controller (4.9), 251 addresses are left to accommodate additional input/output controllers of all types (address X'00' is not available).

I/O interrupt priority is determined by the electrical location of the controller on the Multiplexer Bus, and not by the device address. When the Processor is interrupted, it sends an Acknowledge pulse down the Multiplexer Bus. When the pulse encounters the controller with its interrupt queue flip-flop set, the pulse is stopped and the controller returns its device address to the Processor to indicate which controller originated the interrupt.

Fig. 4.4-1 I/O Interrupt Priorities

The Acknowledge pulse may be generated by the micro-program if Automatic I/O service is enabled (PSW bits 1 and 4 set), or it may be generated by the execution of an Acknowledge Interrupt instruction by the program (PSW bit 1 set and 4 reset). Since the Control Console interrupt is a special type of interrupt (4.5) and is not on the I/O interrupt priority chain, the built-in Teletypewriter Controller has the highest priority. If implemented, the Automatic Memory Protect Controller board is assigned to the Multiplexer Bus slot with the next highest interrupt priority. The Universal Clock board is normally mounted to the right of the memory protect board, so it is eight slots down the bus from the memory protect controller, if these boards are in an expansion chassis.

The Acknowledge pulse and interrupt priority travels first down the left side (front view) of the chassis which accept 15" horizontally mounted board assemblies. After it passes through the lower-left slot, it goes to the top-right slot in the same chassis, and then down the right slot. The interrupt priority travels from the right to left (front view) in chassis which accepts 10" vertically mounted boards. Fig. 4.4-1 illustrates this scheme.

## 4.4.3 External Interrupt Module

Up to four 3000AF12 External (8-Line) Interrupt Modules may be implemented as I/O controllers on the Multiplexer Bus. Each such module provides an interface to as many as eight external interrupt terminations. The inputs are typically connected to terminations in the Central System Cabinet and may be relay isolated. Power (12 VDC) and contacts to control the relays are provided by the user, or the interrupts may be derived from the optional 3010AF16 Change Detect Digital Input Terminations (see 11.1.1).

Each external interrupt implemented uses one I/O Multiplexer device address. The external interrupts are armed or disarmed and masked or unmasked by Write Data instructions addressed to the lowest device number assigned to the module. Four such lowest device numbers are possible: X'20', X'28', X'30', and X'38'. Once initialized by pushing the Initialize button the Display Panel or issuing an Output Command to the interrupt module, the first Write Data instruction specifies which interrupt lines are to be armed or disarmed and the second Write Data instruction specifies which interrupts are to be masked or unmasked. Bits 0 through 7 of the data byte correspond to interrupts 0 through 7, with interrupt 0 having highest priority. Successive Write Data instructions are presumed to transfer arm/disarm and mask/unmask bytes. respectively.

A bit set in an arm/disarm byte allows the corresponding interrupt queue flip-flop to set when the corresponding relay energizes (if relay buffered). A bit set in a mask/unmask byte allows the interrupt to be applied to the Processor, and to be serviced if bit 1 of the current PSW is set. The lowest device address implemented on an External Interrupt Module is selected with jumper wiring on the module, and determines the device address corresponding to interrupts 0 through 7 as follows:

> X'20' through X'27'. X'28' through X'2F'. X'30' through X'37'. X'38' through X'3F'.

When the External Interrupt Module is initialized, all eight interrupts are disarmed and masked.

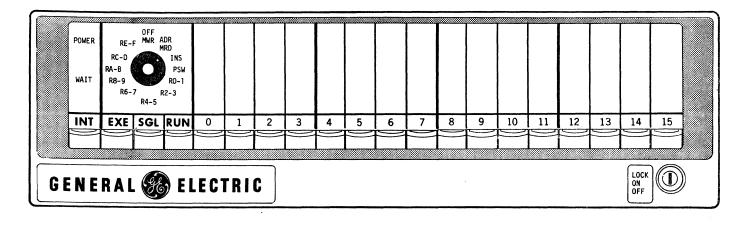

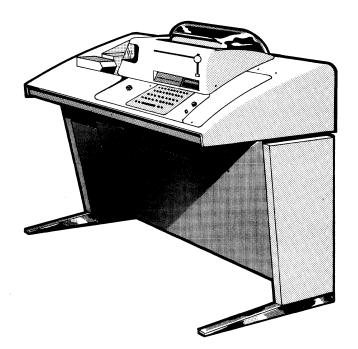

# 4.5 PROGRAMMING AND MAINTENANCE CONTROL CONSOLE

The Central Processor's Control Console allows direct communication with the machine by programming and maintenance personnel. It communicates with the Processor through the built-in Control Console Controller, which is an I/O controller on the Multiplexer Bus. The Control Console functions are effected by a micro-program sequence which is initiated by the console interrupt. The interrupt is generated when the EXEcute switch on the console is pushed. The running program may communicate with the console by issuing I/O user instructions to the Console Controller (device address X'01'). The console interrupt is not a normal I/O interrupt, and can be serviced by the program only if bit 4 of the current PSW is set. For additional console programming considerations, see 7.4 in the 3010/2 Central Processor Reference Manual, GET-6174.

Two register displays are provided and all 16 of the General Purpose Registers may be selected for display, two at a time. The displays can also display the current PSW, the next instruction to be executed, and the contents of any Core Memory location. The console's rotary selector selects the type of operation and display to be in effect the next time EXEcute is pushed. The panel also features a hardware initialize switch, a single step mode switch, a run switch, and 16 data switches.

## 4.5.1 Function Switches

Three function switches are used to select the Central Processor's mode of operation: Single (SGL), RUN, and a rotary selection switch. These three switches are used to place the Central Processor in one of six modes. All three switches must be placed in the correct position prior to pushing EXEcute to select a new mode. The six modes and the switch positions which select them are as follows (detailed console operating procedures are in Chapter 7 in the 3010/2 Central Processor Reference Manual, GET-6174):

Fig. 4.5-1 Control Console

Address Mode. SGL-up, RUN-up, rotary to ADR/ MRD; this mode is used to place an address in the location counter of the current PSW. The desired address must be placed in the 16 data switches and the function switches must be positioned before EXEcute is pushed to enter the address.

Memory Read Mode. SGL-down, RUN-up, rotary to ADR/MRD; this mode is used to read the contents of the core address specified by the location counter of the current PSW. When EXEcute is pushed, the upper console display shows the address plus 2, and the lower display shows the contents of the location specified before the location count was incremented. Subsequent depressions of EXEcute transfers consecutive memory halfwords into the lower display and increment the address by 2.

<u>Memory Write Mode.</u> SGL-down, RUN-up, rotary to OFF/MWR; this mode is used to write the content of the 16 data switches into the core address specified by the location counter of the current PSW. When EXEcute is pushed, the upper console display shows the address plus 2, and the lower display shows the data written into the location specified by the location counter of the current PSW before it was incremented. Subsequent depressions of EXEcute cause the data switch contents to be written into consecutive memory halfwords and increment the address by 2.

Single Mode. SGL-down, RUN-down, rotary to any position except OFF/MWR or ADR/MRD. This mode is used to execute one instruction each time execute is pushed. The rotary switch may be used to select any pair of the general registers, the PSW, or the next instruction to be executed for display. When the registers are displayed, the even numbered register is in the upper display, and the odd is in the lower display. In the PSW position, the status and condition code halfword is in the upper display, and the location counter is in the lower display. In the INS position, the next instruction is in the upper display and the core halfword following that instruction is in the lower display. Halt Mode. SGL-up or down, RUN-up, rotary to any position except OFF/MWR or ADR/MRD. This mode is used to view various displays selected by the rotary switch without incrementing the location counter and executing instructions. The displays are the same as in Single Mode. If a display is selected, EXEcute must be pushed to make the change. When this mode is in effect, the WAIT indicator is lit. The WAIT indicator is also on when the program resets PSW bit 0 but, that state is interruptible, while the HALT mode wait state is not. The HALT mode is left by entering one of the five other modes.

<u>RUN Mode.</u> SGL-up, RUN-down, rotary to any position except OFF/MWR or ADR/MRD. This is the mode in which the program runs at normal speed. The two displays remain unchanged unless the program changes them via the console controller. The program may also read the content of the data switches in this mode and the Single Mode.

# 4.5.2 Data Switches

The 16 data switches line up below the corresponding bit indicators in the two displays. These are alternate position switches. A data switch in the "down" position enters a "one" into the corresponding bit in the PSW location counter when EXEcute is pushed upon entering the Address Mode or while in the address mode. When in the Memory Write Mode, data is written into the location specified by the current PSW. A data switch in the "up" position (as shown on Fig. 4.5-1) enters a "zero" in the corresponding bit position.

## 4.5.3 Initialize Switch and Keyswitch

The Initialize switch (INT) is a momentary switch which initializes the GE-PAC 3010/2 system hardware when pushed. Depression of INT starts a microprogram sequence which stores the contents of all of the General Registers and the complete PSW in dedicated core locations. When the initialize circuit is released, all of these registers are restored, and if bit 2 of the PSW is reset (Fig. 4.2-1) program sequencing can resume from the point at which it was stopped. If PSW bit 2 is set, a Machine Malfunction Interrupt PSW swap takes place. Initialization resets all interrupt queue flip-flops in the I/O controllers and places all system hardware in a known state. Note, however, that initialization does not clear out the PSW nor the General Registers. The condition code should be checked before starting a program to see if the status and condition code are appropriate. If not, the PSW should be changed by loading a new PSW from core. See 7.3.4 in the 3010/2 Central Processor Reference Manual, GET-6174 for detailed instructions on program execution.

The keyswitch is a security lock which prevents unauthorized tampering with the console controls. When the key is inserted and rotated fully clockwise (LOCK) power is on and the console controls are locked out. When in the ON position, power is on and the console controls operate. When in the off position, power is off. If power is turned off and then back on, the system is initialized as described in the preceding paragraph. When power is on, the POWER indicator on the console is lit.

## 4.5.4 Wait State

The Wait State is a state where the Program or the micro-program is waiting for some external event, such as operator intervention, to occur. When the Processor is placed in the Wait State, the WAIT indicator on the console lights and instruction sequencing stops. The Processor can be placed in the Wait State in one of three ways:

- The program sets bit one of the current PSW.

- The Control Console is in the Halt Mode or is in the Single Mode and no instruction is in the process of execution.

- The INT switch is pushed while the console Function Switches are not set up for the Run Mode.

The program initiated Wait State is typically entered when the program requires some operator intervention before instruction sequencing can resume. Since the console controls would normally be set up to select the Run Mode when the program entered the Wait state, the operator can restart instruction sequencing after the necessary action has been taken by pushing EXEcute. Any enabled interrupt may also cause a PSW swap which would take the Processor out of the program initiated Wait State.

The console initiated Wait State (Single Mode or Halt Mode) is left by selecting another mode and pushing EXEcute.

# 4.6 INPUT/OUTPUT SUBSYSTEM

The principal elements of the Central Processor's Input/Output Subsystem are the Multiplexer Channel and Bus. The Multiplexer Channel and Bus provide a total of 30 data and control lines to each attached peripheral device controller, remote communications controller, or process I/O controller. When an optional Selector Channel (Section 6) is implemented, the Multiplexer Bus is connected through to the controllers on the Selector Channel's private bus when the Selector Channel is in the idle mode.

The basic Multiplexer Bus can serve up to 16 I/O controllers. The Multiplexer Bus Extension and Switching options described in Section 5 of this manual may be implemented to serve up to the maximum of 255 controllers, including the Control Console Controller and Teletypewriter Controller, which are built into the Processor. Extended portions of the bus may be located in the Central System Cabinet or in adjacent cabinets.

I/O controllers are manufactured in four basic forms:

- One controller on a 7" x 15" board which occupies 1/2 of a slot in a 15" horizontal air-flow chassis.

- One controller on a 15" x 15" board which occupies a full slot in a 15" horizontal air-flow chassis.

- One controller on a 10" x 10" board which occupies one slot in a 10" vertical air-flow chassis, one slot in a 10" horizontal airflow chassis, or is adapted to one slot in a 15" horizontal air-flow chassis (using adapter no. 3010AE80001).

- One controller on multiple 10" square boards, which must be installed in adjacent slots in a 10" horizontal air-flow chassis, or a 10" vertical air-flow chassis.

Some 10" boards may employ mercury-wetted relays and must be mounted within 30° of vertical. Such boards must be installed in a 10" vertical air-flow chassis. The Multiplexer Bus Switch (Section 5) is one such board.

The physical form of each available controller is described in the GE-PAC 3010/2 Price List and in the 3010/2 Hardware Configurator, PCP-230. Any controllers on the portion of the Multiplexer Bus in the basic Central Processor chassis must be 7" or 15" horizontal types, or must be 10" boards in an adapter. Three types of expansion chassis are available:

15" Horizontal; accommodates up to 8 15" or 16 7" boards.

- 10" Horizontal; accommodates up to 6 10" boards, horizontally mounted.

- 10" Vertical; accommodates up to 13 10" boards, vertically mounted.

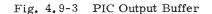

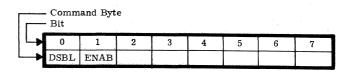

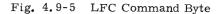

Input/output data on the Multiplexer Bus are transferred in the form of 16-bit halfwords or 8-bit bytes. Only controllers of the 7" and 15" form are capable of transferring halfword data and many of them use 8-bit bytes, only. The data lines on the 15" portion of the bus are 16 bidirectional lines. Most 10" controllers interface with 8 input lines and 8 output lines, and the conversion to this type of data interface is made in the cables which transfer the bus from the 15" portion to the 10" portion.