File No. S360-31 Form Y28-6610-2

# Program Logic

# IBM System/360 Operating System

Linkage Editor (E)

**Program Logic Manual**

Program Number 3605-ED-510

This publication describes the internal logic of the 15K and 18K versions of the level E linkage editor. The linkage editor combines and edits modules to produce a single load module that can be loaded into main storage by the control program. The linkage editor operates as a processing program rather than as a part of the control program.

This program logic manual is directed to the IBM customer engineer who is responsible for program maintenance. It can be used to locate specific areas of the program, and it enables the reader to relate these areas to the corresponding program listings. Because program logic information is not necessary for program operation and use, distribution of this manual is restricted to persons with program-maintenance responsibilities.

**Restricted Distribution**

#### PREFACE

This publication provides customer engineers and other technical personnel with information describing the internal organization and logic of the level E linkage editor. It is part of an integrated library of IBM System/360 Operating System Program Logic Manuals. Other publications that are required for an understanding of the linkage editor are:

IBM System/360 Operating System: Introduction to Control Program Logic, Program Logic Manual, Y28-6605

IBM System/360 Operating System: Concepts and Facilities, C28-6535

IBM System/360 Operating System: Assembler Language, C28-6514

The reader should also refer to the co-requisite publication: <u>IBM System/</u> 360 Operating System: Linkage Editor and Loader, C28-6538

This manual consists of three parts:

An Introduction, describing the linkage editor as a whole, including its relationship to the operating system. The major divisions of the program and the relationships among them are also described in this section.

- 2. A section describing each major division of the 15K and 18K versions of linkage editor E. Each major division is discussed in sufficient detail to enable the reader to understand its basic functions, and to provide a frame of reference for the comments and coding supplied in the program listing. Common data, such as tables, control blocks, and work areas, are discussed only to the extent required to understand the logic of the major divisions. Flowcharts are included at the end of this section.

- 3. An Appendix, containing:

- a. The input conventions and record formats for the linkage editor.

- b. The layouts of tables, which may not be essential for an understanding of the basic logic of the program, but are essential for analysis of storage dumps.

If more detailed information is required, the reader should refer to the comments, remarks, and coding in the link-age editor program listings.

Third Edition (June 1967)

The specifications contained in this publication as amended by Technical Newsletter Y28-6400, dated July 23, 1969, correspond to Release 18 of IBM System/360 Operating System.

Changes are periodically made to the specifications herein; any such changes will be reported in subsequent revisions or Technical Newsletters.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

Comments may be addressed to IBM Corporation, Programming Publications, 1271 Avenue of the Americas, New York, New York 10020.

© International Business Machines Corporation 1969

# CONTENTS

| Section 1: Introduction                                                 |    | - 7  |

|-------------------------------------------------------------------------|----|------|

| Purpose of Linkage Editor                                               | -  | 7    |

| Purpose of Linkage Editor                                               |    | 7    |

| General Description                                                     | •  | 8    |

| General Description                                                     | •  | 8    |

| Module Scructure                                                        | •  | 8    |

| External Symbol Dictionary                                              |    |      |

| Relocation Dictionary                                                   | •  | 9    |

| Composite Dictionaries                                                  | •  | 9    |

| Options                                                                 | ٠  | 9    |

| Module Attributes                                                       | •  | 12   |

| Main Storage Hierarchy Support                                          |    | 13   |

| Major Divisions of Linkage Editor                                       |    | 13   |

| Initial Processing                                                      | Ţ  | 1 1  |

| Initial Processing                                                      | •  | 1 /1 |

| Input Processing (First Pass)                                           | •  | 14   |

| Intermediate Processing                                                 | ٠  | 14   |

| Second Pass Processing                                                  | ٠  | 14   |

| Final Processing                                                        | •  | 14   |

| Input/Output Flow                                                       |    | 14   |

| Internal Data Flow                                                      |    | 15   |

|                                                                         | •  |      |

| Section 2: Discussion of Major                                          |    |      |

| Section 2: Discussion of Major                                          |    | 47   |

|                                                                         | ٠  | 1/   |

| Divisions<br>Initial Processor<br>Main Storage Allocation - 15K and 18B | ٠  | 17   |

| Main Storage Allocation - 15K and 18B                                   | ζ. |      |

| Level E                                                                 |    | 21   |

| Input Processor                                                         |    | 21   |

| Object Module Processor                                                 |    | 22   |

| Load Module Processor                                                   | -  | 22   |

|                                                                         | •  | 2.5  |

| ESD Processor                                                           | •  | 24   |

| ESD Record Types                                                        | ٠  | 24   |

| ESD Record Types                                                        | ٠  | 24   |

| ESD Processing                                                          | •  | 25   |

| TXT and RLD Processor - 15K and 18K                                     |    |      |

| Level E                                                                 |    | 28   |

| TXT Processing                                                          |    |      |

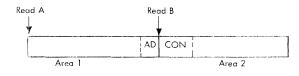

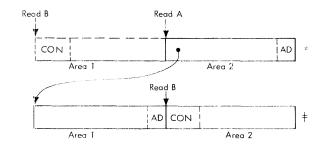

| Processing Out-of-Order Text                                            | •  | 20   |

| Processing out-or-order lext                                            | •  | 20   |

| RLD Processing                                                          | ٠  | 29   |

| End Processor                                                           | ٠  | 31   |

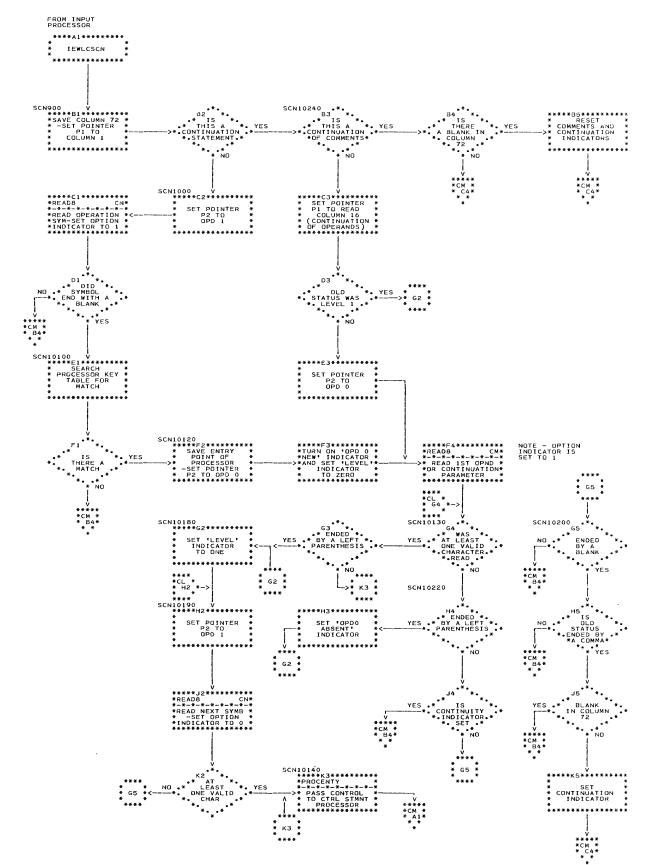

| Control Statement Scanner                                               | •  | 31   |

| Control Statement Processors                                            | •  | 32   |

| Include Processor                                                       |    | 35   |

| Include Processor                                                       |    | 37   |

| Address Assignment Processor                                            | -  | 38   |

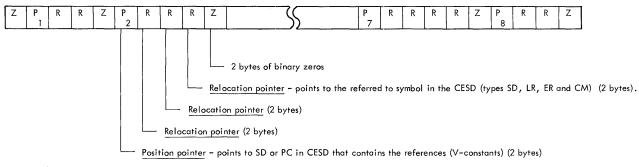

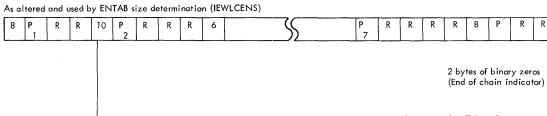

| ENTAR Size Determination Poutine                                        | •  | 10   |

| ENTRO SIZE Decermination Routine .                                      | •  | 40   |

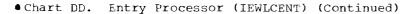

| Entry Processor                                                         | •  | 42   |

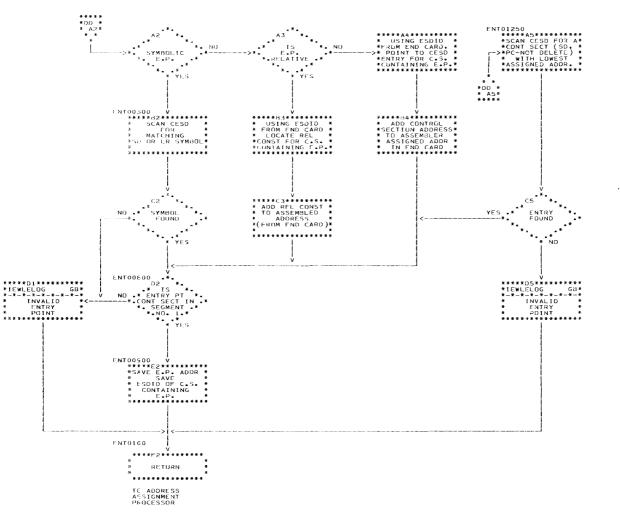

| Intermediate Output Processor                                           | •  | 43   |

| Second Pass Processor                                                   | •  | 44   |

| Second Pass Operation - 15K and 18K                                     |    |      |

| Level E                                                                 | •  | 44   |

| Relocation of Address Constants                                         | •  | 45   |

| Relocation of Non-Branch Type                                           |    |      |

| (A-Type) Address Constants                                              | _  | 45   |

| Relocation of Branch Type (V -                                          | •  | 10   |

| Type) Address Constants                                                 |    | 49   |

|                                                                         | •  |      |

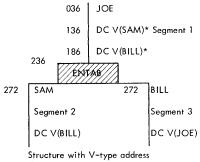

| ENTAB Creation                                                          | •  | 50   |

| "Split" Address Constants - Level H                                     | 5  | 52   |

| Relocation Routine - Level E                                            | •  | 52   |

| Final Processor - 15K and 18K Level E                                   | •  | 54   |

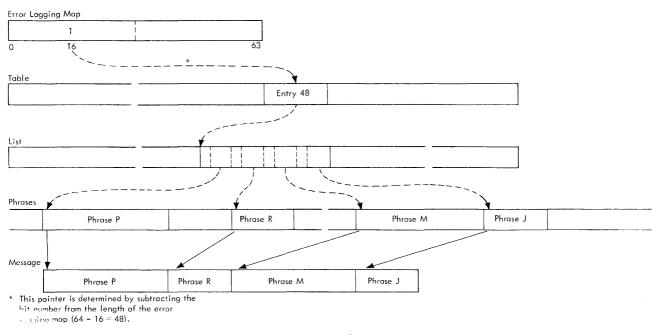

| Error Logging                                                           | •  | 55   |

| Input/Output Error Handling                                             |    | 56   |

| Module MAP and Cross-Reference Table                                    | _  | 56   |

| manual and cross hererence funct                                        | •  |      |

| LEVEL E FLOWCHARTS                                       | . 57                 |

|----------------------------------------------------------|----------------------|

| Microfiche Directory                                     | . 57                 |

| Microffiche Directory                                    | • 51                 |

| Appendix A. Deference Data For Level                     |                      |

| Appendix A: Reference Data For Level<br>E Linkage Editor | . 90                 |

|                                                          | ~ ~ ~                |

| Input Conventions                                        | 0.4                  |

| Record Formats                                           |                      |

| Record Formats - Level E                                 |                      |

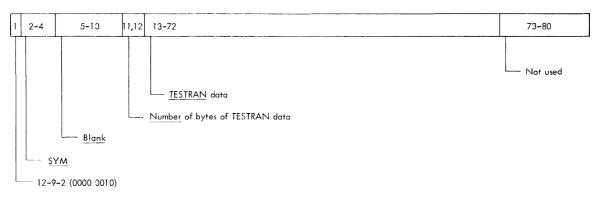

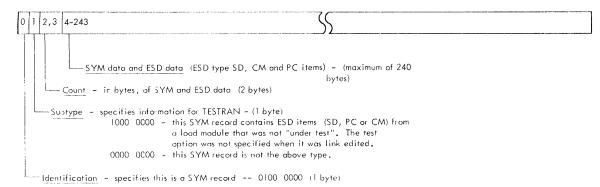

| SYM Input Record (Card Image)                            |                      |

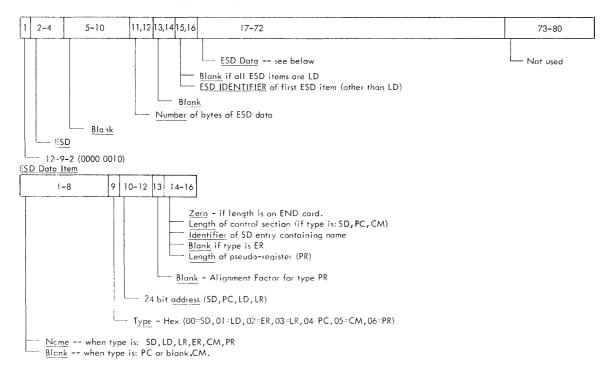

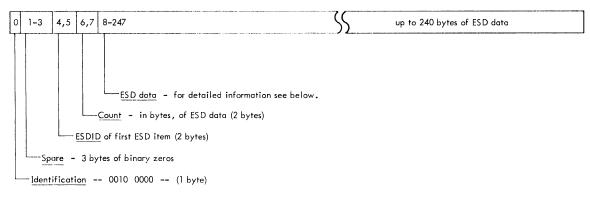

| ESD Input Record (Card Image)                            | . 92                 |

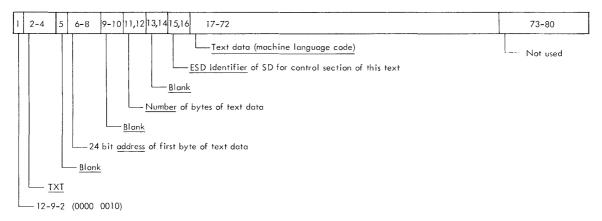

| Text Input Record (Card Image)                           | . 93                 |

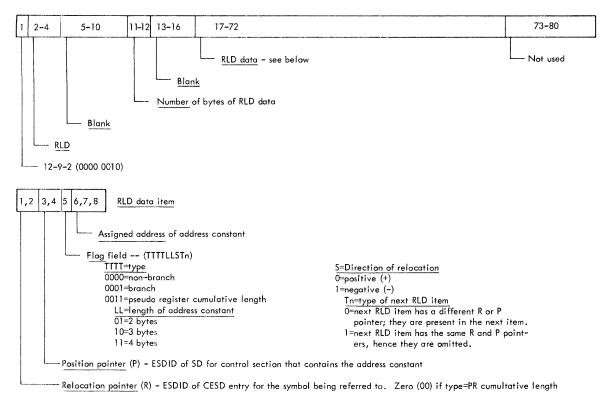

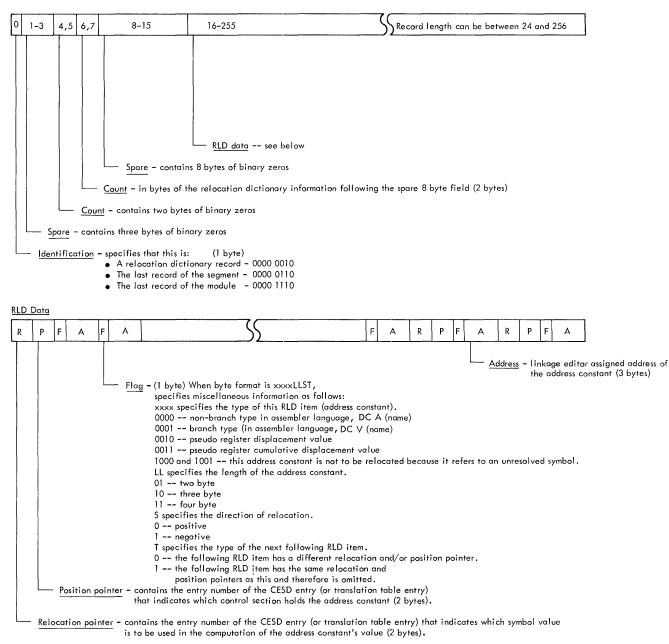

| RLD Input Record (Card Image)                            | . 93                 |

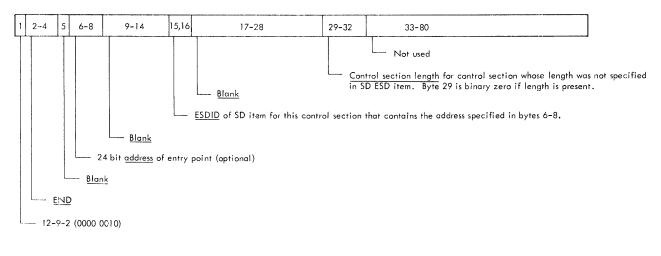

| END Input Record - Type 1                                |                      |

| (Card Image)                                             | . 94                 |

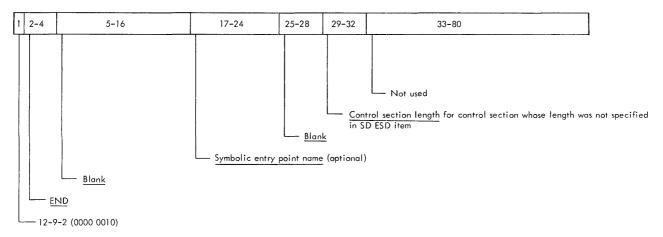

| END Input Record - Type 2                                | • ) !                |

|                                                          | . 94                 |

|                                                          |                      |

| SYM Record - (Load Module)                               |                      |

| CESD Record - (Load Module)                              | . 96                 |

| Scatter-Translation Record                               |                      |

| Control Record - (Load Module)                           | <b>.</b> 98          |

| Relocation Dictionary Record -                           |                      |

| (Load Module)                                            | . 99                 |

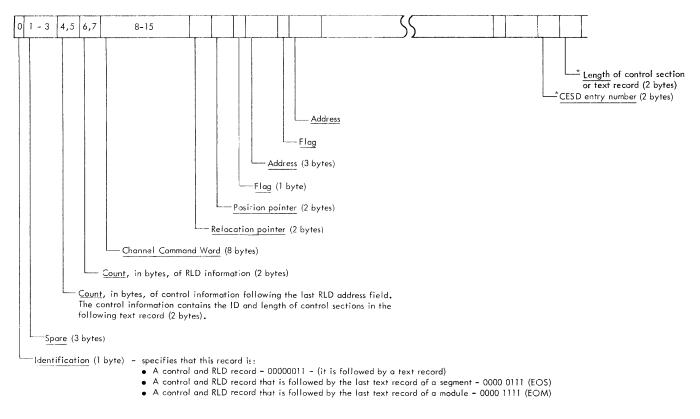

| Control and Relocation Dictionary                        |                      |

| Record - (Load Module)                                   | -100                 |

| Reference Data For Initial                               |                      |

| Processing - 15K and 18K Level E                         | 101                  |

| All Purpose Table                                        |                      |

|                                                          |                      |

| Main Storage Allocation Table                            | .106                 |

| Minimum Table Area for Processing                        |                      |

| Non-Overlay Programs                                     | .107                 |

| Expansion of Table Area Into Extra                       |                      |

| Available Main Storage                                   |                      |

| (Non-Overlay Processing)                                 | .107                 |

| Minimum Table Area for Processing                        |                      |

| Overlay Programs                                         | .108                 |

| Expansion of Table Area Into Extra                       |                      |

| Available Main Storage (Overlay                          |                      |

| Processing)                                              | .109                 |

| Table of Buffer Sizes and Table                          | • 1 0 )              |

| •                                                        | 110                  |

|                                                          | .110                 |

| Reference Data for Input Processing                      |                      |

| Level E                                                  | .111                 |

|                                                          | .111                 |

| Calls List                                               | .111                 |

|                                                          | .111                 |

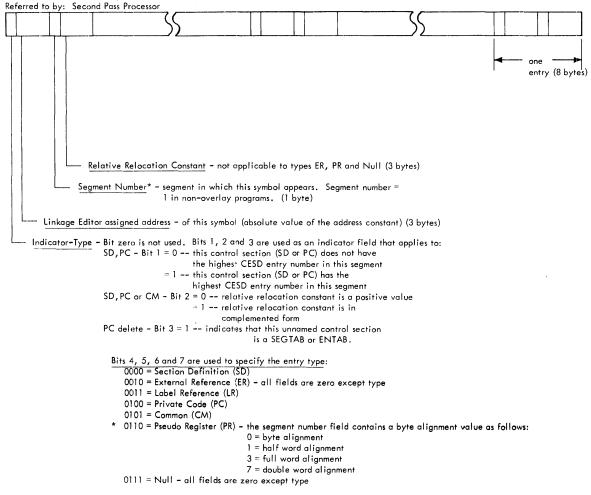

| Composite External Symbol                                |                      |

| Dictionary (CESD) Internal                               |                      |

| Format                                                   | .112                 |

| Normal Combination of Internal                           |                      |

| CESD Types                                               | .113                 |

| Delink Table                                             | .114                 |

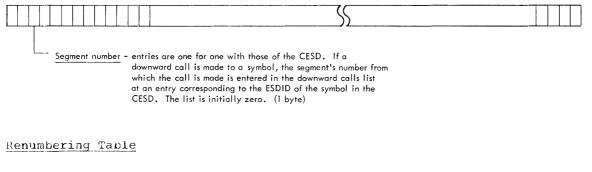

| Downward Calls List                                      | .114                 |

|                                                          | .114                 |

|                                                          |                      |

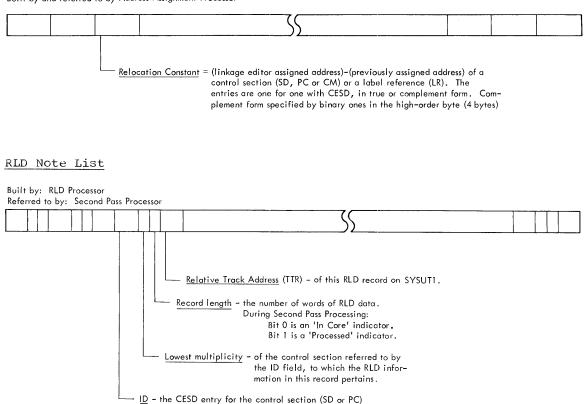

| Relative Relocation Constant Table                       |                      |

| RLD Note List                                            | .115                 |

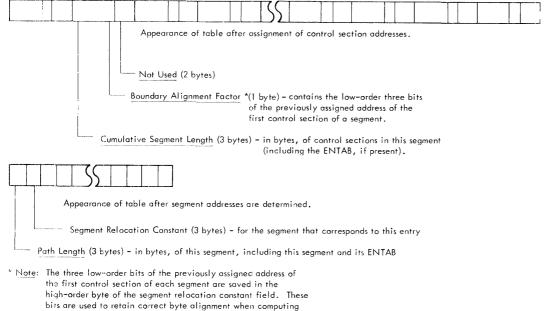

| Segment Length Table                                     |                      |

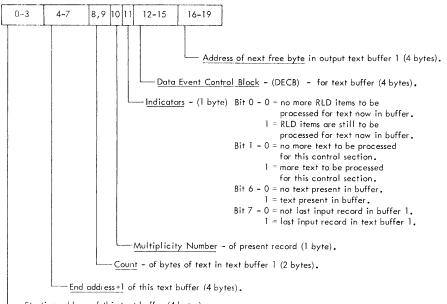

| Text Input/Output Table                                  | <b>.1</b> 15         |

|                                                          | .115<br>.116         |

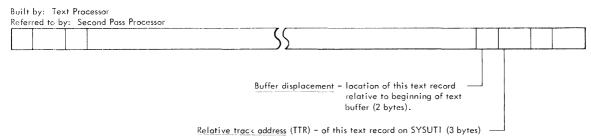

| Text Note List                                           | <b>.1</b> 15         |

| Text Note List                                           | •115<br>•116<br>•116 |

| Text Note List                                           | .115<br>.116         |

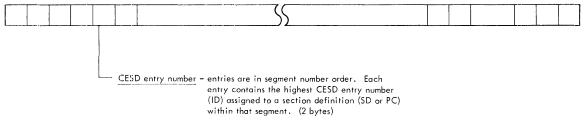

| Half External Symbol Dictionary118  |

|-------------------------------------|

| High ID Table                       |

| Reference Data for Second Pass      |

| Processing Level E                  |

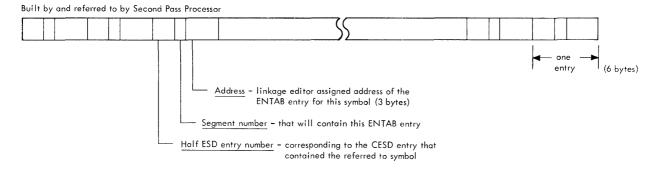

| Entry List                          |

| Entry Table (ENTAB)                 |

| Text Table I                        |

| Text Table II                       |

| Reference Data for Final Processing |

| Level E                             |

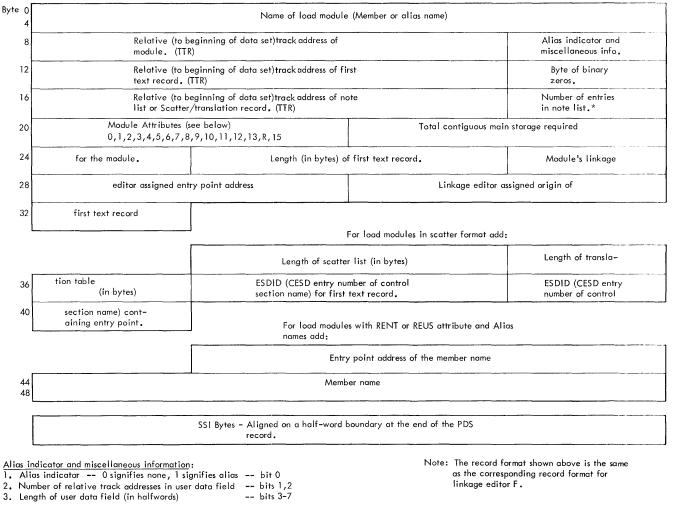

| Partitioned Organization Directory  |

| Record                              |

| Module Attributes                   |

| Partitioned Organization Directory  |

| Record                              |

|                                     |

| .24 |

|-----|

| 24  |

| 24  |

| 24  |

| 25  |

|     |

| 25  |

|     |

| 26  |

|     |

| 27  |

|     |

| 27  |

|     |

| 30  |

|     |

| 31  |

|     |

#### FIGURES

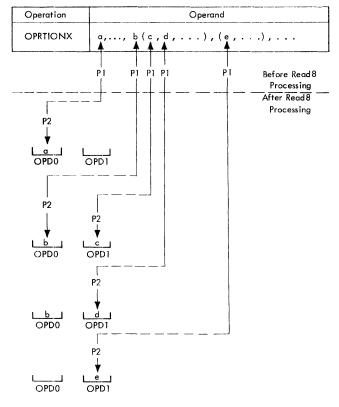

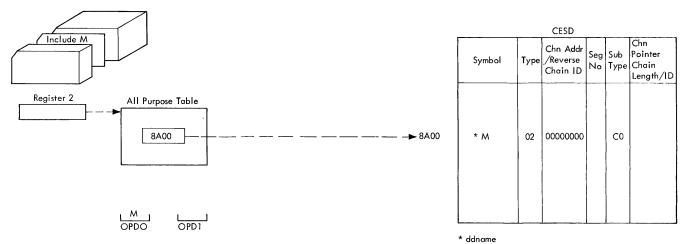

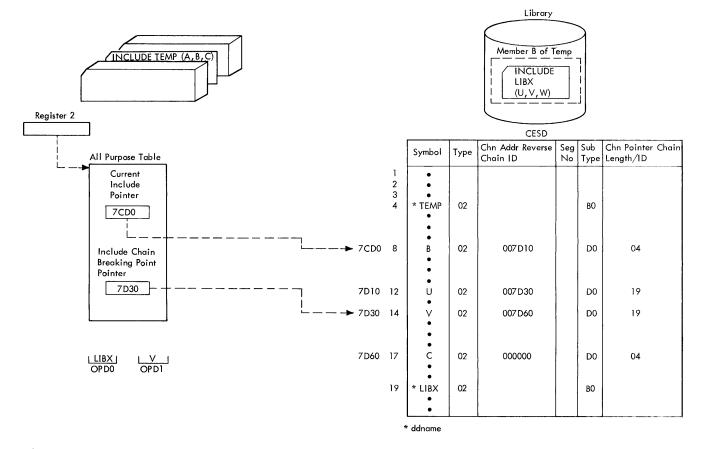

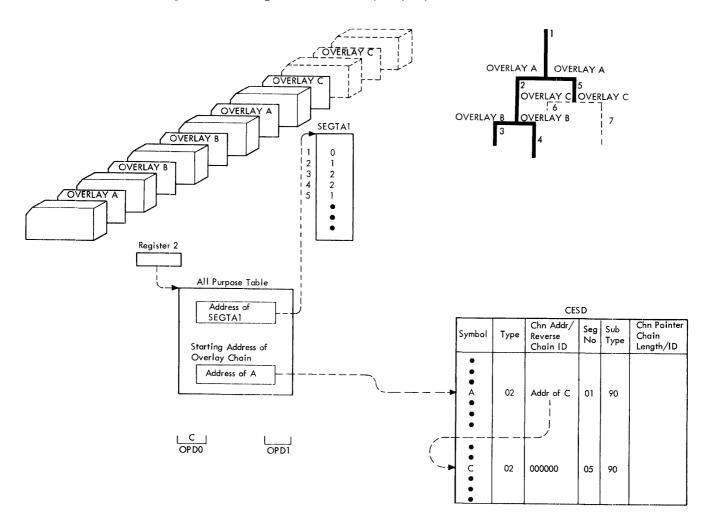

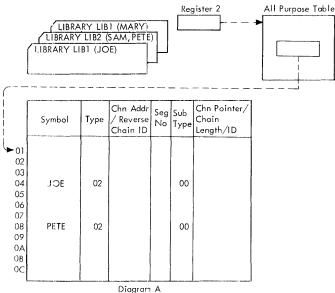

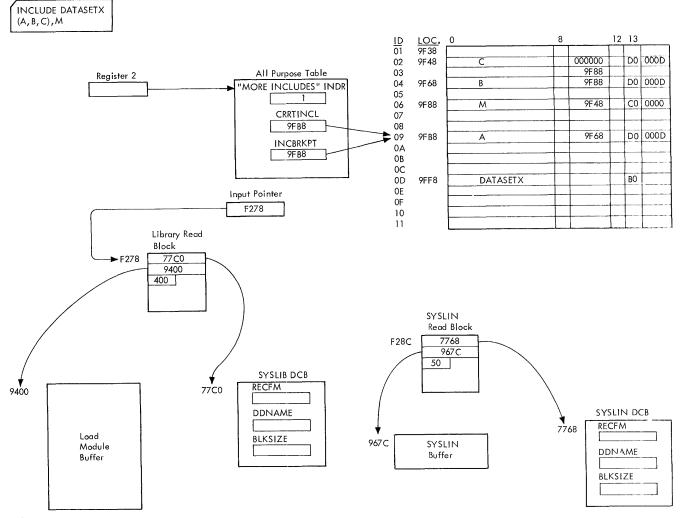

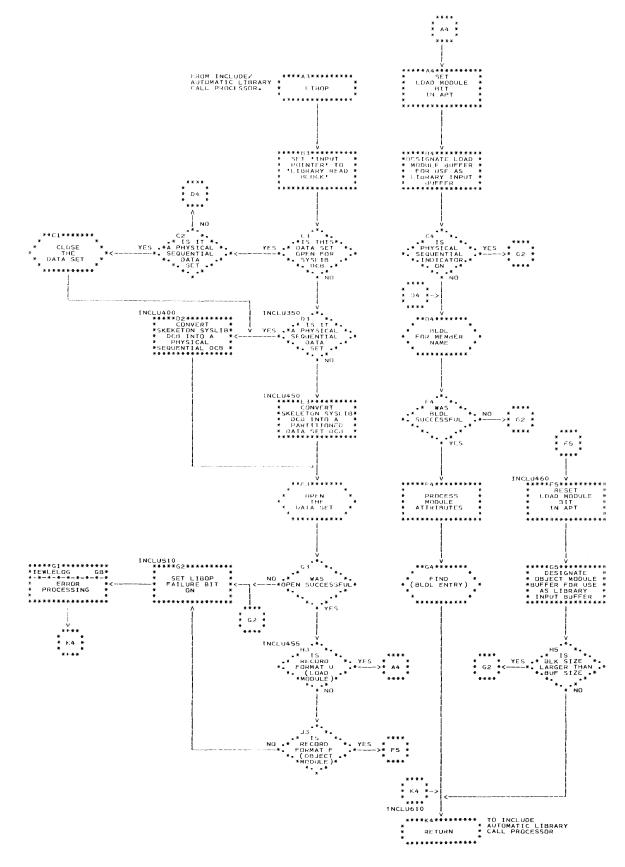

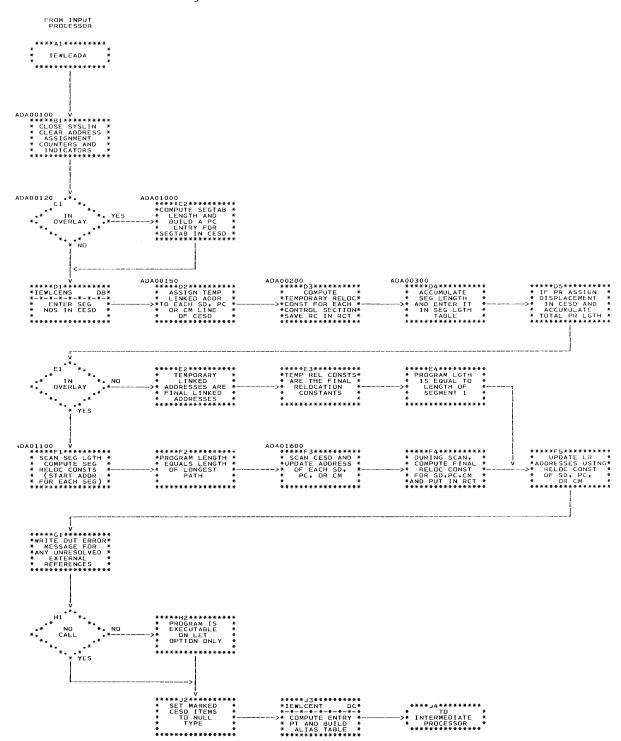

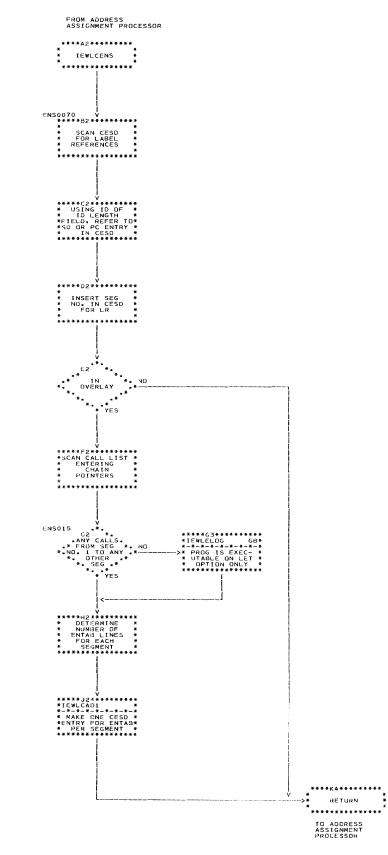

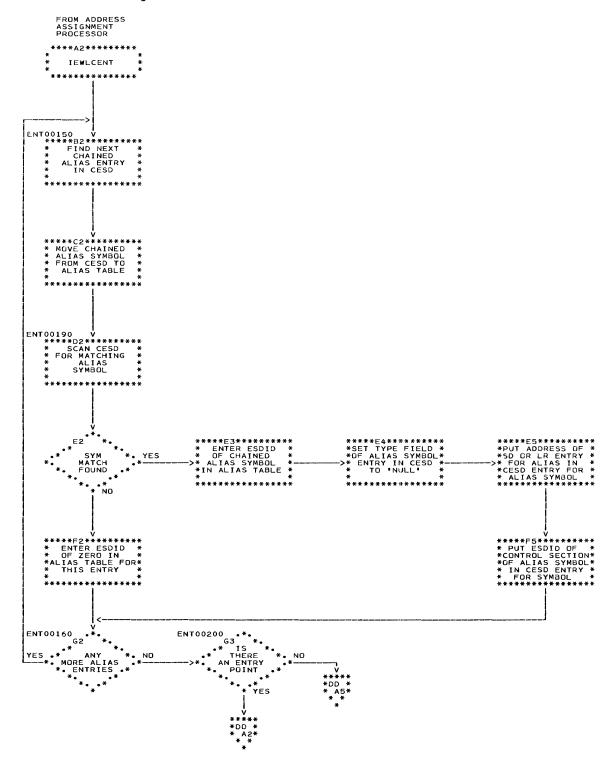

Figure 1. Linkage Editor Processing - Simple Case Figure 2. Combining Control Figure 3. Linkage Editor Processing - Using Overlay and Test Options . . . . . . . . 11 Figure 4. Linkage Editor Processing - Using Scatter Load Figure 5. Input/Output Flow . . . 15 Figure 6. Internal Data Flow . . 16 Figure 7. Level E Linkage Editor Figure 9. Include Statement Processing for a Sequential Data Processing With Nested Members . . 33 Figure 11. Overlay Statement Processing ..... Figure 12. Library Statement Processing ••••••••••

Figure 13. Include Processing . . 37 Figure 14. Automatic Library Call Processing ..... Figure 15. ENTAB Size Determination .... • • • • • 40 Figure 16. Processing of Alias Symbols by the ENTRY Processor . . 41 Figure 17. Writing Scatter/Translation Records . . . . 44 Figure 18. Non-Branch Type Address Constants - Relative Relocation . . . . . . . . . . . . . . . . 46 Figure 19. Non-Branch Type Address Constants - Absolute Relocation . . . . . . . . . . 46 Figure 20. Non-Branch Type Address Constants - Absolute and Relative Relocation . . . . . . . 47 Figure 21. Example of Delinking . 48 Figure 22. Entry List Processing . 50 Figure 23. ENTAB Creation . . . 51 Figure 24. Split Address Constants in the Second Pass Text Messages (Level E) .... 55

# TABLES

|         |      | Incompatible Module |   |

|---------|------|---------------------|---|

| Attribu | tes  | 1                   | 7 |

| Table   | 2.   | General Register    |   |

| Informa | tior | n - Object Module   |   |

| Process | ing  | 2                   | 2 |

|         |      | Record Types and    |   |

| Associa | teđ  | Processors 2        | 3 |

| Table   | 4.   | General Register      |   |   |

|---------|------|-----------------------|---|---|

| Informa | atio | n - Load Module       |   |   |

| Process | sing |                       | 2 | 4 |

| Table   | 5.   | Flag Field Processing | 3 | 1 |

| Table   | 6.   | Relationship of RLD   |   |   |

| Flag F: | ield | to Relocation         | 5 | 4 |

| Table   | 7.   | Error Message Module  |   |   |

| Cross I | Refe | rence Table           | 5 | 6 |

|         |      |                       |   |   |

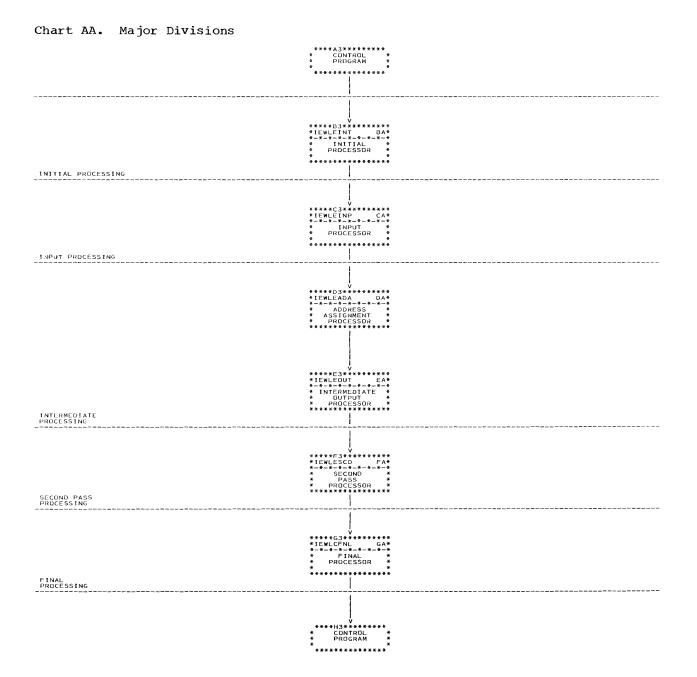

### CHARTS

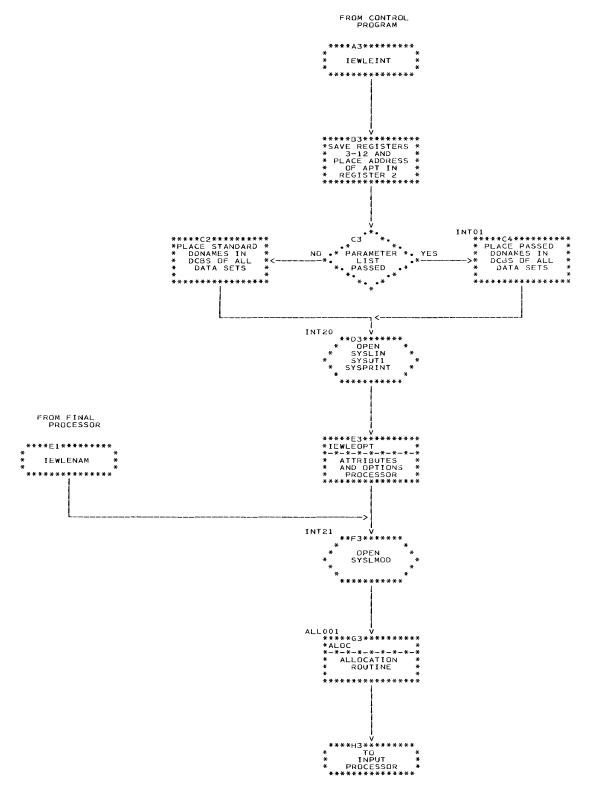

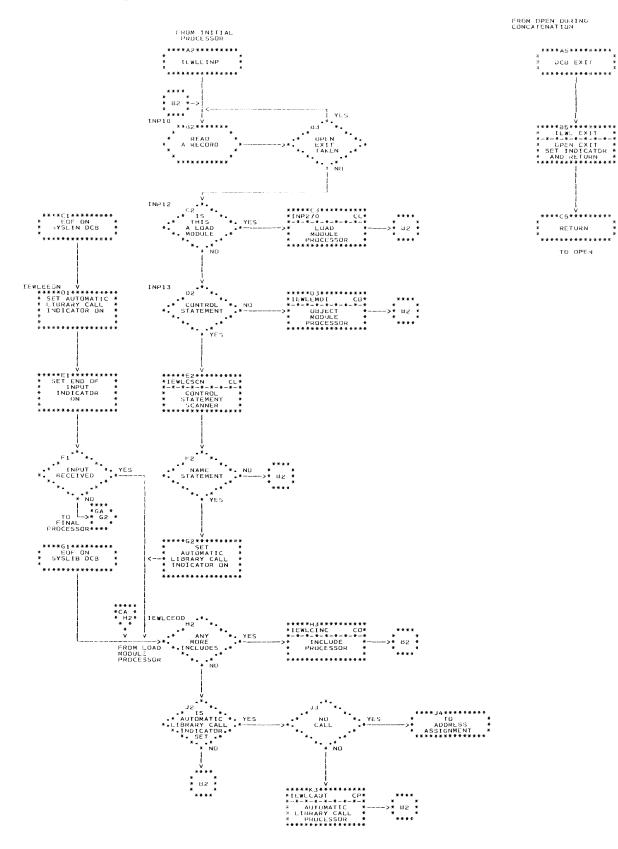

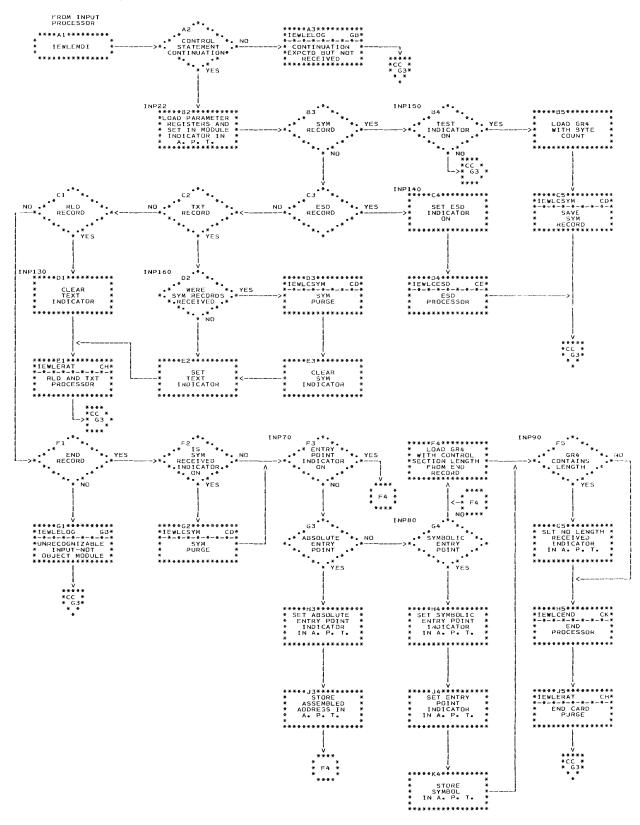

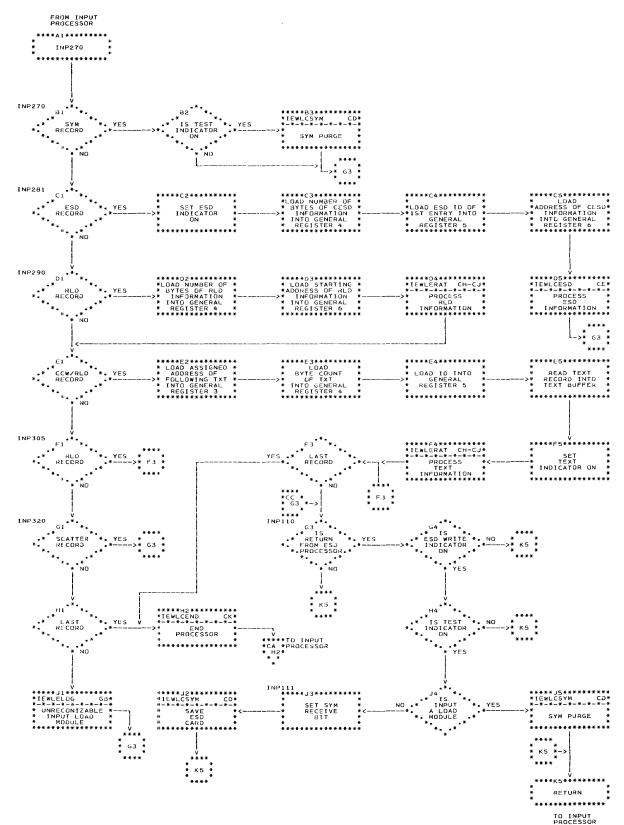

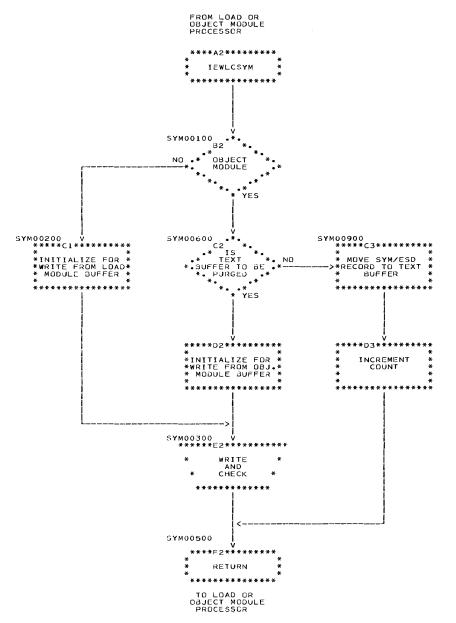

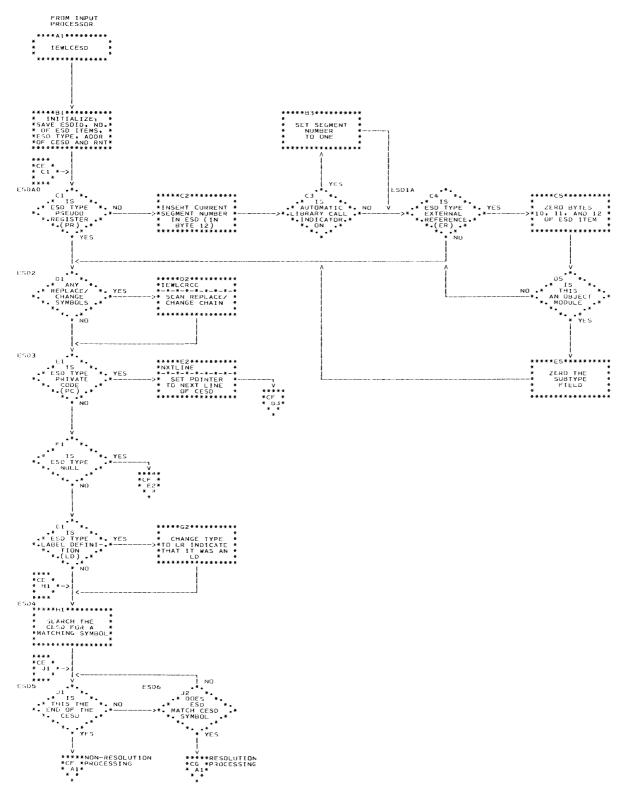

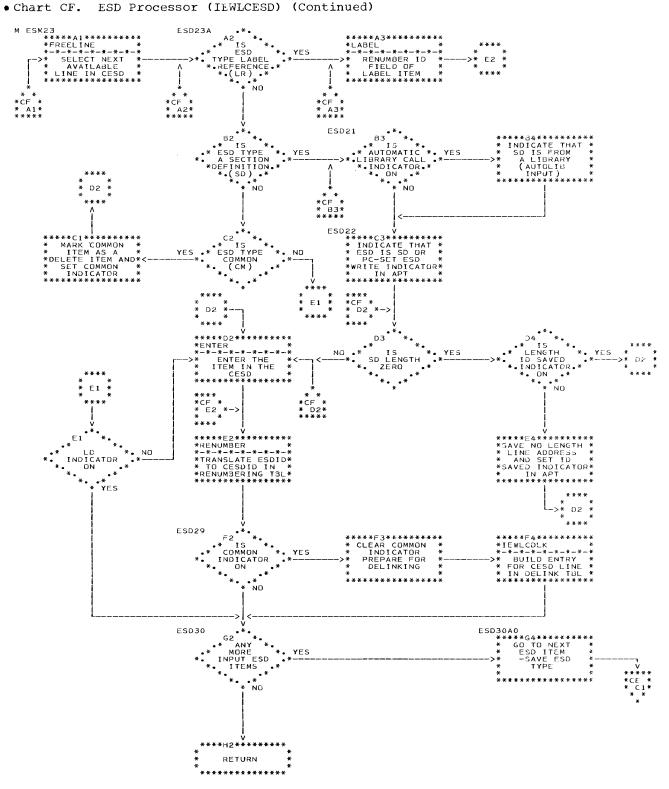

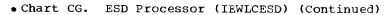

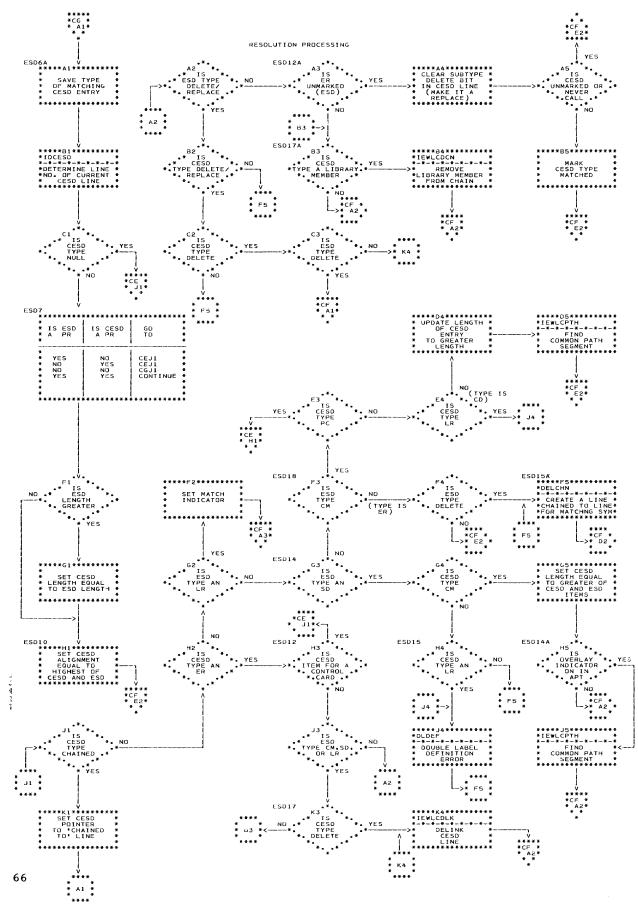

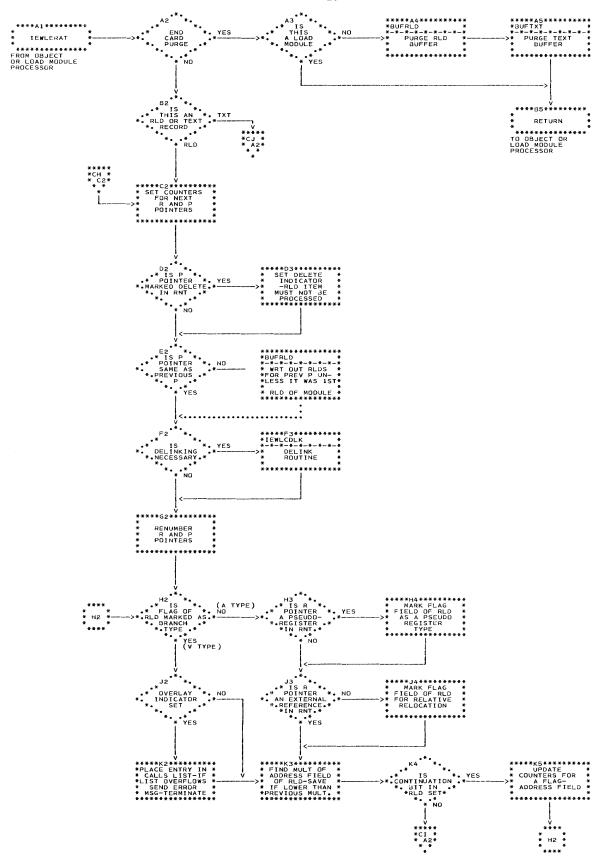

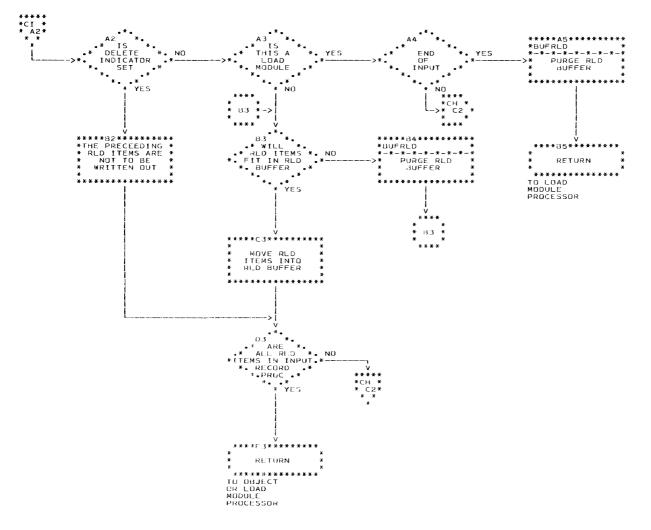

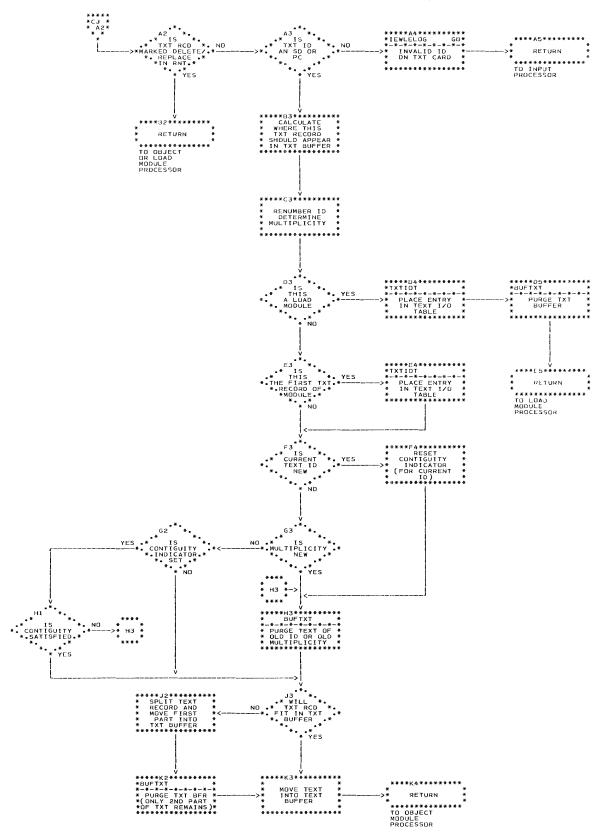

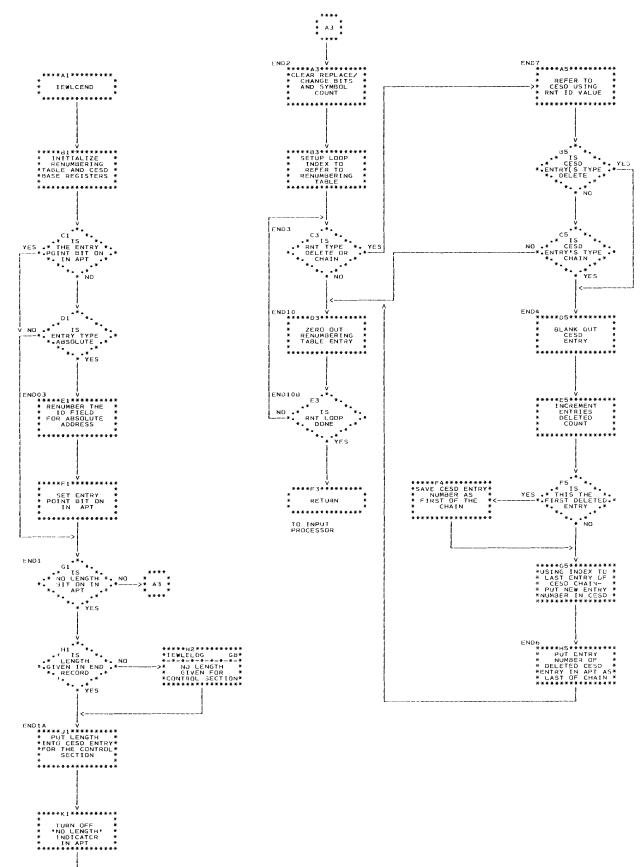

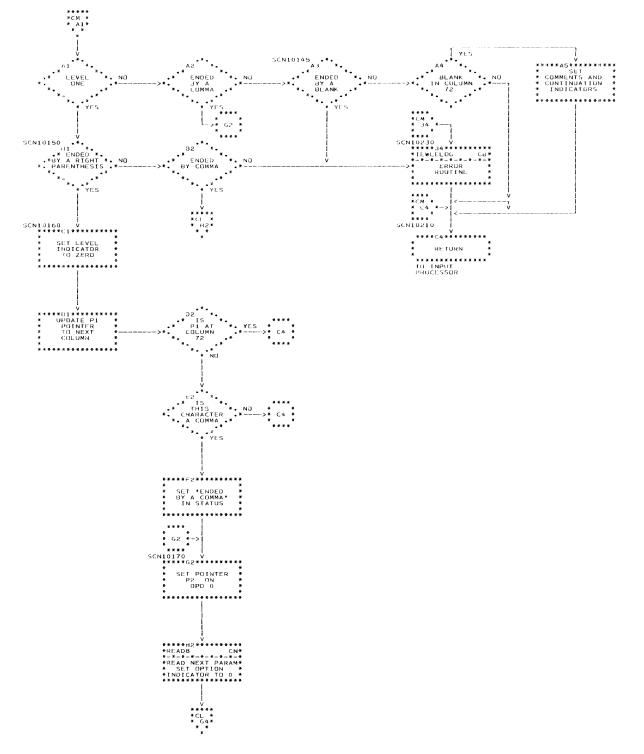

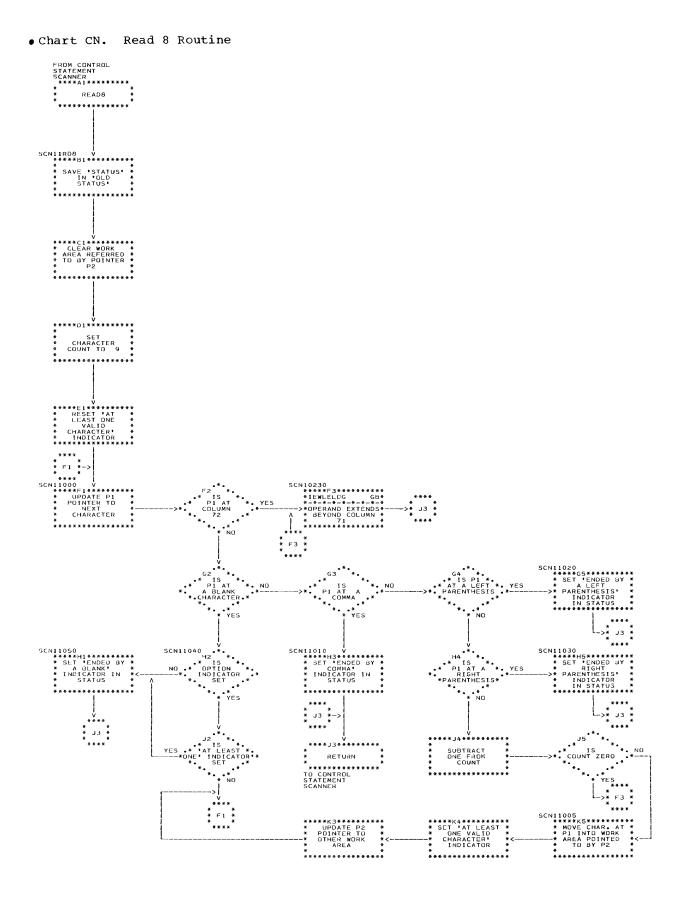

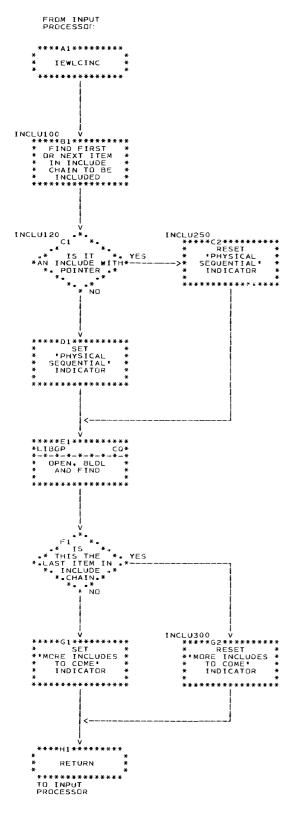

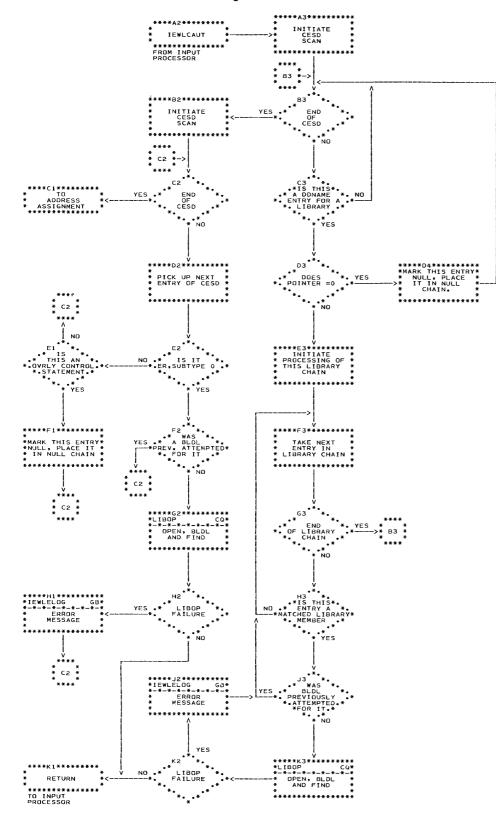

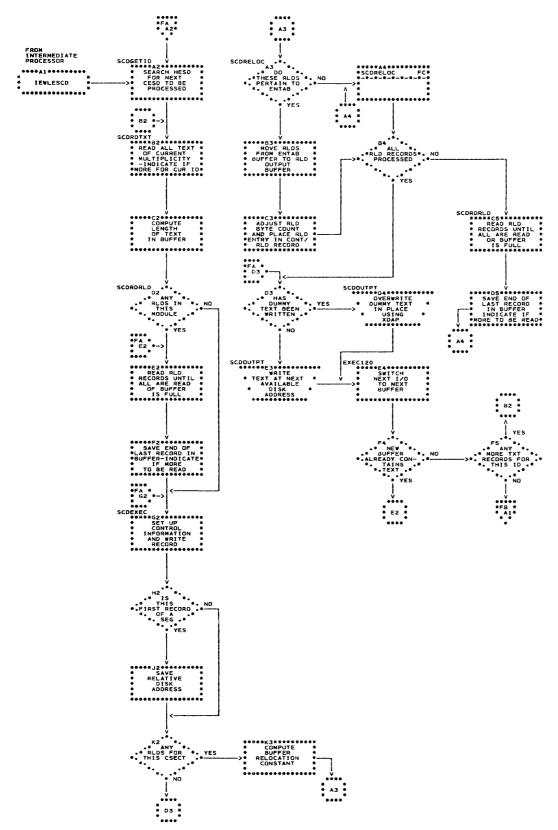

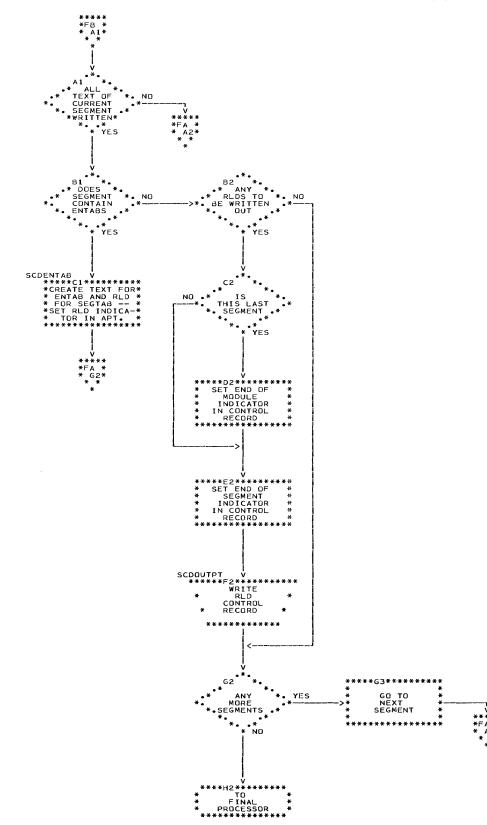

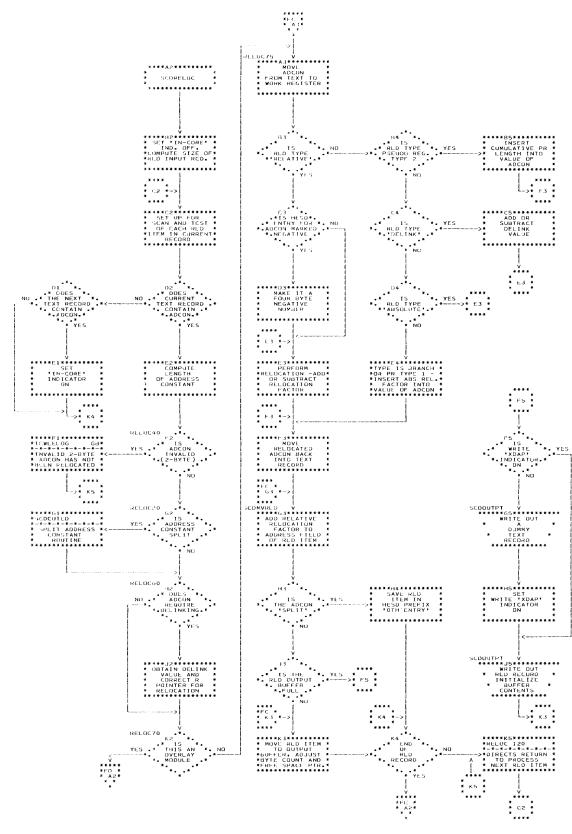

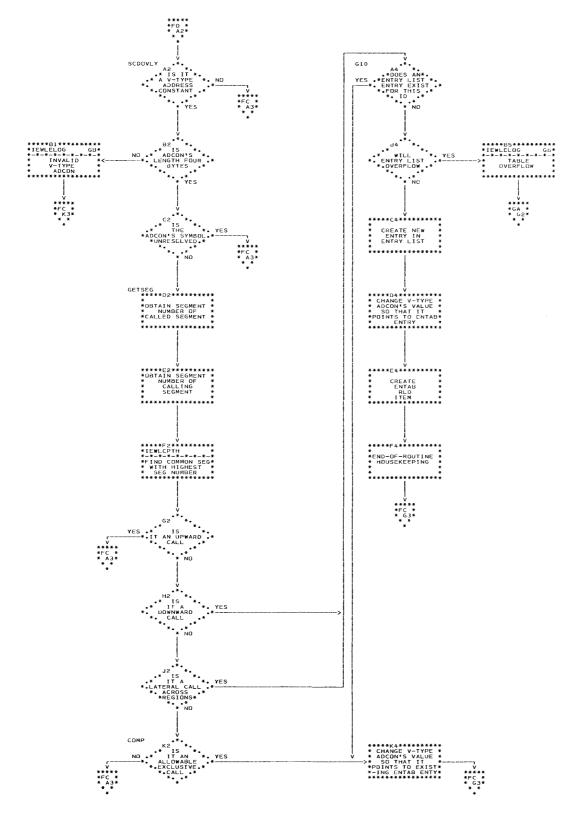

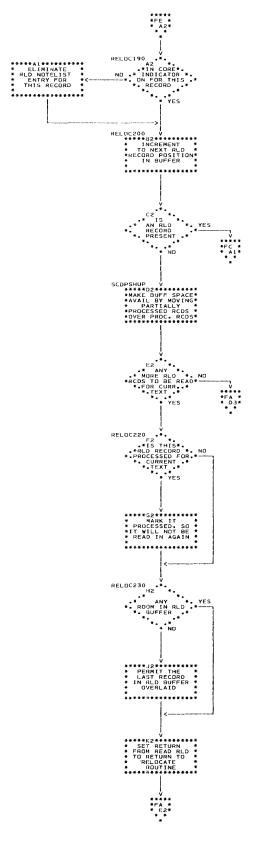

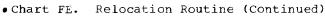

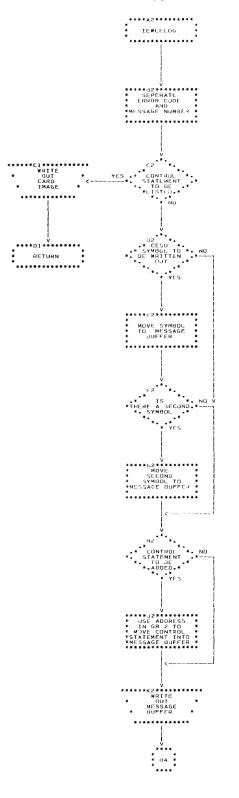

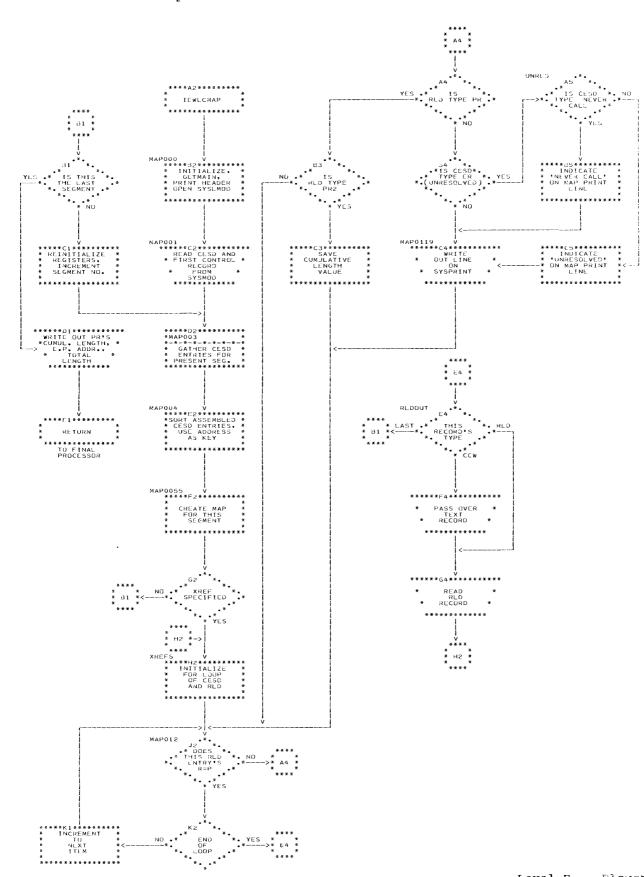

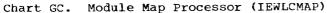

Chart AA. Major Divisions . . . . 58 Chart BA. Initial Processor Chart CA. Input Processor (IEWLEINP) . . . . . . . . . . . . . 60 Chart CB. Object Module Processor (IEWLEMDI) . . . . . . . . . . . . . . . . 61 Chart CC. Load Module Processor Chart CE. ESD Processor (IEWLCESD) 64 Chart CF. ESD Processor (IEWLCESD) (Continued) . . . . . . 65 Chart CH. TXT and RLD Processor (IEWLERAT) . . . . . . . . . . . . . . . . . 67 Chart CK. END Processor (IEWLCEND) 70 Chart CL. Control Statement Chart CM. Control Statement Scanner (IEWLCSCN) (Continued) . . . 72 Chart CN. Read 8 Routine . . . . 73 Chart CO. Include Processor

Chart CP. Automatic Library Call Processor (IEWLCAUT) . . . . . . . . 75 Chart CQ. Library Open Routine Chart DB. IEWLCENS Routine .... 78 Chart DC. Entry Processor (IEWLCENT) (Continued) . . . . . . 80 Chart EA. Intermediate Output Processor (IEWLEOUT) . . . . . . . . . . . . 81 Chart FA. Second Pass Processor Chart FB. Second Pass Processor (IEWLESCD) (Continued) . . . . . . 83 Chart FC. Relocation Routine . . . 84 Chart FD. Relocation Routine Chart FE. Relocation Routine Chart GA. Final Processor Chart GB. Error Logging Routine Chart GC. Module Map Processor | Chart GD. SYNAD Routine . . . . . 90

SECTION 1: INTRODUCTION

This section provides general information describing the purpose, organization, and internal operation of the linkage editor, and its relationship to the operating system.

The level E linkage editor is available in 15K and 18K versions; they differ in speed, table sizes, and overlay structure. All versions of the linkage editor operate in essentially the same manner.

#### PURPOSE OF LINKAGE EDITOR

The linkage editor is one of the processing programs of IBM System/360 Operating System. It is a service program used in association with the language translators to prepare machine-language programs from symbolic-language programs written in FOR-TRAN, COBOL, report program generator, the assembler language, or PL/I. Linkage editor processing is a necessary step that follows source program assembly or compilation.

Linkage editor processing allows the programmer to divide his program into several parts, each containing one or more control sections. Each part may then be coded in the programming language best suited to it and may then be separately assembled or compiled by a language translator (under the rules applicable to each language translator).

The primary purpose of the linkage editor is to combine and link object modules (the output of the language translators) into a load module in which all cross references between control sections are resolved as if they had been assembled or compiled as one module. The load module produced by the linkage editor consists of executable machine-language code in a format that can be loaded into main storage and relocated by program fetch.

In addition to combining and linking object modules, the linkage editor performs the following functions:

• <u>Library Call Processing</u>. Modules (such as standard subroutines) stored in a library can be placed in the input to linkage editor, either automatically or upon request. If unresolved external references remain after all input to the linkage editor is processed, an automatic library call routine retrieves the modules required to resolve the references.

- <u>Program Modification</u>. Control sections can be replaced, deleted, or rearranged (in overlay programs) during linkage editor processing, as directed by linkage editor control statements. Common control sections generated by the FOR-TRAN, PL/I, and assembler language translators are provided locations within the output load module.

- Overlay Module Processing. Linkage editor prepares modules for overlay by assigning relative locations within the module to the overlay segments and by inserting tables to be used by the overlay supervisor during execution.

- Options and Error Messages. The linkage editor can:

- Process special options that override automatig library calls or the effect of minor errors.

- 2. Produce a list of linkage editor control statements that were processed.

- 3. Produce coded diagnostic messages and a directory describing those diagnostic messages that were printed out during linkage editor processing.

- 4. Produce a module map or crossreference table of control sections in the output load module.

#### RELATIONSHIP TO THE OPERATING SYSTEM

The linkage editor has the same relationship to the operating system as any other processing program. Control is passed to the linkage editor in one of three ways:

- As a job step, when the linkage editor is specified on an EXEC job control statement in the input stream.

- 2. As a subprogram, via the execution of a CALL macro instruction (after execution of a LOAD macro instruction), a LINK macro instruction, or an XCTL macro instruction.

3. As a subtask, in multitasking systems, via execution of the ATTACH macro instruction.

#### GENERAL DESCRIPTION

Linkage editor input may consist of a combination of object modules, load modules, and linkage editor control statements. The prime function of the linkage editor is to combine these modules, in accordance with requirements stated on control statements, into a single output load module that can be relocated and loaded into main storage by program fetch for execution. Output load modules are placed in partitioned data sets (libraries).

Each module to be processed by linkage editor has an origin that was assigned during assembly, during compilation, or during a previous execution of the linkage editor. Each module in the input to linkage editor may contain symbolic references to control sections in other modules; such references are called external references.

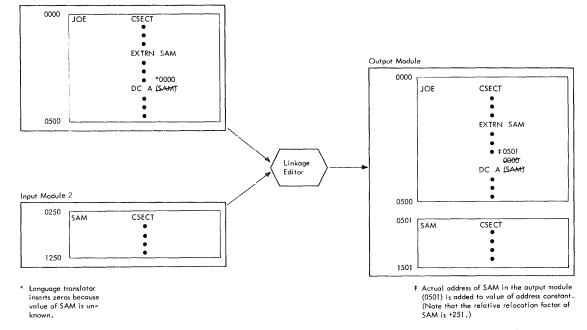

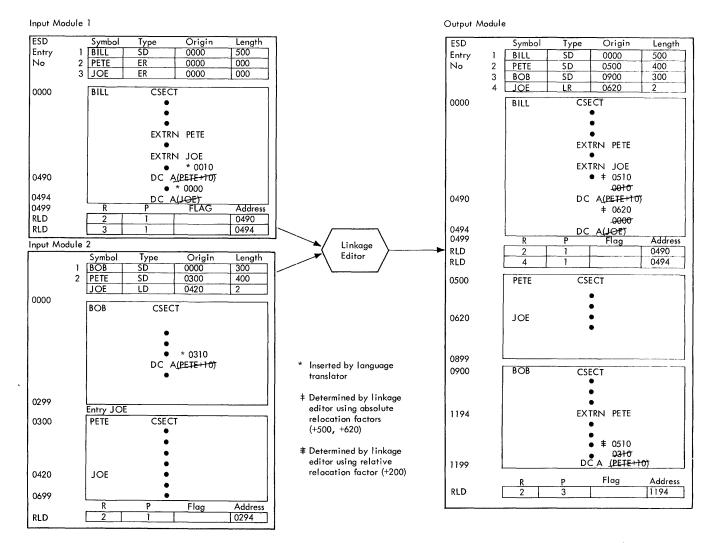

To produce an executable output load module, the linkage editor:

- 1. Assigns relative main storage addresses to the control sections to be included in the output module. Since each input module has an origin that was assigned independently by a language translator, the order of the addresses in the input is unpredictable. (Two input modules, for example, may have the same origin.) Linkage editor assigns an origin to the first control section and then assigns addresses, relative to this origin, to all other control sections in the output.<sup>1</sup> Each item in a control section is relocated the same number of bytes as the control section origin.

- 2. Resolves external references in the input modules. Cross references between control sections in different modules are symbolic, and must be resolved (translated into relocatable machine addresses), relative to the contiguous main storage addresses assigned to the output load module. These symbolic cross-references are made by means of <u>address</u> constants. The linkage editor calculates the new address of each relocatable expression

- <sup>1</sup>If the program is in overlay, an origin is assigned to the first control section in each segment. Within each segment, contiguous addresses are assigned relative to the segment origin.

\_\_\_\_\_

in a control section and determines the assigned origin (value) of the item to which it refers.

Linkage editor processing is affected by specified options, operations requested on control statements, module attributes contained in partitioned data set directories, and control information contained within the modules themselves. The following paragraphs describe the relationship of module structure and module attributes to linkage editor processing.

# MODULE STRUCTURE

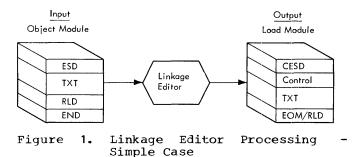

Object modules and load modules have the same basic logical structure (see Figure 1). Each consists of:

- Control dictionaries, containing the information necessary to resolve symbolic cross references between control sections of different modules, and to relocate address constants.

- Text, containing the instructions and data of the program.

- An end of module (EOM) indicator (END statement in object modules; EOM indication in load modules).

Each language translator usually produces two kinds of control dictionaries: an external symbol dictionary (ESD) and a relocation dictionary (RLD). An object module always contains an ESD; a load module contains an ESD, unless it is marked with the "not editable" attribute. Object and load modules usually contain an RLD (unless there are no relocatable address constants in the module). A control dictionary entry is generated whenever an external symbol, an address constant, or the beginning of a control section is processed by a language translator.

# External Symbol Dictionary

The external symbol dictionary contains entries for all external symbols defined or referred to within a module. (An external symbol is one that is defined in one module and can be referred to in another.) Each entry identifies a symbol, or a symbol reference, and gives its location, if any, within the module. When combining input modules, linkage editor resolves references between different input modules by matching the referenced symbols to defined symbols; it does this by searching for the external symbol definitions in each input module's ESD. There is an ESD entry for each named control section and each named common area. The ESD also contains entries that identify unnamed control sections and unnamed common areas.

# Relocation Dictionary

The relocation dictionary (RLD) lists all relocatable address constants that must be modified when the linkage editor produces an output load module. The linkage editor uses the RLD whenever it processes a module. The RLD is also used to adjust the value of address constants after program fetch reads an output load module from a library and loads it into main storage for execution. The RLD contains at least one entry for every relocatable address constant in a module. An RLD entry identifies an address constant by indicating both its location within a control section and the external symbol (in the ESD) whose value must be used to compute the value of the address constant.

### Composite Dictionaries

An output load module is composed of all input object modules and input load modules processed by the linkage editor (except those that are replaced or deleted). The control dictionaries of an output module are therefore a composite of all the control dictionaries in the linkage editor input. The control dictionaries of a load module are called the composite ESD (CESD) and the RLD.

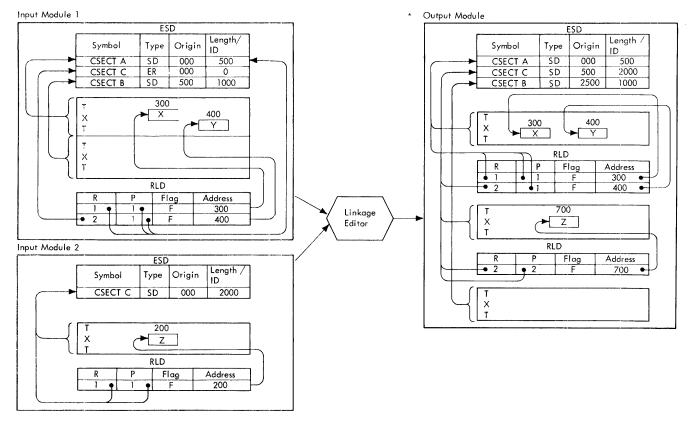

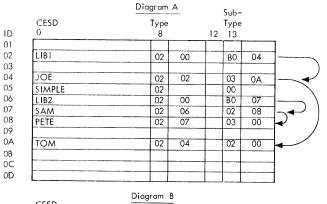

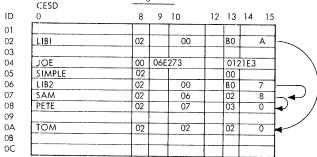

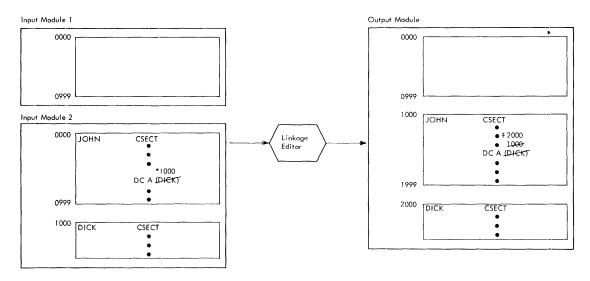

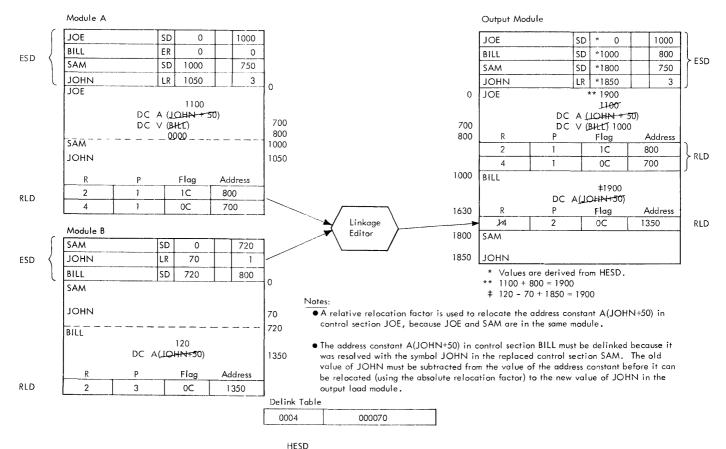

Figure 2 shows how the control dictionaries of two input modules are combined into composite dictionaries by the linkage editor. The control dictionaries and their associated text are interrelated through a system of line numbers and pointers. Within an input module, each ESD item on which an address constant may depend has a line number (ESD identifier, or ESD ID); the line number indicates the position of the item, relative to the other ESD items associated with the text.<sup>1</sup> Every item of text in an object or load module has associated control information that describes it. This control information includes the ESD ID of the ESD item for the control section that contains the text. (In Figure 2, the ESD ID of the text item that contains X and Y points to line 1 of the ESD for input module 1. The ESD ID of the text item containing Z points to line 1 of the ESD for input module 2.)

Each RLD item must point to two ESD items:

- 1. The ESD item for the symbol on which the address constant depends. This is referred to by the RLD <u>relocation</u> <u>pointer</u> (R pointer).

- 2. The ESD item for the control section that contains the address constant. This is referred to by the RLD <u>posi-</u> <u>tion pointer</u> (P pointer).

In input module 1, X and Y are address constants. X refers to the ESD item for the control section in which it resides (CSECTA); therefore, both pointers of its associated RLD item refer to the ESD entry for the control section (line 1). Y refers to an external reference symbol (CSECTC); therefore, the R pointer of its associated RLD points to the ESD entry for the external reference (line 2), whereas the P pointer refers to the ESD entry for its control section (line 1).

When the linkage editor combines the input modules, it must maintain this system of pointers by renumbering the ESD items to reflect their relative positions in the CESD of the output module. It must also update the RLD pointers and control information for the text so that they refer to the renumbered CESD items; the resulting CESD and RLD items are shown in Figure 2.

Note: Figure 2 is intended to show only the relationship between ESD, text, and RLD items before and after linkage editor processing; the output module structure shown applies only to the level E linkage editor.

#### Options

Module structure also depends on selected options. Figure 1 shows a simple case in which a single object module, containing only one control section, is processed by the linkage editor for block loading.

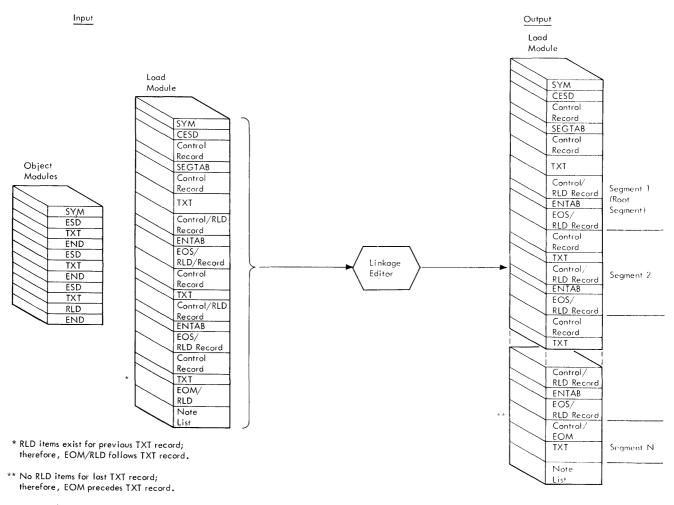

Figure 3 shows the processing of an object module and a load module, each containing several control sections. In this example, test translator macro instructions were included in an assembler language source program and test symbol (SYM) records were produced by the assembler language translator. The TEST and overlay options have been specified on the execute (EXEC) statement and overlay con-

<sup>&</sup>lt;sup>1</sup>In an object module, one type of ESD item (LD) may not have associated text or address constants that depend on it. (Refer to "ESD Processor.") Such ESD items are excluded from the numbering system.

• Figure 2. Combining Control Dictionaries

trol statements have been included in the input to linkage editor. With these options, the output load module produced by the linkage editor contains:

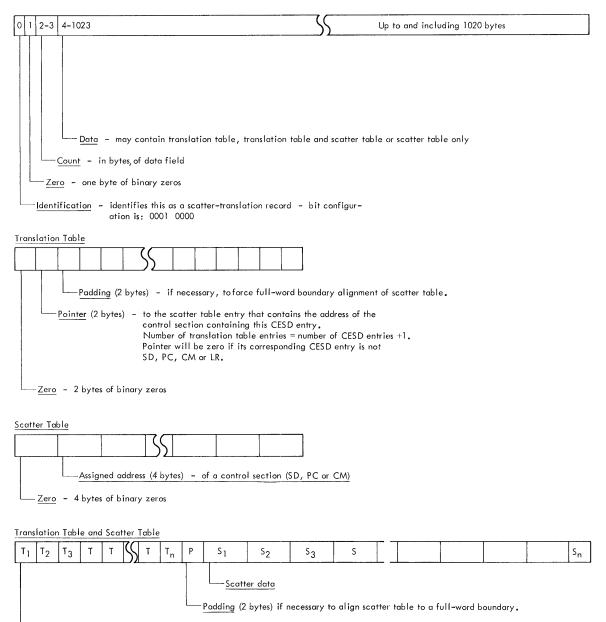

- <u>SYM records to be used by the test</u> <u>translator</u>. (If the TEST option is not specified on the EXEC statement, SYM records in input are not included in the output load module). These records contain blocked SYM and ESD statements created during a previous execution of linkage editor. SYM records in load modules are passed through the linkage editor unmodified to the output device.

- <u>A composite ESD</u>. CESD records contain the ESD items for the module. There is a maximum of 15 ESD items per record on the output device. The first eight bytes of the CESD record contain control information pertaining to the ESD items in the record. This information consists of the ESD ID of the first ESD item and the number of bytes of ESD items in the record.

- <u>A control record, or a composite</u> <u>control/RLD record, preceding each text</u> <u>record</u>. The RLD portion, if present, contains the RLD items used to relocate

the previous text.<sup>1</sup> The control portion may contain:

- An end of segment (EOS) indication, if the following text record is the last text record of an overlay segment.<sup>2</sup>

- 2. An end of module (EOM) indication, if the following text record is the last text record of the module.<sup>2</sup>

- The number of bytes of RLD information that follow, if it is a composite control/RLD record.

- 4. The number of bytes of control information.

<sup>1</sup>If there is a large number of RLD items for the previous text, there may be several RLD records preceding the next text record. The last of these is a control/RLD record.

<sup>2</sup>If there are no RLD items for the last text record, the control record that precedes the text contains the EOS or EOM indication. If there are RLD items, the EOS or EOM follows the text record. (See Figure 3.)

Any overlay statements in the load module are ignored.

Figure 3. Linkage Editor Processing - Using Overlay and Test Options

The control portion also contains the IDs of the control sections in the following text record, the number of bytes of text for each ID, and a channel command word (CCW). The channel command word contains the address assigned by the linkage editor to the first byte of that record, plus the total length of the record. This information is used by program fetch to read the following text.

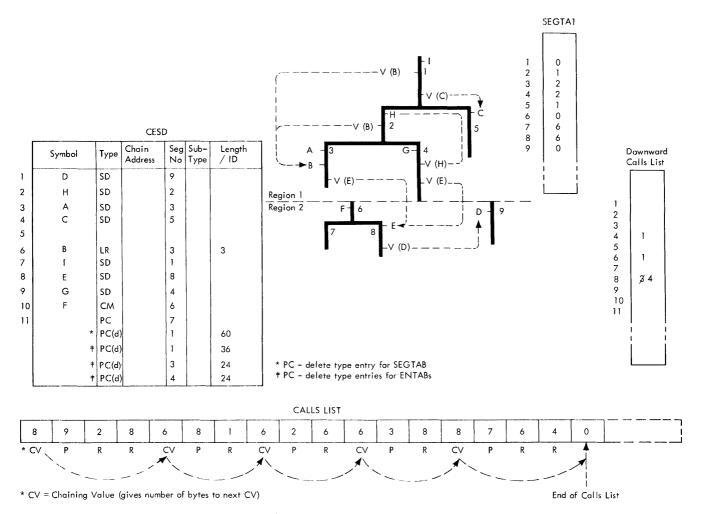

for each control section. Text Text records contain the code and data for the module. In overlay, the linkage editor produces two special types of text records, the segment table (SEG-TAB) and entry table (ENTAB). The SEGTAB, located in the root segment, is used by the overlay supervisor to keep track of the relationship of segments during execution. The ENTAB is a separate control section that may be created by the linkage editor in each overlay segment. An ENTAB is used by the overlay supervisor to determine the segment to be loaded when a segment not in the path is referred to.

• <u>A note list</u>. The note list gives the location of each overlay segment in the output module library.

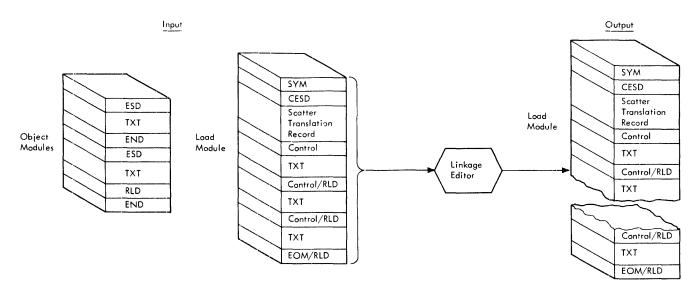

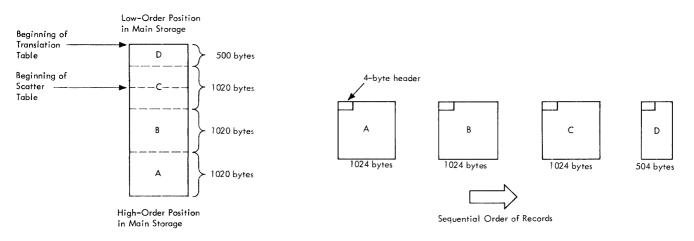

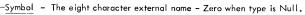

Figure 4 shows the module structure when the scatter loading and test options are requested. With these options, the output load module contains:

- SYM records.

- A composite ESD.

- A scatter/translation record used by program fetch to compute the relocated

addresses required for scatter loading the module into the main storage. The record contains a <u>scatter table</u> and a <u>translation table</u>. The scatter table is a list of control section addresses; the translation table correlates the CESD entry for each control section with the address indicated in the scatter table. (When a load module in scatter format is processed again by the linkage editor, this information is ignored.)

- Text for each control section, preceded by a control/RLD record describing it. (Any RLDs pertaining to a text record are contained in the control/RLD record that follows it.)

- An EOM indication that marks the end of the module.

The Appendix (Section 3) contains the format of each record type.

#### MODULE ATTRIBUTES

When the linkage editor generates a load module in a library (partitioned data set) it places an entry for the module in the PDS directory. This entry contains "attributes" describing the structure, content, and logical format of the load module. The control program uses these attributes to determine how a module is to be loaded, what it contains, if it is executable, whether it is executable more than once without reloading, and if it can be executed by concurrent tasks.

Some module attributes can be specified by the programmer; others are specified by the linkage editor as a result of information gathered during processing. In the following list, attributes marked with an asterisk cannot be specified by the programmer:

- <u>Reenterable</u>. A reenterable module can be executed by more than one task at a time and cannot be modified by itself or by any other module during execution; i.e., a task may begin executing a reenterable module before a previous task has finished executing it.

- <u>Serially Reusable</u>. A serially reusable module will be executed by only one task at a time, and it will either initialize itself and/or it will restore any instructions or any data in the module that it alters during its execution.

- Overlay format. A load module structured for overlay includes a segment table (SEGTAB) to enable the overlay supervisor to load the proper segments, and at least one ENTAB to assist in passing control from one segment to another. If a load module has the overlay format attribute, the reenterable, reusable, refreshable, hierarchy, and scatter attributes cannot be present.

- <u>Hierarchy format</u>. When a HIARCHY statement is detected, the "number" and "name" operand values are used in building the scatter table and translation table. The high-order byte of each CSECT address entry contains the hierarchy number that is included in the GETMAIN request for main storage for program loading.

- <u>Test</u>. If this module is an assembler language program and testing by the test translator is desired, this attribute can be specified. Test will cause SYM records to be written. If the TEST attribute is specified, the module cannot be reenterable or serially reusable.

- <u>Only loadable</u>. This attribute indicates that the control program may load this module only via the LOAD macro instruction.

- <u>Scatter format</u>. A load module in scatter format is suitable for block or scatter loading. The scattertranslation table and the relocation dictionary maintain logical linkage between scattered control sections when program fetch loads them into main storage.

- <u>\*Block format</u>. If neither the overlay nor scatter attributes are specified, it is implied that the module can only be block loaded. The control program will load the module only if enough contiguous main storage space is available for the entire module.

- <u>\*Executable</u>. This attribute indicates that linkage editor did not find any errors that would prevent successful execution. If this attribute is not present the control program will not load the module.

- <u>Module contains one text record and no</u> <u>relocation dictionary records</u>. This attribute indicates that the control program does not have to allocate main storage for relocation dictionary items when loading the module. It also indicates that the first text record is the last one; there is no control record following it. The entire module can be read by program fetch in a single read operation.

- \*Linkage editor assigned origin of first text record is zero. If this attribute is present, the first byte of instruction or data in the first text record is assigned to location zero.

- <u>\*Entry point assigned by linkage editor</u> <u>is zero</u>. Indicates that the entry point is at the first byte of the module.

- <u>\*No relocation dictionary items pres-</u> <u>ent</u>. Indicates to the control program that no allocation of main storage is

necessary to receive relocation dictionary items when program fetch loads them into main storage.

- <u>Not editable</u>. Indicates that the load module cannot be accepted by the linkage editor for subsequent processing. (For example, the programmer may drop the CESD from an output load module in order to conserve space on the library; such a load module cannot be reprocessed by linkage editor.)

- <u>Symbol statements present</u>. If a module produced by the assembler language translator is to be tested by the test translator, it may contain a testing symbol dictionary. In a load module, this dictionary contains the information from the symbol statement images that were input to linkage editor.

- <u>Refreshable</u>. A refreshable module cannot be modified by itself or by any other module during execution; i.e., a refreshable module can be replaced by a new copy during execution by a recovery management routine without changing either the sequence or the results of processing. (For details on recovery management, refer to the publication: IBM System/360 Operating System: Concepts and Facilities, Form C28-6535.)

# MAIN STORAGE HIERARCHY SUPPORT

If Main Storage Hierarchy Support for IBM 2361 Models 1 and 2 is included in the system, the linkage editor produces load modules which can be loaded into either processor storage or IBM 2361 Core Storage by the control program. If the HIAR parameter is specified in the PARM field of the EXEC statement, the linkage editor is initialized to accept the HIARCHY control statement. This statement specifies the storage hierarchy (0 for processor storage and 1 for IBM 2361 Core Storage) into which the CSECTs identified in the statement are to be loaded.

# MAJOR DIVISIONS OF LINKAGE EDITOR

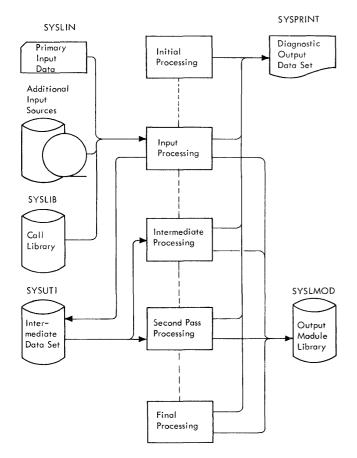

Linkage editor processing consists of five sequential operations:

- 1. Initial processing.

- 2. Input processing.

- 3. Intermediate processing.

- 4. Second pass processing.

- 5. Final processing.

#### INITIAL PROCESSING

Initial processing begins when the control program passes control to the linkage editor. During this operation, the linkage editor prepares for all subsequent operations. The initial processor:

- Uses data management facilities to open data sets to be used during linkage editor processing.

- Interprets the options and attributes specified by the programmer and saves them in an <u>all purpose table</u> (APT).

- Uses task management facilities to obtain main storage space for internal tables, work areas, and input/output buffer areas used in linkage editor processing.

After initial processing, control is passed to the input processor.

#### INPUT PROCESSING (FIRST PASS)

All input to the linkage editor is processed during the first pass. Input records are read, checked for validity, identified, and processed as required. The text and RLD items that are to be part of the output load module are written on the <u>intermediate data set</u> (SYSUT1). Linkage editor control statements are interpreted and processed and the CESD is built in main storage. SYM records in the input are gathered and written out directly on the output device as part of the output load module. After all input has been received and processed, control is passed to intermediate processing.

#### INTERMEDIATE PROCESSING

Intermediate processing consists basically of two operations: address assignment and intermediate output processing. Relative machine addresses are assigned to all external symbols that are to be contained in the output load module, to the module entry point, and also to any alternative entry points defined by the user with ALIAS statements. The intermediate output processor places the CESD and, if required, the SEGTAB or scatter translation table in the output module library.

#### SECOND PASS PROCESSING

During second pass processing, the text and RLD items are read from the intermediate data set, address constants in the text are relocated, and the records that make up the output module are written on the <u>output</u> module library (SYSLMOD).

#### FINAL PROCESSING

Final processing completes the library directory entry for the output load module and places it on the output module library. If the module is structured for overlay, the final processor writes out on SYSLMOD a <u>note list</u> that indicates the location of each segment in the output module library. If any coded diagnostic messages were written out on SYSPRINT during linkage editor processing, a directory explaining these coded messages is written. If specified, a module map or cross-reference table is produced. If a multiple execution of the linkage editor is specified, control returns to initial processing; otherwise, control is returned to the caller.

#### INPUT/OUTPUT FLOW

Four data sets must be specified for linkage editor processing; their ddnames and functions are:

- <u>SYSLIN</u>. This is the "primary input data set," containing object modules and control statements. All input from SYSLIN must be in 80-column card image format. The SYSLIN source may be a card reader, magnetic tape, a directaccess device, or a concatenation of data sets from different types of input devices.<sup>1</sup>

- <u>SYSPRINT</u>. This is the "diagnostic output data set." Diagnostic messages, the module map, and the cross-reference table are written on SYSPRINT. (In the Sequential Scheduling System, the SYS-PRINT device is normally a printer or magnetic tape.)

- <u>SYSUT1</u>. This is the "intermediate data set." Linkage editor uses this data set for temporary storage of text and RLD items being processed. SYSUT1 must be on a direct-access volume.

- <u>SYSLMOD</u>. This is the "output module data set." It is a partitioned data set on a direct-access volume. SYSLMOD contains load modules; their attributes are described in the user's portion of the directory entry for the member.

An additional data set, SYSLIB, is used by linkage editor if there are any automatic library calls to be processed. SYSLIB

<sup>&</sup>lt;sup>1</sup>A concatenation of data sets cannot contain both object and load modules.

can be defined only as a partitioned data set. The members of SYSLIB can be either load modules or object modules (but object and load modules cannot be contained in the same PDS). When SYSLIB is opened, the linkage editor determines whether the PDS contains object or load modules by checking the format in the data control block (DCB). If the PDS contains object modules, the record format (RECFM) field of the DCB indicates "fixed (F) format"; if it contains load modules, the DCB indicates "unknown (U) format". (Load module records are of variable length.) If SYSLIB contains object modules, the linkage editor ignores the user's portions of the PDS directory entries for the object modules.

Other data sets may be read by linkage editor when it processes INCLUDE or LIBRARY statements specifying ddnames. Data sets read into main storage with INCLUDE statements may be either sequential or partitioned. SYSLIB and data sets specified in LIBRARY statements for use by automatic library call must be partitioned.

The attributes for the "execute linkage editor" job step are the attributes specified on the EXEC statement. These attributes may be modified if a load module having different attributes is processed.

Figure 5 shows the input/output flow. During the initial processing, SYSLIN, SYSPRINT, SYSUT1, and SYSLMOD are opened. During input processing, the primary input is read from SYSLIN. If an INCLUDE statement is read in the primary input, the data set whose ddname is specified on the statement is opened, and is processed.

At the end of all SYSLIN input, SYSLIB and any other data sets whose ddnames are specified on LIBRARY statements are processed through automatic library calls.

If the TEST option has been selected, SYM records are written during input processing; text and RLD items are written sequentially on SYSUT1. The location of each text record on SYSUT1 is entered in a <u>text note list</u>. The location of each RLD record on SYSUT1 is entered in an <u>RLD note</u> <u>list</u>. If either note list overflows, it is written out on SYSUT1.

Figure 5. Input/Output Flow

In intermediate processing, the CESD is written on SYSLMOD (unless the not editable attribute is indicated). If a scatter table, translation table, or SEGTAB is required, it is also written on SYSLMOD. The note lists for the text and RLD items on SYSUT1 are read into main storage.

During second pass processing, text and RLD records are read into main storage from SYSUT1 in the order of assigned addresses within each segment (using the note lists to find the records) and are written out on SYSLMOD.

In final processing, the member name and any alias names are entered into the PDS directory entry of the output load module, via the STOW macro instruction. If any coded diagnostic messages were written on SYSPRINT during linkage editor processing, a diagnostic message directory containing error message text is written out on SYS-PRINT. If a module map or cross-reference table was requested, SYSLMOD is closed, and then reopened as an input source. The CESD

is read into main storage from SYSLMOD to be used in producing the module map. If a cross-reference table was requested, the RLD items are also read from SYSLMOD; at the end of final processing, SYSLMOD is closed. All other data sets are then closed and control is returned to the calling program, unless the SYSLIN input during input processing was terminated by a NAME statement. If a NAME statement terminated the primary input, control is returned to initial processing and SYSLMOD is opened for output. When a NAME statement is used to produce multiple load modules in a single execution of linkage editor, SYSLIN, SYSPRINT, and SYSUT1 remain open for the entire execution. (A pointer in the DCB for SYSUT1 is repositioned to the beginning of extent of SYSUT1 after each load module is produced.) If neither a module map nor a cross-reference table is requested, SYSLMOD remains open for output.

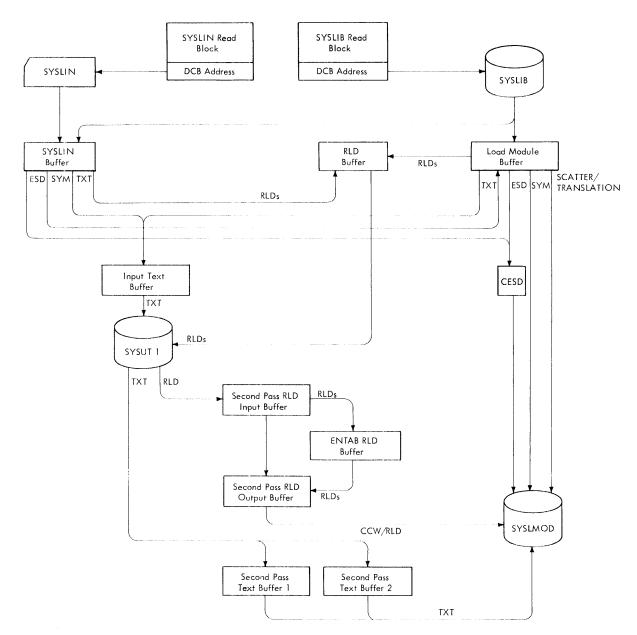

# INTERNAL DATA FLOW

A generalized representation of internal data flow during linkage editor processing is given in Figure 6. A pointer in the SYSLIN or SYSLIB read block indicates the input source from which data is to be read. The input data is then read in and processed in the following manner:

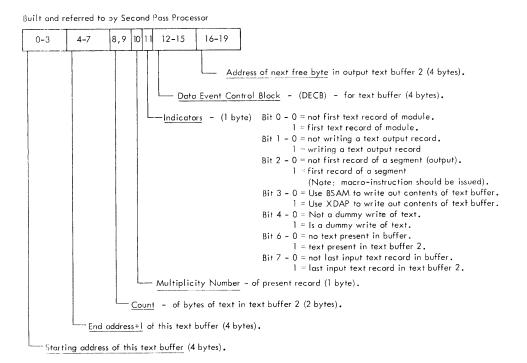

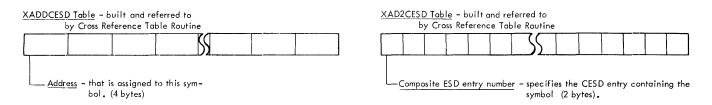

Input records from SYSLIN are read into the SYSLIN buffer. (SYSLIN contains only object modules.) Object modules from SYS-LIB are read into the SYSLIN buffer, whereas load modules from SYSLIB are read into the load module buffer. During input processing, SYM information is gathered in the load module buffer, text is gathered in the input text buffer, RLD records are processed in the input RLD buffer, and ESD records are combined into the composite ESD. Text and RLDs are written out on SYSUT1, while SYM records are written directly on SYSLMOD. CESD, SEGTAB, and scatter/translation records are written out on SYSLMOD during intermediate processing. During second pass processing, any RLD items that were placed on SYSUT1 are read back into the second pass RLD buffer; any text that was stored on SYSUT1 is read back into the second pass text buffer. (Two second pass text buffers are used for input/output overlap.) For overlay modules, ENTAB RLD items are produced in (The ENTAB itself is the ENTAB RID buffer. built in the second pass text buffer.) After address constants in the text have relocated, text, RLD, and ENTAB been records are written out on SYSLMOD.

•Figure 6. Internal Data Flow

#### SECTION 2: DISCUSSION OF MAJOR DIVISIONS

The following text and the associated flowcharts at the end of this section describe the major divisions of the 15K and 18K versions of linkage editor E. Each major division is further subdivided and described to explain the general organization and operation of linkage editor.

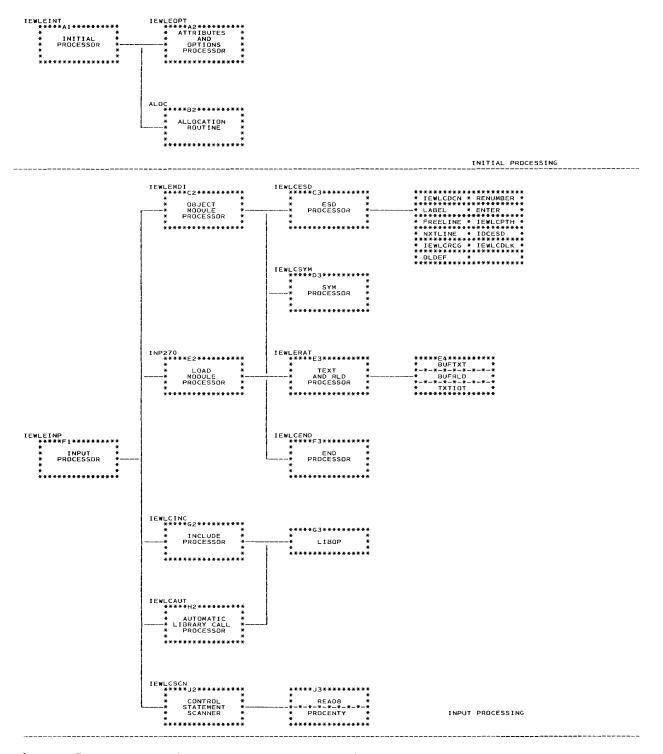

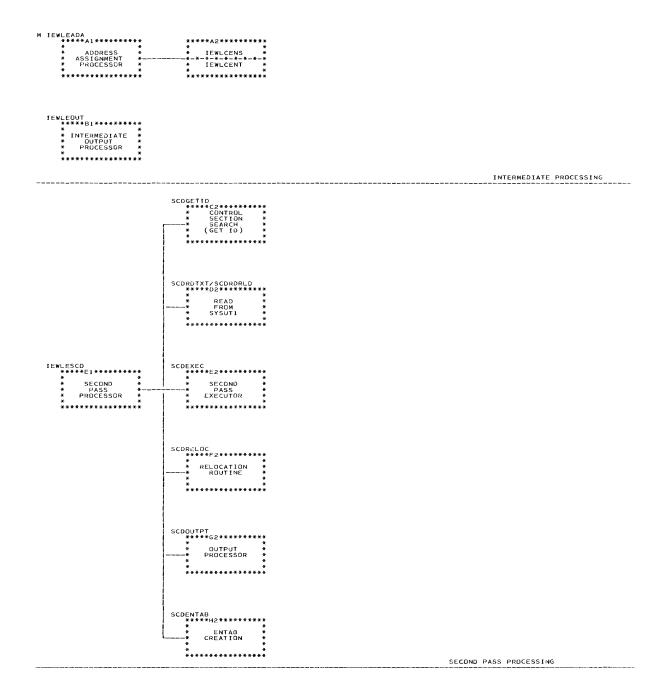

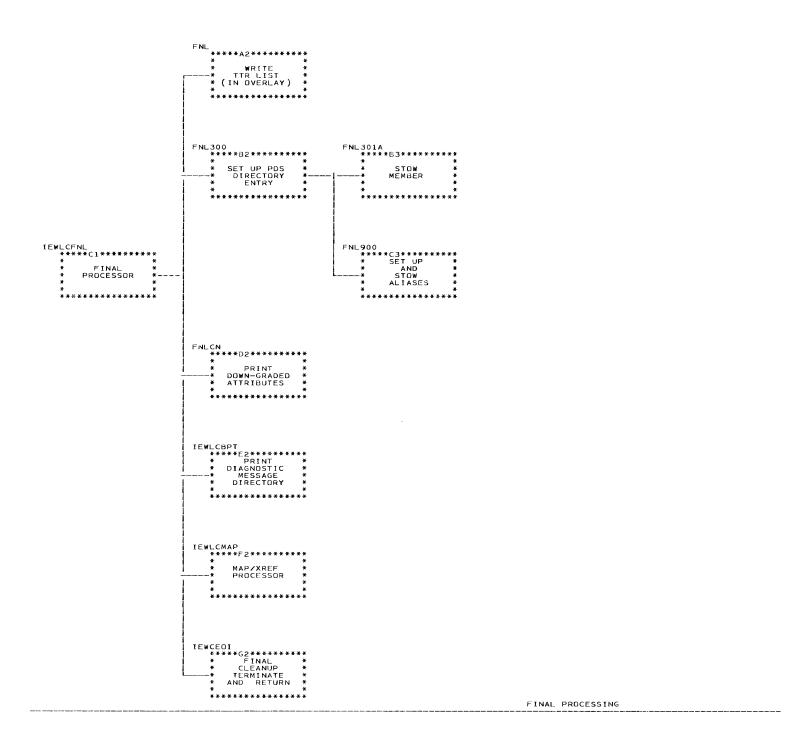

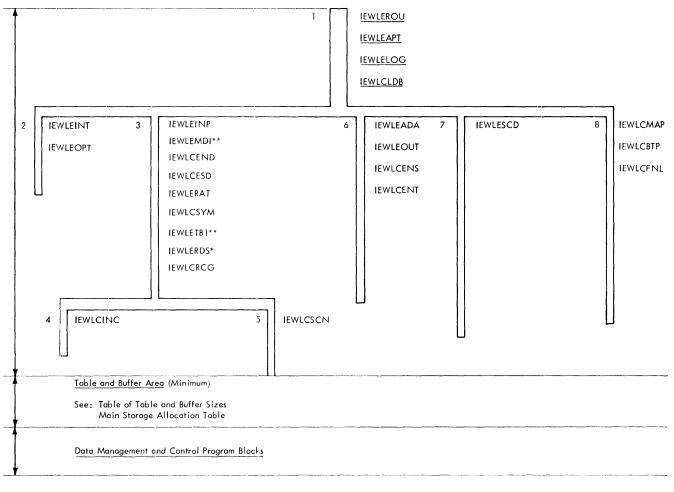

The major divisions of linkage editor E are shown in chart AA.

- Initial processor.

- Input processor.

- Address assignment processor.

- Intermediate output processor.

- Second pass processor.

- Final processor.

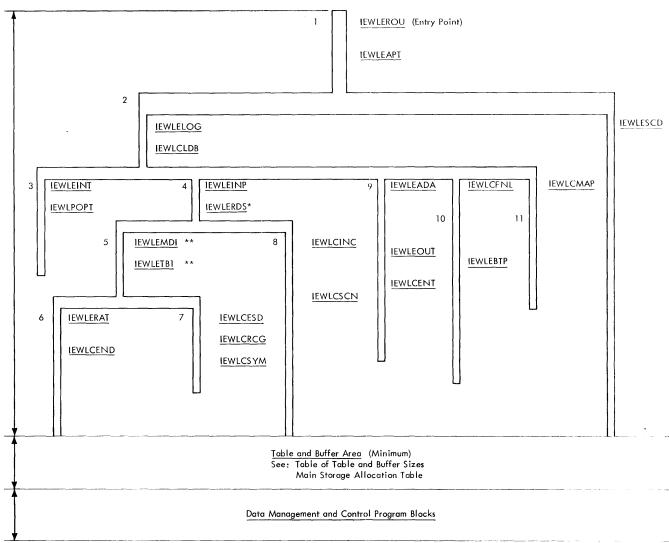

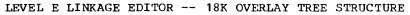

The overall organization of linkage editor E is shown in Figure 7.

#### INITIAL PROCESSOR

The initial processor builds an all purpose table (APT), which contains descriptions of other tables used by the linkage editor, and contains decision indicators that control linkage editor operation. The APT remains in main storage throughout the linkage editing process and is the major communication area among internal functions.

When the linkage editor receives control from the job scheduler, or from another program via a CALL (after execution of LOAD, LINK, XCTL, or ATTACH macro instruction), control information may be passed to it.<sup>1</sup> This information includes the attributes and options that control linkage editor processing. When control is passed to the linkage editor from the job schedul-

<sup>1</sup>The method of passing information to the linkage editor is described in the System Reference Library publication <u>IBM\_System/</u> <u>360\_Operating\_System: Linkage\_Editor and</u> Loader. er, the passed control information is the information contained in the operand field of the EXEC statement. The initial processor interprets the control information, checks it for validity, and saves it for later use in linkage editor processing.

A program that passes control to the linkage editor may provide a substitute list of ddnames to be used by the linkage editor in place of the standard names, and a name that is to be assigned to the output load module in the PDS directory.

The 15K and 18K level E initial processor (IEWLEINT) (Chart BA) operates in the following manner:

- After the standard ddnames (or passed ddnames) have been entered into the data control blocks of the data sets used by the linkage editor, the initial processor opens all data sets except SYSLIB and SYSLMOD using data management facilities. (The SYSLIB DCB is used for automatic library calls or INCLUDE statements. It is opened during input processing only if there are any automatic calls or INCLUDE statements specifying it.)

- The initial processor sets an "unlike attributes" indicator in the SYSLIN DCB. This indicates to the open routine that SYSLIN may be a concatenation of data sets stored on different devices.

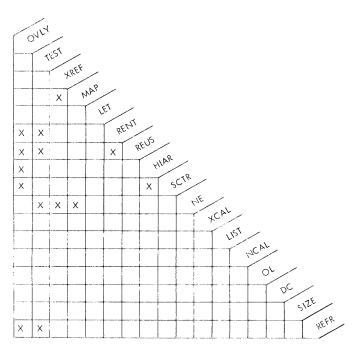

- The attribute and option routine scans and analyzes the control information that was previously passed in a list to linkage editor. The processing options requested by the user and the attributes to be assigned to the output load module are compared against an option table and noted in the all purpose table. When mutually exclusive attributes are specified for a load module, the linkage editor ignores the incompatible attribute (refer to Table 1).

Table 1. Combinations of Module Attributes and Program Options Note: An X indicates incompatible attributes: the attribute that appears lower on the list is ignored. For example, to check the compatibility of XREF and NE, follow the XREF column down and the NE row across until they intersect. Since an X appears where they intersect, they are incompatible attributes. NE is ignored.

Figure 7. Level E Linkage Editor Organization

Figure 7. Level E Linkage Editor Organization (Continued)

Figure 7. Level E Linkage Editor Organization (Continued)

• SYSLMOD is opened, and the allocation processor requests main storage space for internal tables, buffers, and work areas. The allocation processor issues a request for a minimum requirement of main storage space. The minimum value depends on whether or not the module being processed is structured for overlay; it includes an amount to be used by data management functions. If sufficient main storage space is available, the supervisor returns control to the allocation processor and the space exceeding the minimum requirement is divided among the tables and buffers. If sufficient main storage space is not available, the control program will not return control to linkage editor.

The following paragraphs describe the allocation process in the level E version of the linkage editor.

MAIN STORAGE ALLOCATION - 15K AND 18K LEVEL  $\ensuremath{\mathsf{E}}$

To obtain the required main storage space, the allocation processor (ALOC):

- 1. Determines the excess of main storage space allocated by the supervisor.

- 2. Divides the total excess by the total weight factor. A weight factor is a ratio based on the individual main storage requirements of linkage editor tables that are not fixed in size. (Fixed tables have weight factors of zero.) The total weight factor depends on whether or not the module is structured for overlay.

- 3. Multiplies the quotient obtained in step 2 (rounded to the nearest lower integer) by the weight factor for each table and adds the result to the minimum requirement for the table. This is done for all tables and buffers used by the current module.

- 4. Divides the total byte count for each table by the number of bytes per entry, and saves the result in the all purpose table.

- 5. Computes the addresses for the tables.

- 6. Releases excess main storage space, noting the last address used.

When the required main storage space has been allocated, tables are initialized, and control is passed to the input processor.

#### INPUT PROCESSOR

After initial processing, control is passed to the input processor. The input processor performs a control function; the operations performed depend on the nature of the input. The input type and input conditions are analyzed, and control is passed to the appropriate processing routine. At the end of input, control passes to the intermediate processor.

The 15K and 18K level E input processor (IEWLEINP) is shown in Chart CA; it operates in the following manner:

- Each input record is read, using one of two read blocks. The first read block contains the address of the SYSLIN module buffer, the address of the SYS-LIN DCB, and the block size and logical record length. The second read block contains the address of the buffer for library records (object module buffer or load module buffer), the address of the library DCB, and the block size and logical record length. A pointer is used to indicate which read block is to be used for the input record. Initially, the pointer is set to the SYSIIN read block. If input is to be read from a library, the include processor (Chart CO) or automatic library call processor (Chart CP) may move the pointer to the library read block at any end-of-data condition. The reading of input is therefore not restricted to a particular DCB and buffer.

- If SYSLIN is a concatenation of data sets, the current READ is reissued when a data set boundary is crossed.

- Control is given to the control statement scanner (Charts CL and CM) for all object module records whose first column character is a blank, provided that the record is not encountered "in module." (Control statements encountered within a module cause an error indication.)

- Control is given to either the object module processor (Chart CE) or load module processor (Chart CC), depending on the input module type. (All input via include or automatic library call is identified by record format. F format indicates object modules; U format indicates load modules. Only object modules are read from SYSLIN.)

- At any end-of-input (from SYSLIN or SYSLIB), the input processor determines if control should be given to the include processor or to the automatic library call processor. The include processor is given control if more modules must be included before resuming normal processing. The automatic library call processor receives control if the NCAL option (no automatic library calls) was not selected and an end-of-input on SYSLIN has occurred. If the NCAL option was selected, control is passed to the address assignment processor.

- If a NAME statement, which may indicate a multiple execution of linkage editor, was detected by the control statement scanner, processing proceeds as if an end-of-input had occurred on SYSLIN (the automatic library call processor receives control). However, no end-ofinput indication is made so that control will be returned to the initial processor at the end of final processing.

- If an end-of-input occurs on SYSLIN, but no valid input was received, control is passed to the final processor (Chart GA) to terminate linkage editor processing.

#### OBJECT MODULE PROCESSOR

The level E object module processor is shown in Chart CB. Object module processing consists essentially of three operations:

- 1. Determination of record type.

- 2. Setup of general registers.

- 3. Special event processing.

The record type is determined by examining columns 2 through 4 of each logical input record. For each record type, control is passed to an associated processor, as follows:

| Record<br><u>Type</u> | Processor | Chart    |

|-----------------------|-----------|----------|

| SYM                   | IEWLCSYM  | CD       |

| ESD                   | IEWLCESD  | CE,CF,CG |

| TXT                   | IEWLERAT  | CH,CJ    |

| RLD                   | IEWLERAT  | CH,CI    |

| END                   | IEWLCEND  | CK       |

The general registers are loaded with input record information to be used by the selected processor, as described in Table 2.

| ●Table | 2. | General | Register | Information | - Object | Module | Processing |

|--------|----|---------|----------|-------------|----------|--------|------------|

|--------|----|---------|----------|-------------|----------|--------|------------|

| Input Record Type<br>(See Appendix A for |                  | General 1                                                          | Register         |                                               |

|------------------------------------------|------------------|--------------------------------------------------------------------|------------------|-----------------------------------------------|

| Record Formats)                          | 3                | 4                                                                  | 5                | 6                                             |

| SYM                                      |                  | SYM Statement<br>byte count                                        |                  | Address of SYM<br>statement in<br>buffer      |

| ESD                                      |                  | Number of bytes<br>of ESD informa-<br>tion                         |                  | Address of first<br>byte of ESD in<br>buffer  |

| TXT                                      | of first byte of | Number of bytes<br>of text informa-<br>tion                        |                  | Address of first<br>byte of text in<br>buffer |

| RLD                                      |                  | Number of bytes<br>of RLD informa-<br>tion                         |                  | Address of first<br>byte of RLD in<br>buffer  |

| END                                      | of entry point   | Length of CSECT<br>for which no<br>length was given<br>in ESD item | containing entry |                                               |

Following is a description of special event processing:

- When an END statement is detected, the RLD and TXT processor is entered so that any data still contained in the input RLD buffer or the input text buffer can be written out on SYSUT1.

- If the TEST option is selected, the SYM records from the object module are gathered by the SYM processor in the load module buffer. When the first TXT statement in a module is encountered (or if no text statement has been encountered when the END statement is detected), the SYM processor is entered so that the contents of the load module buffer can be written out on SYSLMOD (see Chart CD).

- When control is returned from the ESD processor, indicators in the all purpose table are examined to determine if:

- 1. A control section (SD, PC, or common) was indicated on the ESD statement.

- 2. The TEST option was specified.

If both conditions are met, the SYM processor is entered to block the ESD record with any other ESD records in the input text buffer.

- If a control statement continuation is expected and an object module record is read, an error condition occurs, and a coded diagnostic message is produced by the error logging routine. Normal object module processing is then performed on the record.

- If, during object module processing, a statement is encountered which is not one of the five acceptable types (SYM, ESD, TXT, RLD, or END), an error condition occurs and a diagnostic message is produced by the error logging routine. The input record is then ignored.

#### LOAD MODULE PROCESSOR

The level E load module processor is shown in Chart CC. Load modules included in the input to linkage editor by the include processor or the automatic library call processor are processed in the following manner:

• The input record type is determined by an identification field (byte 1 of the

record), and control is passed to an associated processor, as shown in Table 3.

- The parameter registers are loaded with input record information to be used by the selected processor, as described in Table 4.

- If the record is not identified as a TXT, CESD, Scatter/Translation, SYM, or CCW/RLD record, an error condition occurs, and a diagnostic message is printed out. The input record is otherwise ignored.

- If the TEST option was not specified on the EXEC statement, all SYM records are ignored.

- If an end-of-module indication is found in a CCW or RLD record, the END processor performs cleanup functions and control returns to the input processor.

- When a CCW record is detected, the following TXT record is immediately read into the input text buffer before the TXT and RLD processor is entered.

- If the test option was specified on the EXEC statement and a SYM record is received, control is passed to the SYM processor to write out the record as test translation data from the load module buffer (see Chart CD).

| PI0Cessols                               |                          |                     |              |  |  |

|------------------------------------------|--------------------------|---------------------|--------------|--|--|

| Record Type                              | Identifier               | Processor           | Chart        |  |  |

| TXT                                      | *<br> hex "20"           | IEWLERAT<br>IEWCESD | CH,CJ        |  |  |

| CESD<br>Scatter/                         |                          | TEWCESD             | CE,CF,CG<br> |  |  |

| Translation                              | hex <b>'</b> 10 <b>'</b> | (Ignored)           |              |  |  |

| SYM                                      | hex <b>'</b> 40 <b>'</b> | IEWLCSYM            | CD           |  |  |

| CCW                                      | hex '01'                 | IEWLERAT            | CH,CI        |  |  |

| CCW/RLD                                  | hex '03'                 | IEWLERAT            | CH,CI        |  |  |

| RLD                                      | hex '02'                 | IEWLERAT            | CH,CI        |  |  |

| If end of mo                             | odule indica             | ation is or         | n:           |  |  |

| CCW                                      | hex 'OD'                 | IEWLCEND            | СК           |  |  |

| CCW/RLD                                  | hex 'OF'                 | IEWLCEND            | CK           |  |  |

| RLD                                      | hex 'OE'                 | IEWLCEND            | CK           |  |  |

| *Identified by preceding control record. |                          |                     |              |  |  |

• Table 3. Record Types and Associated Processors

The following paragraphs describe the functions, during object and load module processing, of the ESD processor, the TXT and RLD processor, and the END processor.

Table 4. General Register Information - Load Module Processing

|                              |   | General F                                         | Register                                   |                                            |

|------------------------------|---|---------------------------------------------------|--------------------------------------------|--------------------------------------------|

| Load module  <br>Record Type | 3 | 4                                                 | 5                                          | б                                          |

| SYM                          |   | Zero                                              |                                            |                                            |

| CESD                         |   | Byte count of ESD<br>items in record              | ESDID of first<br>CESD item in<br>record   | Address of first<br>CESD item in<br>buffer |

| CCW                          |   | Level E-Byte count<br>text in following<br>record | ESDID of CSECT<br>to which text<br>belongs |                                            |

| RLD                          |   | Byte count of RLD<br>items in record              |                                            | Address of first<br>RLD item in<br>buffer  |

#### ESD PROCESSOR

When the object or load module processor detects an ESD record, it gives control to the ESD processor (Charts CE, CF, and CG).

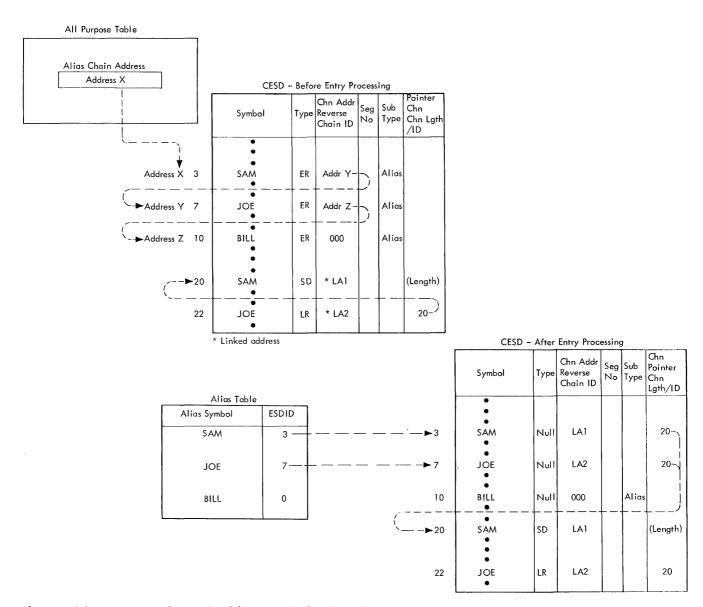

The main function of the ESD processor is symbol resolution. It combines the individual ESDs in the input to linkage editor into a composite ESD, which contains all symbols in the input which were not changed, deleted, or replaced. The ESD processor refers to a chained REPLACE/ CHANGE list (produced by the control card scanner) to determine which ESD items are to be changed, deleted, or replaced. The ESD processor also produces a renumbering table (RNT), which is used by the TXT, RLD, and END processors to translate the ESD ID of the input ESD items to CESD IDS.

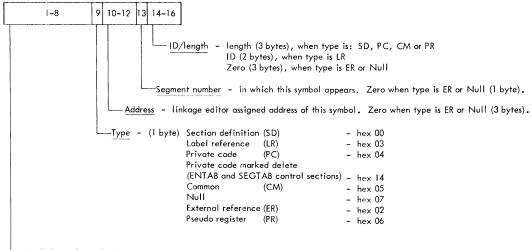

#### ESD Record Types

Every object module in the input to linkage editor must contain at least one ESD item. An ESD item is created by a language translator whenever it finds a symbol that is defined for external use. In the assembler language, for example, ESD items are created whenever an ENTRY, EXTRN, COM, START, or CSECT statement, or a V-type address constant is found. An ESD item is created to define the beginning of each control section, and to define a common area. Each ESD item has a type assigned to it that indicates its function. The ESD types are:

- <u>Section Definition (SD</u>). Defines the beginning of a named control section.

- <u>Private Code (PC)</u>. Defines the beginning of an unnamed control section.

- <u>Label Definition (LD)</u>. Defines a label (symbol) whose location is defined relative to the location of the control section in which it is contained. An LD-type ESD item contains the ESD ID of the control section that contains the label.

- <u>Common (CM)</u>. Defines a common area for which a main storage address is assigned during linkage editor processing. The area may be named or unnamed; an unnamed area is referred to as a "blank common" area.

- <u>Pseudo Register (PR)</u>. Defines an area external to the output module, but referred to by it, for which main storage space is allocated at execution time. The linkage editor treats PR symbols as a block that is external to the program. The value assigned to each symbol is a displacement within this block.

- External Reference (ER). Refers to a symbol that is referred to but not defined within an input module.

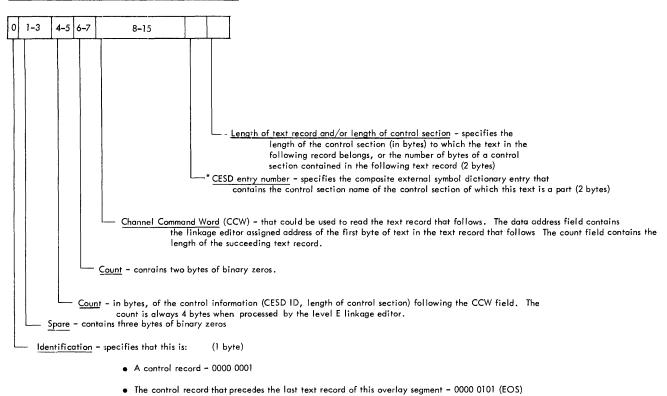

## CESD Record Types and Subtypes

A load module in the input to linkage editor contains at least one CESD record (240 bytes, maximum). The CESD record types are the same as for ESD records, with the following additions:

- <u>Null type</u>. This indicates that the item is to be ignored in any reprocessing of the module by linkage editor.

- <u>Label Reference (LR)</u>. This defines a label (symbol) within a control sec-

tion. An LR type CESD entry is numbered; it contains the ESD ID of the control section entry in the ID/length field. An LR may be referenced directly by an RLD item in the same module, whereas an LD may not. All LD items are changed to LR items during linkage editor processing (LDs are contained only in object modules, never in load modules).

• <u>Private Code (PC) Marked Delete</u>. This is a CESD item created only for ENTABS and SEGTABS. PC-delete entries are placed in the renumbering table, indicating that associated TXT and RLD information is to be deleted.

CESD items may also contain a "subtype." The subtypes are listed in the internal CESD format in Section 3.

#### ESD Processing

Upon receiving control from the input processor, the ESD processor saves the ESD ID of the ESD record, the number of bytes of ESD information, and the type field of the first ESD item. The current segment number is placed in the ESD, unless it is a PR type (PRs have an alignment value in the segment number field). If the automatic library call indicator is on, the segment number is set to 1 so that called modules will be placed in the root segment. The ESD item is then processed according to its type, in the following manner:

- If the ESD item is an ER, bytes 10, 11, and 12 are set to zero in the input buffer (either the object module buffer, the SYSLIN buffer, or the load module buffer). Byte 10 must be cleared because the automatic library call processor uses it to indicate if automatic library calls have been processed. Bytes 11 and 12 must be cleared because any nonzero data (including blanks) will be entered in the <u>delink</u> <u>table</u> if delinking is required for the symbol. If the input item is an ER item from an object module, the CESD subtype field is also reset to zero to indicate that there are no modifiers in the subtype field.

- If a REPLACE/CHANGE function has been requested for the input module, the routine IEWLCRCG examines the REPLACE/CHANGE chain that was built in the CESD by the control statement scanner and makes the appropriate modifications. For example, if the scanner received the statement CHANGE A (B), the CESD contains a line for A, marked as a change statement item in the subtype field; the next line contains the symbol B. The ESD processor

changes the input ESD item symbol from A to B.

- If the ESD item is a PC, the CESD is not searched because each PC entry is treated as a unique entry. The PC is placed in the next available CESD line and is processed in the same manner as an SD.

- If the ESD item is NULL, the renumbering routine is entered. (This routine is described in "Non-Resolution Processing".)

- If the ESD item is an LD, the ESD processor changes it to an LR. The item is then processed as an LR. (There are some minor differences in processing LDs that have been changed to IRs; refer to "LR (or LD) Items." For this reason, the ESD processor sets an internal indicator when it changes the type to LR.)

After determining the FSD type, the ESD processor scans the CESD for a matching symbol. If no match is found, nonresolution processing proceeds as shown on Chart CF. If the input ESD symbol matches a symbol in the CESD, resolution processing is performed as shown on Chart CG. Resolution processing results in only one CESD entry for each unique input FSD symbol; multiple occurrences of the same input ESD symbol are listed in the renumbering table (RNT) with pointers to the single CESD entry.

NON-RESOLUTION PROCESSING (CHART CF): If no matching symbol is found in the CFSD, the input ESD item is processed as described in the following paragraphs.

SD\_Items: If the input ESD item is an SD:

- The freeline routine selects an empty line in the CESD. The line following the current line is chosen unless a previous CESD line is marked null. (Null lines are used whenever possible to save space.)

- The ESD processor determines if automatic library calls are being processed. If automatic library calls are being processed, an indicator is set in the type field of the selected CESD line. (If a module map was requested, this indicator is checked during module map processing. If the indicator is set, the control section is marked with an asterisk in the module map or cross reference table to indicate that it was obtained from a library during automatic library call processing.)

Section 2: Discussion of Major Divisions 25

- A "write" indicator is set in the all-purpose table to note that SDs, PCs, or CMs were encountered in the input record. When control returns to the input processor, the write indicator is tested. If it is on and the TEST option was specified, routine IEWLCSYM will save ESD records containing SDs, PCs, or CMs, block them into 244-byte records (including four bytes of control information), and write them out on SYSLMOD.