Y28-6616-1

#

# **Program Logic**

# IBM System/360 Operating System

# Input/Output Supervisor

Program Number 3605-CI-505

This publication describes the operation of the I/O supervisor within the IBM System/360 Operating System control program. The I/O supervisor's components, the EXCP supervisor and the I/O interruption supervisor, are discussed in detail to show the internal structure and logic involved in the control of I/O devices and channels.

Program Logic Manuals are intended for use by IBM customer engineers involved in program maintenance and by system programmers involved in altering the program design. Program logic information is not necessary for program operation and use; therefore, distribution of this manual is limited to persons with program maintenance or modification responsibilities.

#### PREFACE

This publication discusses the operation of the I/O supervisor. It is directed primarily to IBM customer engineers and to IBM system programmers.

The publication is divided into an | introduction and five parts to provide both general and detailed presentations of the following areas:

- EXCP supervisor.

- I/O interruption supervisor.

- Error routines.

- SVC transient area routines.

- Control blocks, tables, and queues.

All options that may be added to the primary control program are included in the presentations. The control program options are explained in the publication <u>IBM</u> <u>System/360</u> Operating System: Storage Estimates, Form C28-6551.

#### RECOMMENDED PUBLICATIONS

Information required for an understanding of this manual is contained in the following publications:

IBM System/360: Principles of Operation, Form A22-6821

IBM System/360 Operating System: Introduction to Control Program Logic, Program Logic Manual, Form Y28-6605

In addition, the following publication may be found convenient for reference:

IBM System/360 Operating System: System Programmer's Guide, Form C28-6550

#### Second Edition (April 1967)

This edition, Form Y28-6616-1, is a reprint of Form Y28-6616-0 incorporating TNLs Y28-2155, dated 6/1/66, Y28-2169, dated 8/31/66, dated 2/27/67. Note also that the prefix is changed from Z28- to Y28.

Specifications contained herein are subject to change from time to time. Any such change will be reported in subsequent revisions or Technical Newsletters.

This publication was prepared for production using an IBM computer to update the text and to control the page and line format. Page impressions for photo-offset printing were obtained from an IBM 1403 Printer using a special print chain.

Copies of this and other IBM publications can be obtained through IBM Branch Offices.

A form for readers' comments appears at the back of this publication. It may be mailed directly to IBM. Address any additional comments concerning this publication to the IBM Corporation, Programming Systems Publications, Department D58, PO Box 390, Poughkeepsie, N. Y. 12602

## CONTENTS

|                      | INTRODUCTION                                      | •  | 7          |

|----------------------|---------------------------------------------------|----|------------|

|                      | The Input/Output Supervisor                       |    | 8          |

| ,<br>j               | EXCP Supervisor                                   | •  | 10         |

|                      | I/O Interruption Supervisor                       | •  | 11         |

| 1.<br>1.<br>1.<br>1. |                                                   |    |            |

|                      | The Error Routines                                |    | 11         |

|                      |                                                   |    |            |

|                      | The Purge and Restore Routines                    | •  | 1,2        |

|                      |                                                   |    | 4.0        |

|                      | The Control Blocks, Tables, and Queues            | ٠  | 12         |

|                      | Control Blocks.                                   | •  | 12         |

|                      | Input/Output Block                                |    | 13         |

|                      | Data Control Block                                |    |            |

|                      | Data Extent Block                                 |    | 13         |

|                      |                                                   |    |            |

|                      |                                                   | •  | 13         |

|                      | Tables                                            | •  | 14         |

|                      |                                                   | •  | A 1.       |

|                      | Device Table                                      | •  | $14 \\ 15$ |

|                      | Statistics Table                                  |    |            |

|                      | Attention Table.                                  | •  | 15         |

|                      | Attention Table                                   |    | 15         |

|                      | Logical Channel Word Table                        |    | 16         |

|                      | Queues.                                           |    |            |

|                      | Logical Channel Queues                            |    |            |

|                      | Seek Queues                                       |    | 17         |

|                      | Seek Queues                                       |    | 17         |

|                      |                                                   | -  |            |

|                      | PART I: EXECUTE CHANNEL PROGRAM                   |    |            |

|                      | SUPERVISOR                                        |    | 18         |

|                      |                                                   |    |            |

|                      | General Operating Procedure                       | •  | 18         |

|                      |                                                   |    |            |

|                      | Operation of the Subroutines and                  |    |            |

|                      | Modules                                           | •  | 19         |

|                      |                                                   |    | 19         |

|                      | GET Request Element Subroutine                    | •  | 20         |

|                      | Error EXCP Routine                                | ٠  | 20         |

|                      | Test Channel Modules                              | ٠  | 21         |

|                      | Selector Channel Test Channel                     |    | ~ 1        |

|                      | Module.                                           | •  | 21         |

|                      | Multiplexor Channel Test Channel                  |    | 24         |

|                      | Module                                            | •  | 21         |

|                      | Normal Engueue Modules                            |    | 21<br>22   |

|                      | Normal Enqueue Module                             | •  | 22         |

|                      | Priority Enqueue Module                           | ٠  | 22         |

|                      | Normal Dequeue Module Ordered Seek Enqueue Module | •  | 22         |

|                      | Ordered Seek Enqueue Module                       | •  | 22         |

|                      |                                                   | •  | 23         |

|                      | Select Subroutine                                 | •  | 24         |

|                      | Unit Record and                                   | ۹. | 24         |

|                      | Telecommunications Start I/O                      |    |            |

|                      | Module.                                           |    | 24         |

|                      | Tape Start I/O Module                             | •  | 24         |

|                      | Direct-Access Start I/O                           |    | a. 1       |

|                      | Module                                            |    | 25         |

|                      | End-of-Extent Appendage.                          | -  | 26         |

|                      | Start I/O Subroutine                              |    | 26         |

|                      | Start I/O Appendage                               |    | 26         |

|                      | Post-Start I/O Subroutine                         |    | 26         |

|                      |                                                   |    |            |

| PART II: I/O INTERRUPTION SUPERVISOR.                                                                                      | •     | 28                               |

|----------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------|

| General Operating Procedure                                                                                                | •     | 28                               |

| Operation of the Subroutines and                                                                                           | '     |                                  |

| Modules                                                                                                                    |       | 29                               |

| Modules                                                                                                                    |       | 29                               |

|                                                                                                                            | •     | 29                               |

|                                                                                                                            | •     | 29                               |

| Channel Data Check, Channel                                                                                                |       |                                  |

| Control Check, Interface                                                                                                   |       |                                  |

| Control Check Bits                                                                                                         | •     | 29                               |

| Control Unit End Bit                                                                                                       | •     | 30                               |

| PCI Bit and PCI Appendage                                                                                                  |       | 30                               |

| Channel End Bit and Channel End                                                                                            |       |                                  |

| Appendage                                                                                                                  |       | 30                               |

| Device End Bit                                                                                                             | •     | 30                               |

|                                                                                                                            | •     | _                                |

| Attention Bit.                                                                                                             | •     | 21                               |

| Unit Check Bit and Abnormal End                                                                                            |       | ~ 4                              |

| Appendage                                                                                                                  | •     | 31                               |

| Unit Exception and Incorrect                                                                                               |       |                                  |

| Length Bits                                                                                                                | •     | 31                               |

| Program Check, Protection Check,                                                                                           |       |                                  |

| and Chaining Check Bits                                                                                                    |       | 31                               |

| Status Modifier and Busy Bits.                                                                                             | •     | 31                               |

| Trapcode Modules                                                                                                           |       |                                  |

|                                                                                                                            | •     | 21                               |

| Unit Record and                                                                                                            |       |                                  |

| Telecommunications Trapcode                                                                                                |       |                                  |

| Modules                                                                                                                    | •     | 31                               |

| Tape Trapcode Module                                                                                                       | •     | 31                               |

| Direct-Access Trapcode Module                                                                                              |       | 32                               |

| Channel Restart Subroutine                                                                                                 |       |                                  |

| Channel Search Modules                                                                                                     |       |                                  |

| Multiplexor Channel with Burst                                                                                             | •     | 52                               |

|                                                                                                                            |       | 32                               |

| Devices                                                                                                                    | •     | 32                               |

| Multiplexor Channel with No                                                                                                |       |                                  |

| Burst Devices                                                                                                              | •     | 33                               |

| Selector Channel Included in                                                                                               |       |                                  |

| Only One Logical Channel                                                                                                   | •     | 33                               |

| Selector Channel Included in                                                                                               |       |                                  |

| More than One Logical Channel .                                                                                            |       | 33                               |

| Sense Subroutine                                                                                                           |       | 34                               |

| Interfaces.                                                                                                                |       | 34                               |

| Attention Routine Interface                                                                                                |       | 34                               |

|                                                                                                                            |       |                                  |

| Error Routine Interface                                                                                                    |       | 35                               |

| SER Interface                                                                                                              | ٠     | 36                               |

| ABTERM Routine Interface                                                                                                   | •     |                                  |

| Post Routine Interface                                                                                                     | •     | 36                               |

|                                                                                                                            |       |                                  |

| PART III: IBM-SUPPLIED ERROR ROUTINES                                                                                      |       | 37                               |

|                                                                                                                            | •     | 0.                               |

| Device-Dependent Routines                                                                                                  |       | 37                               |

|                                                                                                                            | •     | 38                               |

| General Operating Procedure                                                                                                | •     |                                  |

| Device-Dependent Characteristics                                                                                           | ٠     | 39                               |

| 1052, 2150 Error Routine                                                                                                   |       | 39                               |

| 2540/2821 Error Routine                                                                                                    |       |                                  |

| 1403/1443 Error Routine                                                                                                    |       | 41                               |

| 1442, 2501, 2520 Error Routine .                                                                                           |       | 41<br>41                         |

|                                                                                                                            | •     |                                  |

|                                                                                                                            | •     | 41<br>42                         |

| 2671/2822 Error Routine                                                                                                    | • • • | 41<br>42<br>43                   |

| 2671/2822 Error Routine<br>2400 Tape Series Error Routine .                                                                | • • • | 41<br>42                         |

| 2671/2822 Error Routine<br>2400 Tape Series Error Routine .<br>Direct-Access Device Error                                  | • • • | 41<br>42<br>43<br>43             |

| 2671/2822 Error Routine<br>2400 Tape Series Error Routine .<br>Direct-Access Device Error<br>Routine                       | • • • | 41<br>42<br>43<br>43             |

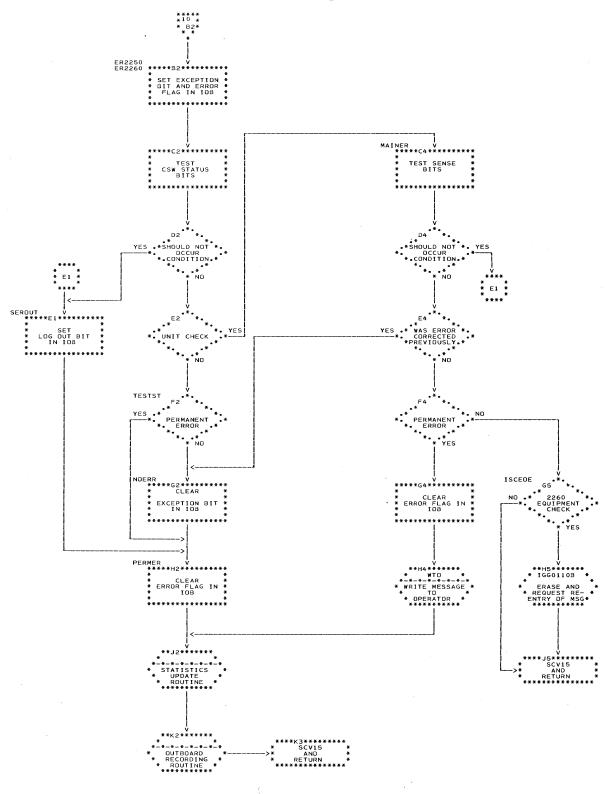

| 2671/2822 Error Routine<br>2400 Tape Series Error Routine .<br>Direct-Access Device Error<br>Routine<br>2250 Error Routine | • • • | 41<br>42<br>43<br>43<br>45<br>48 |

| 2671/2822 Error Routine<br>2400 Tape Series Error Routine .<br>Direct-Access Device Error<br>Routine                       | • • • | 41<br>42<br>43<br>43             |

| Common Routines                         |

|-----------------------------------------|

| Error Interpreter Routine 48            |

| Write-to-Operator Routine 48            |

| Statistics Update Routine 49            |

| I/O Outboard Recording Routines 50      |

|                                         |

| The Outboard Recorder 50                |

| The Statistical Data Recorder 50        |

| Module Operation 50                     |

| PART IV: SVC TRANSIENT AREA ROUTINES 52 |

| SVC Purge Routine                       |

| Purge Complete Subroutine 54            |

| Restore Routine                         |

|                                         |

| DEVTYPE Routine                         |

| IOHALT Routine 54                       |

| PART V: CONTROL BLOCK AND TABLE         |

| FORMATS                                 |

| Attention Table 55                      |

| Channel Table                           |

|                                         |

| Data Control Block                      |

| Data Extent Block                       |

| Device Table 59                         |

| Event Control Block<br>Input/Output Block<br>Logical Channel Word Table<br>Request Element Table<br>Statistics Table<br>UCB Lookup Table<br>Unit Control Block |   | • | 66<br>67<br>67 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----------------|

| CHARTS                                                                                                                                                         | • | • | <b>7</b> 5     |

| APPENDIX A: LOAD MODULE NAMES                                                                                                                                  | • | • | 84             |

| APPENDIX B: LINKAGES WITHIN THE<br>REQUEST ELEMENT TABLE                                                                                                       | • | • | 84             |

| APPENDIX C: THEORY OF LOGICAL<br>CHANNELS.                                                                                                                     | • | • | 86             |

| APPENDIX D: SYSTEM ENVIRONMENT<br>RECORDING OUTPUT DATA SET FORMAT<br>Header Record<br>Statistical Data Records<br>Record Entries                              | • | • |                |

| INDEX                                                                                                                                                          | • | • | 93             |

## FIGURES

#### CHARTS

| Chart 01. Functional Flow of the                    | Chart 06. Input/Output Interruption                             |

|-----------------------------------------------------|-----------------------------------------------------------------|

| Input/Output Supervisor                             | Analysis (2)                                                    |

| Chart 02. Control Flow Within the EXCP              | Chart 07. Scheduling of an                                      |

| Supervisor                                          | IBM-Supplied Error Routine 81                                   |

|                                                     | Chart 08. General Operating Procedure                           |

| Error EXCP Routine                                  | for Device-Dependent Error Routines 82                          |

| Input/Output Interruption Supervisor 78             | Chart 09. OBR/SDR Module Flow 83<br>Chart 10. General Operating |

| Chart 05. Input/Output Interruption<br>Analysis (1) | Procedure-Graphics 83                                           |

## TABLES

Table 1. Modular Areas Within the  The input/output (I/O) supervisor is the portion of the control program that issues the privileged I/O instructions and supervises the resulting I/O operations for any program that requests I/O device activity. The I/O supervisor has two purposes:

- To handle I/O requests, which are requests for the execution of channel programs.

- To handle I/O interruptions, which result from the execution of channel programs and from operator intervention.

To facilitate the handling of the I/O requests and interruptions, the I/O supervisor is divided into two major program sections:

- Execute channel program (EXCP) supervisor.

- Input/output (I/O) interruption supervisor.

These major sections are resident in main storage and provide control program support for the execution of channel programs.

The EXCP supervisor handles all I/0 requests issued by means of the EXCP macroinstruction andSVC 15. I/0 The interruption supervisor handles all I/0 interruptions, provides error recovery supervision, indicates to the user when an I/O request is complete, and restarts available devices and channels.

Routines and control areas used with the I/O supervisor are:

- Error routines.

- Purge routine and restore routine.

- DEVTYPE routine.

- IOHALT routine.

- Control blocks, tables, and queues.

Error routines are transient and are called by the I/O supervisor to handle device and channel errors and unusual conditions. The purge and restore routines are also transient and are used, respectively, to remove from the system I/O requests that are active or waiting to be started and to reschedule I/O requests that previously removed. The DEVTYPE rouwere passes information concerning tine I/0 device characteristics to the user. The IOHALT routine allows the graphics or telecommunications user to halt I/O activity on any device except a direct access device.

Control blocks, tables, and queues all reside in main storage. Control blocks are created either by the user at assembly time by means of control statements and macroinstructions, or by the system at system generation time. Tables, and also the control fields for queues and the elements to be queued, are created at system generation time. The queues are then maintained by the I/O supervisor.

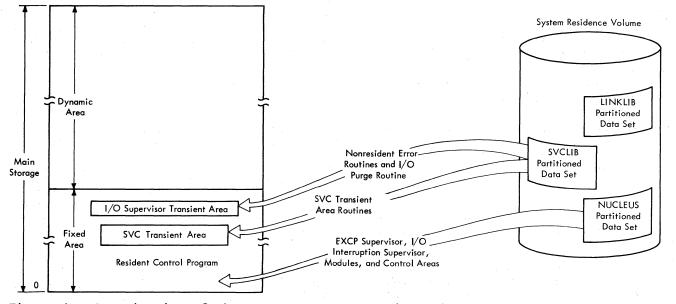

Figure 1 shows the organization of the I/O supervisor within main storage.

• Figure 1. Organization of the Input/Output Supervisor Within Main Storage

#### THE INPUT/OUTPUT SUPERVISOR

The I/O supervisor starts and supervises I/O operations for programs that request I/O device activity.

Processing programs and the control program request I/O device activity via a macro-instruction. The type of macroinstruction that is used depends upon the use of an access method.<sup>1</sup>

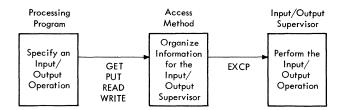

If an access method is used, the expansion of the GET/PUT or READ/WRITE macroinstruction contains a branch to access method routines. These routines construct a channel program, provide control block information, and cause control to be routed to the I/O supervisor via an EXCP macroinstruction.

If an access method is not used to request the execution of channel programs, the processing program or the control program must issue the EXCP macroinstruction. Before doing so, they must provide the necessary channel program and the control block information required for the I/O supervisor.<sup>2</sup>

Figure 2 illustrates the relationships among a processing program or the control program, an access method, and the I/O supervisor.

Figure 2. Relationships Among a Processing Program or the Control Program, an Access Method, and the Input/Output Supervisor When a channel program must be retried because of an error in its execution, SVC | 15 is issued, usually by IBM-supplied error | routines.

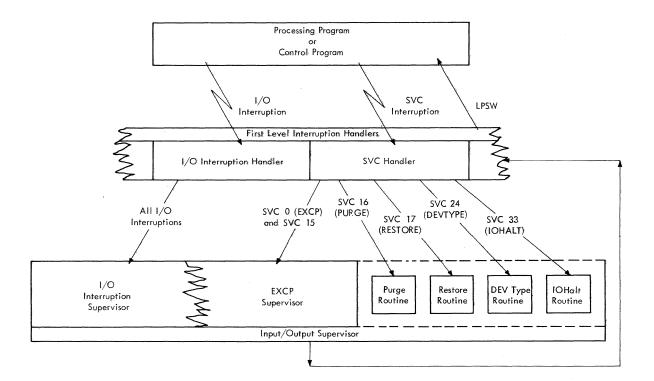

Execution of the EXCP macro-instruction or SVC 15 causes an interruption. This and all other interruptions in the system are handled by the first level interruption handlers (FLIH).<sup>3</sup> After storing the program status word (PSW) and saving the contents of general registers, a FLIH routes control to the routine that performs the functions required by the interruption.

The I/O supervisor receives control from a FLIH after the following interruptions:

- Supervisor call (SVC) interruptions, caused when SVC 0 (EXCP) and SVC 15 are executed.

- I/O interruptions of all types.

An SVC interruption also occurs when SVC 16, 17, 24 or 33, respectively, for the PURGE RESTORE, DEVTYPE or IOHALT macroinstruction is executed. A FLIH gains control; however, since the required purge or restore routine is transient, it must be called into the SVC transient area before control is given to it.

Figure 3 shows the flow of control within the system and within the I/O supervisor from the time an SVC or I/O interruption occurs until the time the interruption is handled and the control program or a processing program is given control.

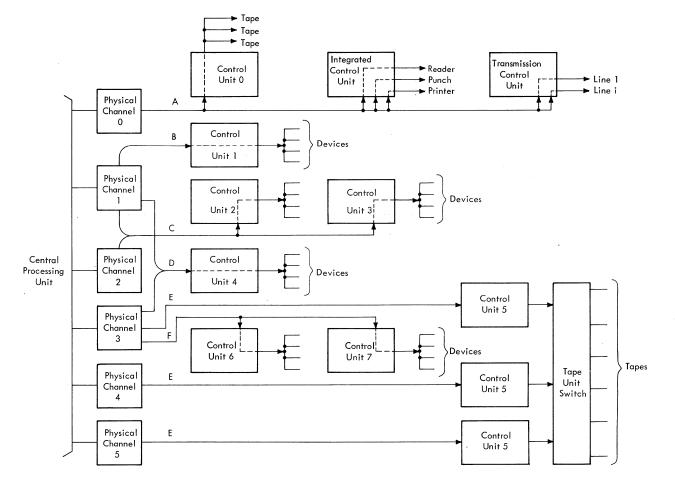

Within the mainline code of the I/O supervisor, there are five modular areas (these are not load modules). There are three modular areas within the EXCP supervisor and two within the I/O interruption supervisor. The size and function of these areas is dependent upon system configuration. Their inclusion in the I/O supervisor is determined at system generation (SYSGEN) time.

<sup>&</sup>lt;sup>1</sup>Access method descriptions are contained in the section "Data Access Methods" of the <u>IBM System/360 Operating System: Data</u> <u>Management publication, Form C28-6537.</u> <sup>2</sup>The necessary information is contained in the section "Execute Channel Program (EXCP) Macro-Instruction" of the System Programmer's Guide.

<sup>&</sup>lt;sup>3</sup>The FLIHs are described in the <u>IBM</u> <u>System/360</u> Operating System: Fixed-Task <u>Supervisor</u>, Program Logic Manual, Form Y28-6612.

Figure 3. Control Flow Within the System and the Input/Output Supervisor

The modular areas, shown in Table 1, are:

- <u>Test channel</u>. A test channel module determines if a channel is available for the device that is to be used for an I/O request.

- Enqueue and dequeue. An enqueue module queues I/O requests that cannot be immediately started. After an I/O request has finished, a dequeue module removes the request from the queue.

- <u>Start I/O</u>. Start I/O modules provide device information and actions preceding the issuance of a start I/O instruction for the device.

- <u>Channel search</u>. When an I/O request has finished such that a channel becomes available, a channel search module determines the next I/O request to be started on that channel by searching queues constructed by enqueue modules.

- <u>Trapcode</u>. Trapcode modules establish information for a device after an I/O interruption associated with that device.

#### Table 1. Modular Areas Within the Input/Output Supervisor

| Major<br>Program                            |              | Modular Area                                                                  |

|---------------------------------------------|--------------|-------------------------------------------------------------------------------|

| Section                                     | Name         | Features                                                                      |

| EXCP<br>Super-<br>visor                     |              | One module per logical<br>channel; created at<br>SYSGEN time.                 |

|                                             | and          | Three modules; selected<br>at SYSGEN time according<br>to enqueueing options. |

|                                             | Start<br>I/O | One module per device<br>class; selected at<br>SYSGEN time.                   |

| I/O<br>Inter-<br>ruption<br>Super-<br>visor |              | One module per physical<br>channel; created at<br>SYSGEN time.                |

|                                             | -            | One module per device<br>class; selected at SYSGEN<br>time.                   |

The object module for the I/O supervisor is named IEAASU00. This load module includes the mainline code and the modular areas of the I/O supervisor and in addition, includes the dispatcher, the exit effector, the FLIHs, and the communication vector table (CVT) of the fixed-task supervisor. The load module names for the various error routines and the purge and restore routines are summarized in Appendix A.

Routines that supplement the handling of I/O requests and interruptions are appendages to the I/O supervisor. (They do not alter the I/O supervisor program.) These | appendages may be supplied by the user of the I/O supervisor.

Appendages are called into main storage by the open routine and are removed by the close routine or at the end of a job step.<sup>1</sup> When the I/O supervisor branches to an appendage, the current PSW has all interruptions except machine check interruptions masked as disabled; it indicates the supervisor state, and a protection key of zero.

There are five exits from the I/O supervisor to an appendage vector table; the table contains addresses, which may or may not route control to an appendage. (The appendage vector table is described in Part V: Data Extent Block.) If control is not routed to an appendage, the I/O supervisor retains control and continues normal processing.<sup>2</sup>

The five appendage exits are:

- End-of-extent. The provision for an end-of-extent appendage is included within the EXCP supervisor for directaccess device I/O requests. The appendage is given control when the EXCP supervisor determines that execution of the request will violate the extent limits of the data set.

- <u>Start I/O.</u> The provision for a start I/O appendage is included within the EXCP supervisor for all I/O requests. The appendage receives control preceding the execution of the start I/O (SIO) instruction for the request.

- <u>Program-controlled interruption</u>. The provision for an appendage for a program-controlled interruption (PCI) is included within the I/O interruption supervisor. The PCI appendage returns

<sup>1</sup>The OPEN and CLOSE routines are described in the publication <u>IBM System/360 Operating</u> <u>System: Input/Output Support</u> <u>(OPEN/CLOSE/EOV), Program Logic Manual</u>, Form Y28-6609. control to the I/O interruption supervisor where normal processing continues.

- <u>Channel end</u>. The I/O interruption supervisor exits to a channel end appendage after a channel end interruption occurs, before indicating to the user how the I/O request completed. (The channel end appendage is also entered when the channel end interruption is accompanied by a wrong length indication or a unit exception, or both.)

- <u>Abnormal end</u>. The I/O interruption supervisor exits to an abnormal end appendage whenever there has been an error associated with the processing of an I/O request.

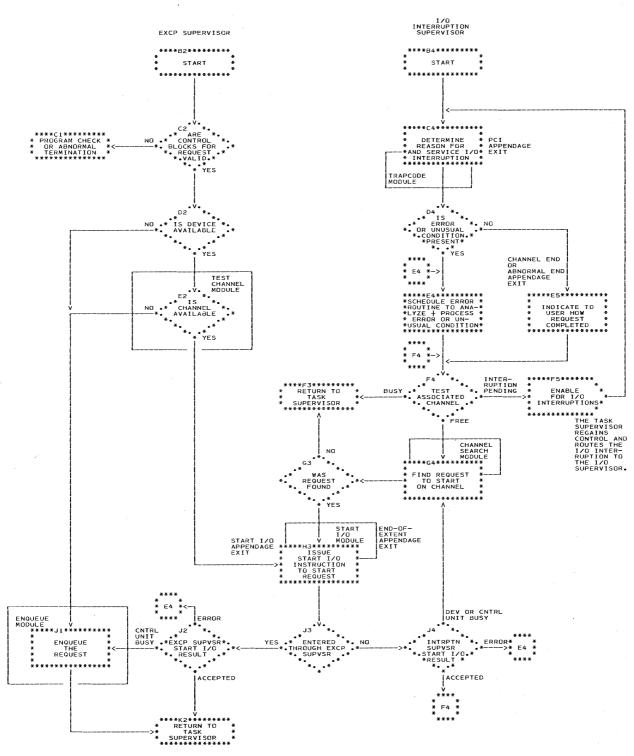

#### EXCP SUPERVISOR

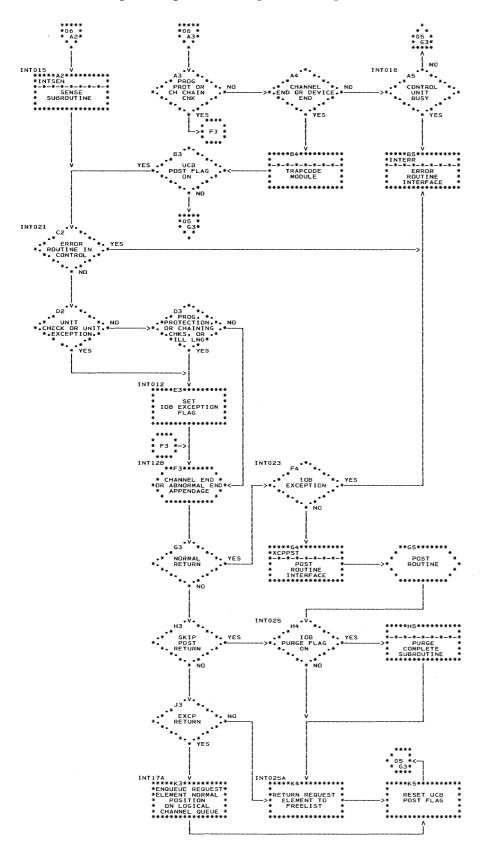

The EXCP supervisor is the portion of the I/O supervisor that starts the channel programs requested by use of the EXCP macro-instructions and SVC 15. It performs the same procedures when initiating the channel programs for both. Chart 01 shows the functional flow of the EXCP supervisor, and also of the I/O interruption supervisor. (All charts precede Appendix A.)

Before accepting a channel program for execution, the EXCP supervisor determines if:

- The control blocks for the I/O request are valid.

- The device for the I/O request is available.

- A physical channel for the device is available.

If the first of these conditions is not met, either a program check results or the task requesting the I/O activity is abnormally terminated. If either the device or the channel is not available, the I/O request is queued for subsequent processing.

When the required conditions are met, the EXCP supervisor issues an SIO instruction, which in turn initiates the commands in the channel program. The following conditions may result:

• The channel program may be accepted and the I/O operations successfully started.

1

<sup>&</sup>lt;sup>2</sup>Additional information regarding the use of appendages can be found in the EXCP section of the System Programmer's Guide.

- An error may occur during initiation of the channel program, in which case, control is given to the I/O interruption supervisor and the reason for the error is determined. If necessary, an error routine is scheduled.

- The control unit for the device may signal busy. In this case, the channel program is not accepted and the I/O request is queued (except in the case of some telecommunications requests).

After the resulting condition is handled, control returns to the FLIH.

#### **I/O INTERRUPTION SUPERVISOR**

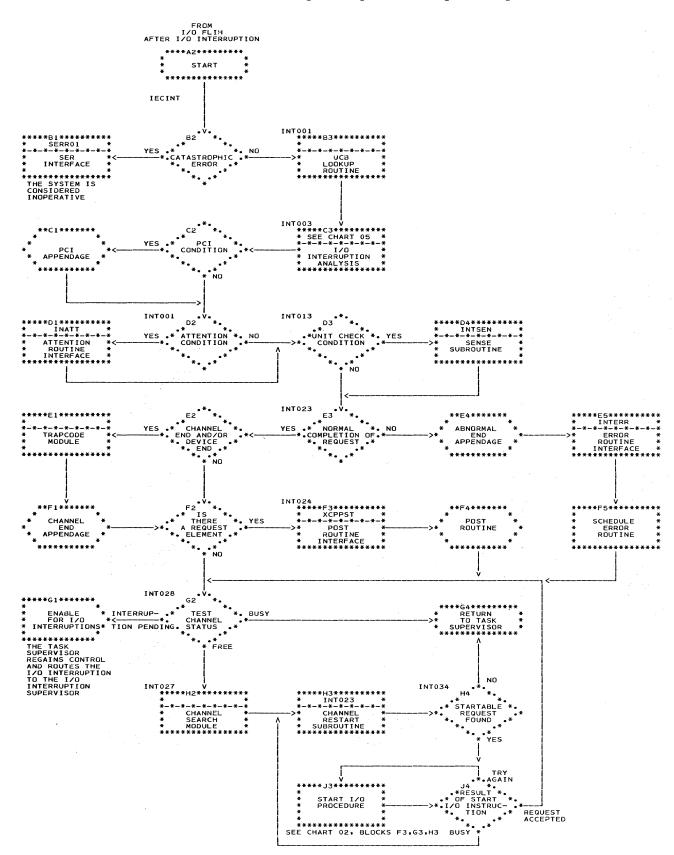

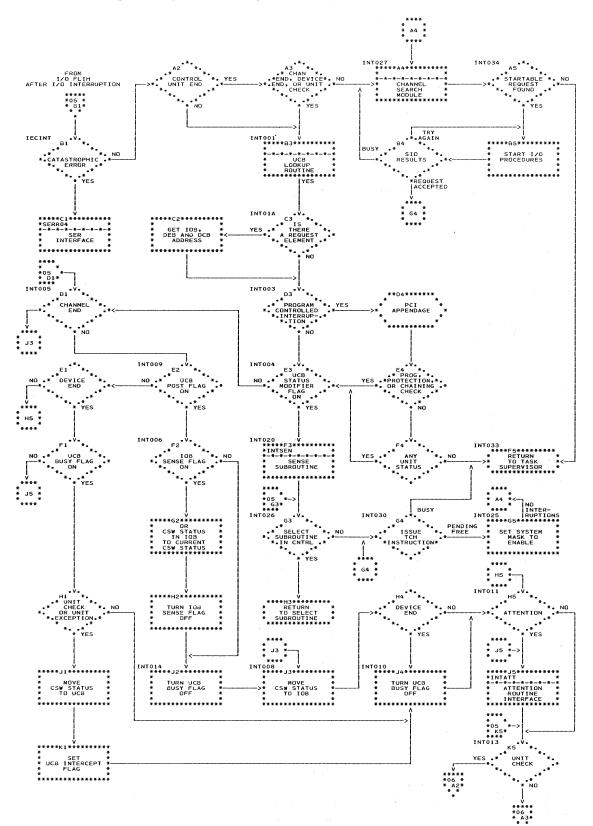

An I/O interruption occurs after signals from I/O devices have been generated (in response to channel program execution and operator action) and accepted by the central processing unit (CPU). The I/O interruption supervisor analyzes status bits in the channel status word (CSW), which is stored as a result of the I/O interruption, to determine the reasons for the I/O interruption.

The I/O interruption supervisor processes the following, when denoted by the CSW status bits:

- <u>Attentions</u>. The appropriate attention routine is entered.

- <u>Status modifier situations</u>. Status modifier conditions, such as a control unit busy condition that causes an I/O request to be queued, are handled.

- <u>Control unit end, channel end, and</u> <u>device end interruptions</u>. These interruptions indicate normal ending conditions and normal processing continues. Normal completions are indicated to the user.

- <u>Busy conditions</u>. When the selected I/O device or control unit is unavailable, the I/O request is queued.

- <u>Unit check</u>. A sense command is issued to obtain additional information regarding the unit check.

- Errors and unusual conditions. When errors, such as program, channel chaining, and protection checks, and unusual conditions, such as unit exception and wrong length indication, are detected, an error routine is scheduled. An uncorrectable error is indicated to the user as a permanent error condition.

- <u>Program-controlled interruptions.</u> A PCI appendage supplied by the user of the I/O supervisor is entered.

- <u>Catastrophic errors</u>. When catastrophic errors (channel data check, channel control check, and interface control check CSW bits) occur, the system environment is recorded and the CPU is put into the wait state. The system is then considered inoperative and the Initial Program Load procedure must be followed to re-initialize the system. (System environment recording (SER) is a group of programs that collect and record data regarding System/360 machine errors.)

The completion of an I/O request is indicated by a channel end or a channel end and device end interruption. The I/O interruption supervisor indicates this completion to the user.

After the reason for the I/O interruption has been determined and the interruption processing completed, the I/O interruption supervisor determines the state of the channel upon which the interruption was received. Pending I/O interruptions are accepted and handled. If the channel is free, an attempt is made to restart it with a queued I/O request (one that was previously requested, but could not be started The appropriate queues are immediately). searched until an I/O request is started or until it is determined that there are no I/O requests that can be started on the free channel. Control returns to the FLIH.

#### THE ERROR ROUTINES

\_\_\_\_\_

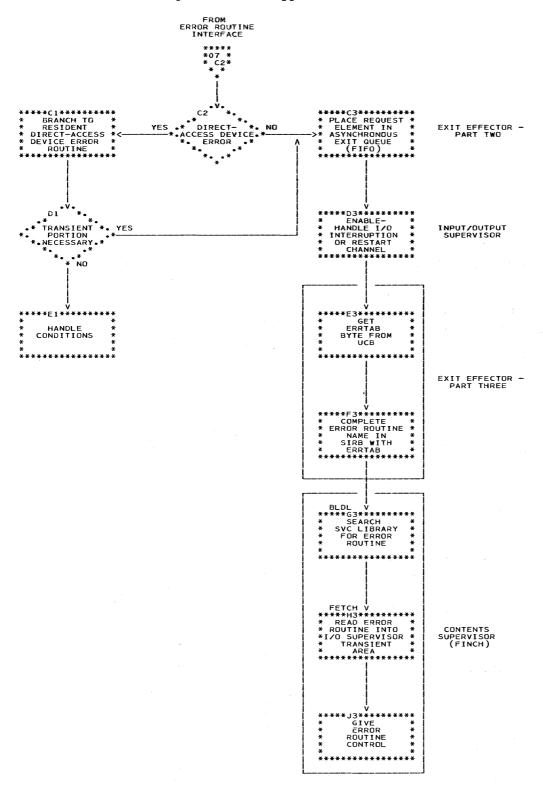

Standard IBM-supplied error routines are selected at SYSGEN time for each type of I/O device in the system. Error routines are transient and reside in the SVC library.<sup>1</sup> However, the portions of the directaccess device error routine that are necessary for the system residence device and for frequent unusual conditions (end-of-cylinder, head switching, alternate track procedures, etc.) are resident in main storage. The names of the error routine load modules are in Appendix A.

Whenever an I/O interruption occurs and the I/O interruption supervisor detects an error that requires error recovery procedures, it determines whether or not an IBM-supplied error routine is to be used.

<sup>&</sup>lt;sup>1</sup>The requirements for an error routine are discussed in the EXCP section of the System Programmer's Guide.

An indication of the required error routine and of the channel program that developed the error are passed to the task supervisor's exit effector and an asynchronous exit is requested. The error routine must be scheduled asynchronously because immediate in-line processing of the error would hinder efficient channel scheduling.

The appropriate error routine is entered into the I/O supervisor transient area (providing the error routine is not resident) and, when scheduled, is given control. The error routine determines the type of error and, where possible, issues the ERREXCP macro-instruction in an attempt to retry the channel program and to recover from the error. At completion of error processing (successful or unsuccessful), the error routine issues the ERREXCP macroinstruction so that the I/O request can be properly terminated by the I/O interruption supervisor. The completion is indicated to the user and the error routine returns control to the task supervisor.

#### THE PURGE AND RESTORE ROUTINES

The SVC purge and restore routines are transient and are called into the SVC transient area whenever a PURGE or RESTORE macro-instruction (SVC 16 and SVC 17, respectively) is issued. The load module name for the SVC purge routine is IGE0001F and for the SVC restore routine is IGE0001G.

The SVC purge routine removes active or queued I/O requests from the system. The SVC restore routine reschedules I/O requests that were previously purged.

There is also an I/O purge routine; the load module name is IGE0025E. This routine is used only by the I/O supervisor and should not be confused with the SVC purge routine, which is called by means of a system macro-instruction. The I/O purge routine removes certain requests from the system whenever there has been a permanent error. It is discussed in Part II: Error Routine Interface.

#### THE CONTROL BLOCKS, TABLES, AND QUEUES

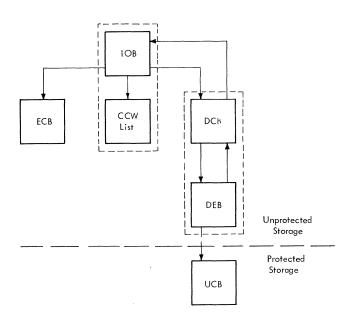

The I/O supervisor, as well as other portions of the control program, records the status of devices, data sets, and internal routines in control blocks, • Figure 4. tables, and queues.

The control blocks supply information to the I/O supervisor regarding I/O requests and devices, and regarding the data sets required for the execution of the requests. The tables point to device- and channeldependent modules and are used internally by the I/O supervisor. Queues are used by the I/O supervisor for I/O requests that cannot be started immediately. Part V contains detailed formats and explanations of the control blocks and tables.

#### CONTROL BLOCKS

Control blocks maintain the information that concerns the status and activity of I/O devices, requests, and interruptions. The I/O supervisor is concerned with the following control blocks:

- Input/output block.

- Data control block.

- Data extent block.

- Event control block.

- Unit control block.

These control blocks, and the pointers indicating their relationships, are shown in Figure 4.

e 4. Control Blocks Used by the Input/Output Supervisor

#### Input/Output Block

An input/output block (IOB) is the communication medium between a routine that requests I/O operations and the I/O supervisor. The address of an IOB is passed to the I/O supervisor when an I/O request is given.

The contents of an IOB include:

- The address of the channel program, which consists of a group of channel command words (CCW), to be executed.

- An indication that the channel program is or is not related to other channel programs. (Related channel programs are all associated with the same data set. Each is dependent upon the successful completion of its preceding related channel programs. If a permanent error occurs that is associated with a related channel program, the I/O purge routine purges the remaining related requests for the data set.)

- A storage area for the CSW, which is stored by the I/O supervisor at the completion of an I/O request.

- The initial seek address for a directaccess device.

- The address of the data control block and the event control block.

#### Data Control Block

A data control block (DCB) contains information that pertains to the current use of a data set and contains the address of a data extent block. A DCB provides the I/O supervisor with the status of error correction procedures for each data set and indicates whether or not IBM-supplied error routines are to be used for the data set.

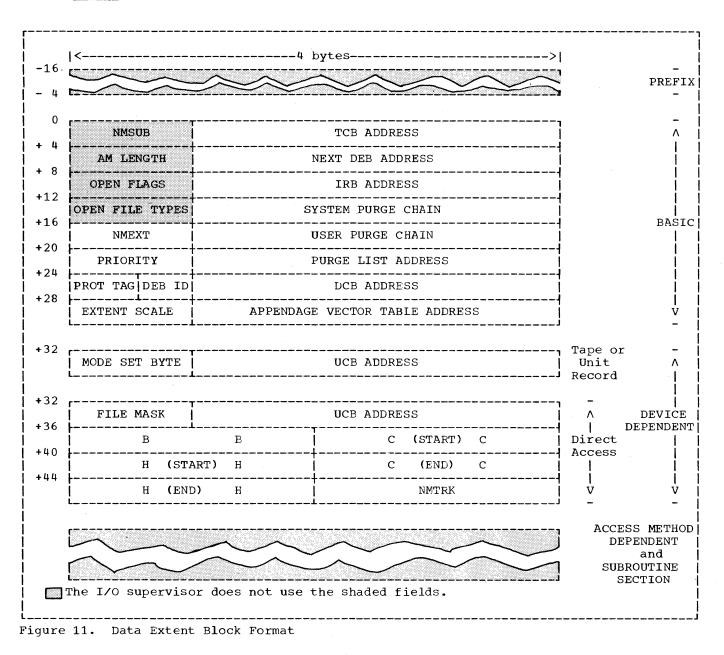

#### Data Extent Block

A data extent block (DEB) is an extension of the information contained in a DCB. Each DEB is associated with a DCB, and the two blocks address each other. A DEB describes the extent of a data set; it indicates the storage medium, the location, and the boundaries of the data set, contains an appendage table address, and provides data protection and priority information.

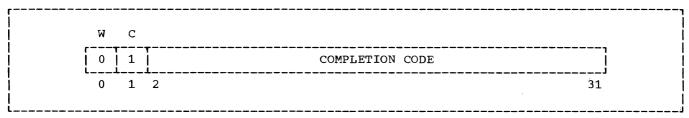

#### Event Control Block

An event control block (ECB) is used by the I/O supervisor to indicate to the user when and how the execution of his channel program completed. A normal completion is determined by either a channel end or a channel end and device end interruption. The I/O supervisor indicates a request has completed, successfully or not, by posting the request complete by use of the post routine of the task supervisor.<sup>1</sup>

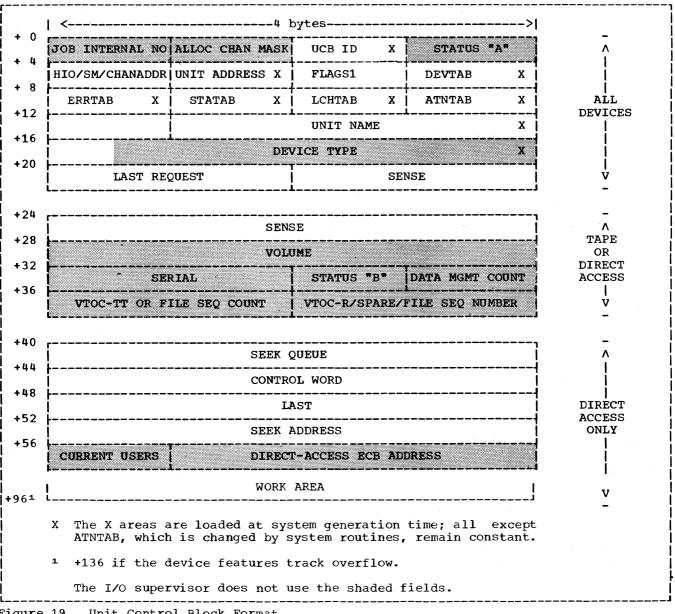

#### Unit Control Block

A unit control block (UCB) is the means by which the I/O supervisor notes and determines the activity and status of each I/O device attached to the system. A UCB represents the I/O device for the volume upon which a data set resides. It is addressed by a DEB.

There is one UCB for each I/O device or telecommunications line addressed in the system. One UCB per volume is required if a data set resides on two or more volumes that are mounted concurrently upon separate I/O devices. In this case, each of the UCBs is addressed by the same DEB.

The contents of the UCB include:

- The unit address, which is used in the SIO instructions for the device.

- The type of device the UCB represents (e.g., IBM 2311 Disk Storage, IBM 2400 Magnetic Tape Unit, etc.).

- The flag bits, which indicate the current status of the associated I/O device. For example, the UCB busy bit may be set to indicate that the device is currently in operation. Other flag bits may be set to indicate UCB not ready, control unit busy, post, etc.

- An area for sense information, which details the conditions, such as a programming error or equipment malfunction, that cause a unit check interruption. When the I/O supervisor issues a sense command, up to six bytes of sense information from the control unit of the device is read into this area; the number of bytes of information that is meaningful varies with the device type.

<sup>1</sup>For information concerning the post routine, refer to the Fixed-Task Supervisor, Program Logic Manual. • Reference fields, consisting of an indexing value or an address, that refer to tables. When the reference is an indexing value, the I/O supervisor adds it to the starting address of the pertinent table to obtain the address of the proper entry. When the reference is an address, it is of the proper entry.

#### TABLES

Tables contain pointers to control blocks and to device- and channel-dependent routines, modules, and queues. They also provide an area for device statistics. The I/O supervisor contains the following tables:

- UCB lookup table.

- Channel table.

- Device table.

- Statistics table.

- Attention table.

- Request element table.

- Logical channel word table.

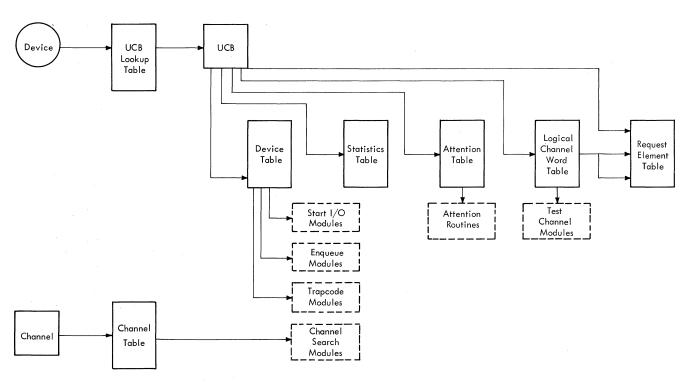

These tables, and the pointers indicating their relationships, are shown in Figure 5.

#### UCB Lookup Table

The UCB lookup table contains the address of each UCB in the system and the values that are necessary to locate these UCB addresses within the table. The table is divided into channel values, control unit values, and UCB addresses.

After an I/O interruption occurs, the I/O supervisor calculates the address of the UCB that represents the I/O device associated with the interruption. The table values and the I/O address, which is stored in the PSW, are used to perform the calculation.

#### Channel Table

The channel table is used by the I/O supervisor to re-enable a channel for additional I/O interruptions and to locate the channel search module for the channel. The table contains one entry for each physical channel attached to the system.

Figure 5. Tables Used by the Input/Output Supervisor

#### Device Table

The device table is the means by which the I/O supervisor determines the proper device-dependent modules for a device. Each entry in this table contains the address of a start I/O module, an enqueue module, and a trapcode module.

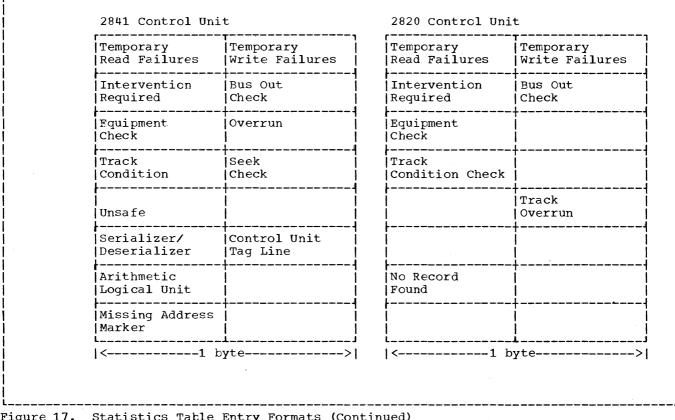

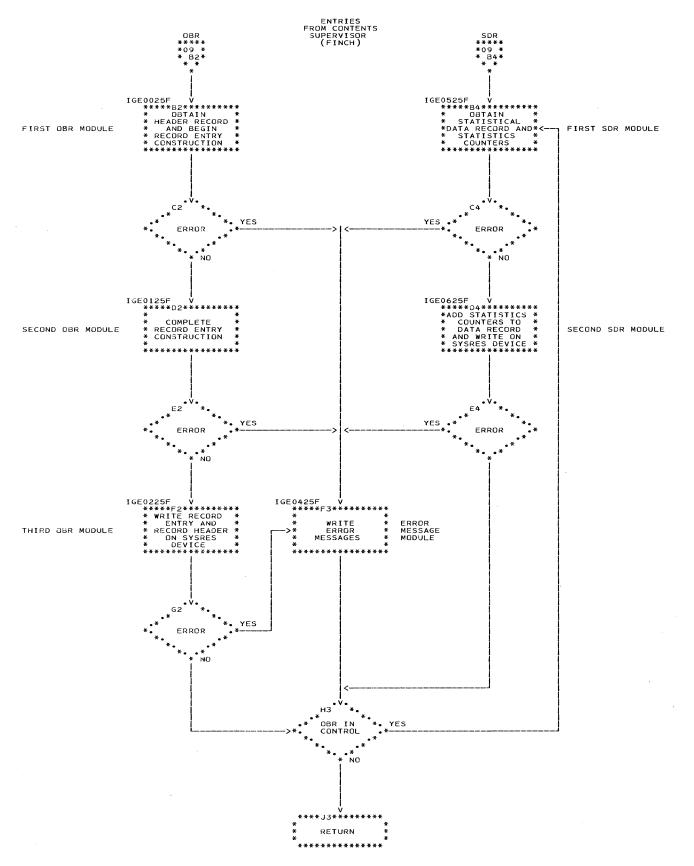

#### Statistics Table

The statistics table contains one entry, which includes up to eight statistics counters, for each I/O device attached to the system. Each statistics counter is used by the IBM-supplied error routines to count the number of temporary read and write errors, equipment checks, interventions required, and other statistics that depend on the particular device type.

Whenever a statistics counter overflows or a permanent error occurs, the SER program's statistical data recording routine uses the statistics counters to update statistical data records. Statistical data records are expansions of the statistics counters. They reside on the system residence device, so that they are available for recall and analysis.

#### Attention Table

The attention table is constructed at SYSGEN time to contain the addresses of attention routines. Attention routines are specified by system routines to service attention interruptions.

There are two types of attention interruptions:

- Normal attention interruptions, which are indicated by the attention bit in the CSW status field.

- Unsolicited device end interruptions, which are caused by the transition from the not-ready to the ready state that occurs when the operator presses the ready button.

When a system routine desires that an attention or unsolicited device end interruption is to be handled, it places an indexing value into the UCB for the device. When the indexing value is added to the starting address of the attention table, the address of the appropriate entry within the table is obtained. The system routine must have placed into this entry, at SYSGEN time, the address of the attention routine for the device. Since the attention table is constructed at SYSGEN time, it is available only to routines that specify their attention routines at SYSGEN time.

When an attention interruption occurs, the I/O supervisor passes control to the attention routine. If execution of the attention routine is not desired, the system routine must place a zero into the UCB instead of an indexing value. The first entry in the attention table contains a branch back to the I/O supervisor; thus, when an attention interruption occurs, the starting address added to zero yields the address of the first entry in the table and the I/O supervisor regains control.

#### Request Element Table

The request element table<sup>1</sup> consists of a number of request elements that are used to represent I/O requests. The number of elements in the table is determined at SYSGEN time and remains fixed.

The I/O supervisor issues a request element to represent each I/O request given by means of the EXCP macro-instruction. An element is not issued when an I/O request | is retried by means of SVC 15. When the element is issued, the I/O supervisor stores information into it, which includes the addresses of the UCB, DEB, and IOB associated with the I/O request.

Each request element can be in one of three states:

- Available.

- Active.

- Queued.

An example of the linkage relationships of the available, active, and queued request elements within the request element table is presented in Appendix B.

Available Request Elements: Available request elements are not in current use; they are either unused or contain information that is no longer needed by the I/O supervisor. These request elements are issued to represent incoming I/O requests.

<sup>1</sup>In some documentation, the request element table is referred to as the 12 star (12\*) table and its request elements as 12\* elements. The available request elements are linked together by means of a "link field" that is contained in the first two bytes of each element. This linkage of available request elements forms a "freelist". Each element in the freelist points to the next element. Because other request elements in the request element table might be active or queued, members of the freelist are not necessarily contiguous within the table.

The first element in the freelist, referred to as "next available", is always the next request element issued by the I/O supervisor for an incoming I/O request. The "freelist pointer" contains the address of the next available request element. It resides within the I/O supervisor and is addressed by an entry in the communications vector table (CVT).<sup>1</sup>

The last element in the freelist is the last available request element and is identified by means of a "dummy address" in its 2-byte link field. The dummy address is a hexadecimal FFFF (i.e., has all bits on). When there are no available request elements, the freelist pointer contains the dummy address to indicate that the freelist is empty.

Active Request Elements: Active request elements correspond to I/O requests that have been started but have not yet been completed. The I/O supervisor indicates that a request element is active by placing the address of the active request element into the UCB that represents the device being used for the I/O request. When an I/O interruption associated with the device occurs, the I/O supervisor finds the active request element, which is then used to find the various control blocks that are used during the processing of the I/O interruption.

Queued Request Elements: Queued request elements correspond to I/O requests that could not be started immediately. The elements belonging to the same queue are linked together by means of the link fields located in the first two bytes of the elements. The last element in each queue is denoted by means of the dummy address within its link field. During the queueing procedure, only the contents of the link fields in the request elements are changed.

<sup>1</sup>The CVT is described in the Introduction to Control Program Logic, Program Logic Manual.

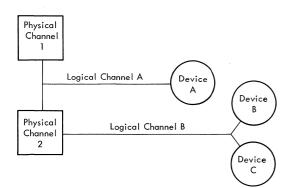

#### Logical Channel Word Table

The logical channel word table contains a logical channel word entry that corresponds with each logical channel in the system. A multiplexor channel has one logical channel; a selector channel may have more than one. (For further information concerning logical channels, refer to Appendix C.)

A logical channel word designates the first and last request elements in the logical channel queue associated with a logical channel. If the queue is empty, the logical channel word contains in its first two bytes the dummy address of hexadecimal FFFF. A logical channel word also contains the address of a channel-dependent test channel module.

#### QUEUES

The I/O supervisor uses two types of queues for I/O requests:

- Logical channel queues.

- Seek queues.

The logical channel queues consist of request elements that represent I/O requests for the execution of channel programs on either sequential or direct-access devices.

The seek queues contain request elements that represent I/O requests for seek operations to be executed on direct-access devices. When a seek operation has been executed and the access arm of the directaccess device is in the proper position, the representative request element is enqueued in the appropriate logical channel queue.

#### Logical Channel Queues

I/O operations awaiting execution are held for subsequent processing in a logical channel queue. There is one logical channel queue associated with each logical channel in the system. (See Appendix C.) A multiplexor channel has one logical channel queue; a selector channel may have more than one. The last request element in each logical channel queue is identified by the dummy address in the link field of the element.

#### Seek Queues

The I/O supervisor uses seek queues in conjunction with logical channel queues to overlap seek operations for non-drum direct-access devices that are attached to the same physical channels. There is one seek queue associated with each non-drum direct-access device in the system. The UCB for a direct-access device contains a seek queue control word that indicates the seek queue for the device. When the seek queue is empty, the seek queue control word contains in its first two bytes the dummy address of hexadecimal FFFF.

When an I/O request is given for a direct-access device, a seek address is indicated by the user in the associated IOB. This seek address is used by the I/O supervisor to issue an initial seek command required for the requested I/O operations.

When the direct-access device necessary to execute the initial seek command is busy, the request element representing the I/O request is enqueued in the seek queue for that device. When the direct-access device becomes available and the seek command has been executed so that the access arm is at the proper address, the request element is dequeued from the seek queue and enqueued in the logical channel queue associated with the device and the physical channel. The remaining I/O operations specified in the channel program for the I/O request are then started when a physical channel and the device are available.

#### Queueing Procedures

The I/O supervisor effects linkage within the queues of request elements in the request element table by means of three types of queueing procedures: first-infirst-out (FIFO), priority, and ordered. The user selects queueing procedures at SYSGEN time.

In FIFO queueing, a request element is queued according to the order in which its corresponding I/O request is received (pushup queue). The queue is constructed and maintained so that the next request element to be retrieved is the oldest element in the queue.

In priority queueing, a request element is queued according to the dispatching priority of the task associated with its corresponding I/O request. The next request element to be retrieved is that with the highest priority.

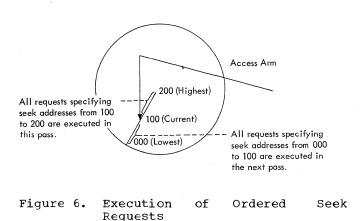

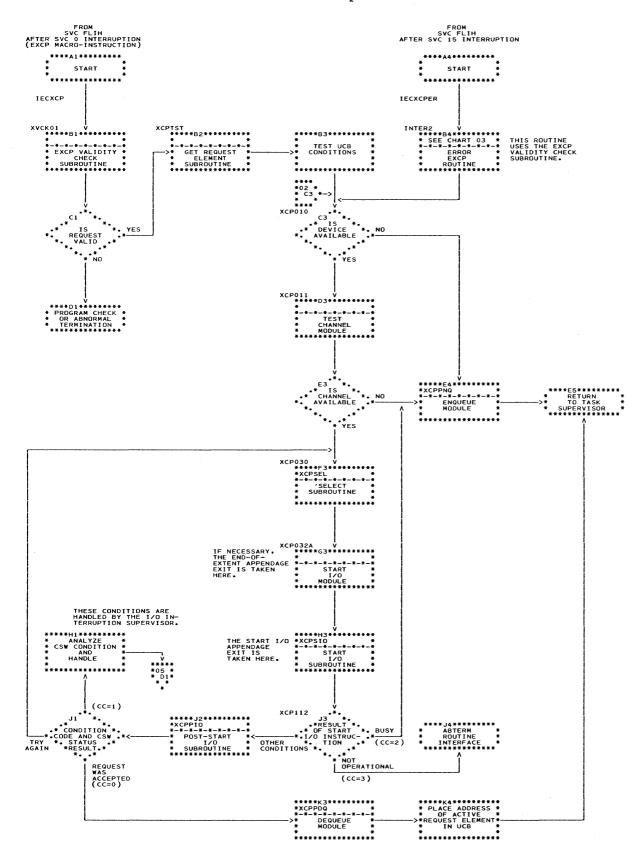

In ordered queueing, a request element, representing an I/O request for a directaccess device, is queued according to the numerical order of the given seek address. The seek addresses are ordered from the lowest to the highest. Related requests are queued in FIFO arrangement and are executed where appropriate during the ordered "sweep" of the direct-access arm. Ordered queueing minimizes the movement of the arm. The EXCP supervisor receives control initially from the SVC FLIH after either an SVC 0 or an SVC 15 interruption. When the EXCP supervisor is entered, the current PSW has all interruptions except machine check interruptions masked as disabled, indicates supervisor and running states, and has the supervisor protection key of zero.

The EXCP macro-instruction (SVC 0) is used to request normal I/O processing of a channel program. SVC 15 is used by the error routines to request that a channel program whose execution encountered an error be retried and also to indicate a permanent error or a successful retry. The I/O purge routine uses SVC 15 to return control to the I/O supervisor after related requests are purged.

- The user of EXCP or SVC 15 is responsible for certain fields within the DCB and the IOB associated with the I/O request. Within the DCB, the user must ensure that:

- DCB exception bits set to 11, indicating a permanent error on the data set, are reset to 00. If this is not done, further related requests for that data set are posted as complete without execution.

- DCB exception bits set to 01, indicating error recovery procedures are in progress, remain at this setting.

- The tape block count remains unchanged until the IOB associated with the request has been posted complete.

Within the IOB, the user must ensure that:

• The block count increment amount for tape block counts is reset if the channel program indicated by the IOB changes.

The field must be zero if block count updating is not desired.

The field must be negative for a backspace.

The field must be zero for a rewind; the DCB block count field must also be zero.

• The unrelated flag is on to indicate the I/O request is unrelated or is off to indicate the I/O request is related, and must be handled as such.

- The start address contains the address of the first CCW to be executed in the channel program.

- The channel program description indicates the type of chaining in the channel program, as follows:

- 00 No chaining

- 10 Data chaining

- 01 Command chaining

- 11 Data and command chaining

- The ECB address contains the address of the corresponding ECB.

- The DCB address contains the address of the DCB for the data set on which I/O processing is requested.

When the EXCP supervisor receives control, the address of the IOB that contains the information necessary for the I/O request must reside in general register 1. Processing of the I/O request then takes place.

After the operation of the EXCP supervisor is complete, control returns to the type 1 exit of the SVC FLIH, which determines whether control is to be given to the dispatcher or to the routine giving the I/O request.

Chart 02 shows control flow among the subroutines and the modules within the EXCP supervisor.

#### GENERAL OPERATING PROCEDURE

For a normal I/O request, the EXCP validity check subroutine is entered directly from the SVC FLIH. This subroutine checks the validity of the control blocks associated with the I/O request. It also initializes certain IOB fields that are to be used in later processing.

For an error retry, the EXCP validity check subroutine is entered from the error EXCP routine. The error EXCP routine ensures that the IOB fields are not initialized, since their content is necessary for the error retry. After the EXCP validity check subroutine is executed, the get request element subroutine issues a request element for a normal I/O request. It stores address information required by the I/O supervisor into the next available request element. Because a request element is issued for all normal I/O requests, an additional request element is not issued if an error retry for a particular I/O request becomes necessary.

The flag bits within the UCB that denote the status of the I/O device are inspected to determine if the requested device is available for processing.

When the device is available, a test channel module determines if a physical channel in the device's logical channel is available. The correct test channel module is selected by means of the logical channel word table.

If conditions associated with the device prohibit processing or if the test channel module does not find an available physical channel, the request element is queued for subsequent processing of the I/O request. The appropriate enqueue module is selected by means of the device table entry for the particular device.

When a channel is free and the device is available, the select subroutine is entered. This subroutine selects the appropriate start I/O module for the device by means of the device table and gives control to it. The start I/O module perdevice-dependent functions forms and branches to the start I/O subroutine, which in turn issues the SIO instruction for the I/O request.

The condition code and the CSW (if stored) that results from the execution of the SIO instruction indicate whether the channel program for the request has been started, whether the request element must be queued, or whether the SIO instruction for the I/O request should be re-issued. The start I/O subroutine and the post-start I/O subroutine handle these results.

Once the operations for an I/O request are terminated (because of completion, error, or external action on the device), an I/O interruption occurs. Information concerning the operation of the I/O interruption supervisor is contained in Part II: I/O Interruption Supervisor.

#### OPERATION OF THE SUBROUTINES AND MODULES

The following subroutines, routines, and modules are used to perform the functions of the EXCP supervisor:

- EXCP validity check subroutine.

- Get request element subroutine.

- Error EXCP routine.

- Test channel modules.

- Enqueue and dequeue modules.

- Select subroutine.

- Start I/O modules.

- Start I/O subroutine.

- Post-start I/O subroutine.

EXCP VALIDITY CHECK SUBROUTINE

For both normal (SVC 0) and error retry (SVC 15) entries into the EXCP supervisor, the EXCP validity check subroutine validates the control blocks associated with the request. These control blocks are:

- Input/output block.

- Data control block.

- Data extent block.

- Unit control block.

The addresses of the control blocks are placed into general registers. During this process, the DEB and UCB identification fields are checked, the pointer to the DCB within the DEB is checked, and if applicable, the DEB protection tag is compared against the task control block (TCB) protection tag. If the subroutine finds that the control blocks are on improper boundaries, a program check occurs. On other errors, the ABTERM routine interface of the I/O interruption supervisor is entered and the task is abnormally terminated.

When the EXCP validity check subroutine is used for normal I/O processing, the following IOB fields associated with the last I/O request processed on the currently requested I/O device are reset:

- Error count.

- Flags 1, 2, and 3.

- CSW.

- Condition code.

- Sense.

- ECB code.

When the subroutine is used for error retry, these fields are not reset and control returns to the error EXCP routine.

#### GET REQUEST ELEMENT SUBROUTINE

After a normal I/O request is validated, a request element is issued to represent it. If an error retry for a particular I/O request becomes necessary, an additional request element is not required because one had been previously issued. Control block information is loaded into the request element, and UCB conditions, which determine if the request element must be queued, are tested.

If there is no available request element (i.e., the freelist pointer contains the dummy address of hexadecimal FFFF), the EXCP supervisor uses an enable/disable loop (pseudodisable) to allow an I/O interruption to occur. The I/O interruption supervisor processes the I/O interruption and, if the I/O interruption signifies completion of an I/O request, returns the associated request element to the freelist. If, however, there is an error associated with the I/O request that is interrupted, the task that initiated the operation in error is abnormally terminated.

The EXCP supervisor uses the request element that is returned to the freelist to represent the I/O request. However, if no request element can be returned to the freelist, or if no I/O interruption occurs, the EXCP supervisor repeats the enable/disable loop.

The next available request element is loaded with the following information:

- Address of the UCB, which represents the I/O device to be used for the requested operations.

- TCB identification, as noted in the TCB for the task requesting I/O operations. (In an operating system in which option 4 is included, the address of the TCB is also placed into the request element.)

- Address of the IOB, which indicates the channel program to be executed.

- Dispatching priority of the request, as noted in the DEB. (If no priority is specified, this field is not significant.)

- Address of the DEB, which indicates the location of the data set to be operated upon.

If the request is related and there is a permanent error, as indicated by the IOB unrelated flag and the DCB permanent error code, the request cannot be executed. (An error has occurred on a previous related I/O request for the data set.) In this case, the abnormal end appendage exit is taken. For a normal return from the appendage, the request is posted complete with the purge code and the request element is returned to the freelist. Control returns to the task supervisor.

<u>UCB</u> <u>Condition</u> <u>Test:</u> The conditions associated with the I/O device that may prohibit immediate processing are denoted by the following bits contained in the UCB:

- Control unit busy.

- Device busy.

- Not ready.

- Disk arm seeking.

- Error routine in control.

If any of these bits are on, the request element is queued by an enqueue module for subsequent processing of the I/O request. If none are on, the device is available, is able to accept the request, and a test channel module is entered.

ERROR EXCP ROUTINE

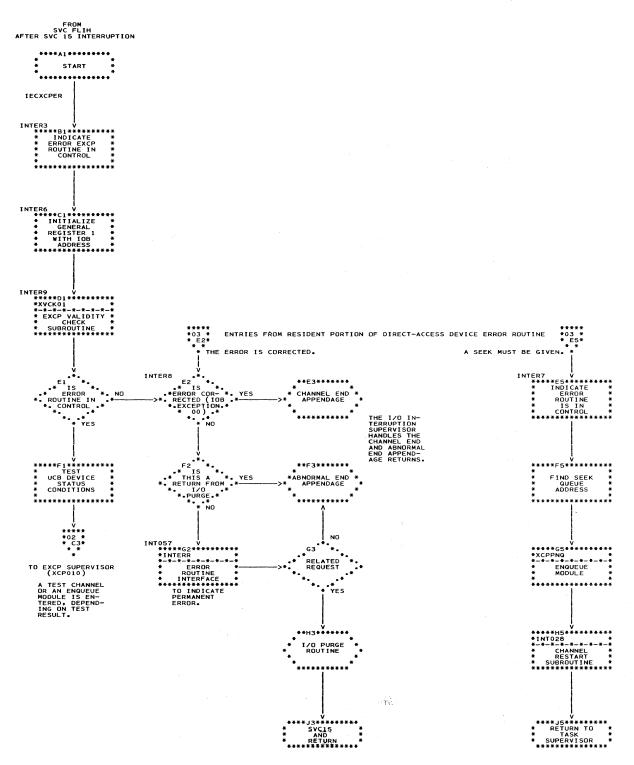

The error EXCP routine directs the retry of I/O requests (and the results of each retry) to the I/O supervisor. The routine is entered from the SVC FLIH after the SVC 15 interruption. Chart 03 shows the flow of control in the error EXCP routine.

SVC 15 is provided to simplify error recovery procedures with respect to request elements; an additional request element need not be issued by the get request element subroutine.

IBM-supplied error routines issue SVC 15 to retry channel programs because of an error, and also issue it when the error has been corrected, when another retry is necessary, and when the error is permanent. (See Part III: IBM-Supplied Error Routines.)

The I/O purge routine issues SVC 15 when it has purged all related requests and the abnormal end appendage must be entered. (See Part II: Error Routine Interface.)

The resident portion of the directaccess device error routine returns (it need not issue SVC 15) to the error EXCP routine: when an error is corrected; and when a request element must be queued in a seek queue for error recovery purposes. In the first case, the channel end appendage is entered; in the second, the channel restart subroutine of the I/O interruption supervisor is entered. The only parameter that the user of SVC 15 must furnish is the address of the request element that represents the I/O request that is to be retried. The request element contains the address of the IOB associated with the I/O request and is loaded into general register 1 for entry to the EXCP validity check subroutine.

The EXCP validity check subroutine checks the validity of the control blocks pertinent to the request and loads their addresses into general registers. The EXCP validity check subroutine then returns to the error EXCP routine; the IOB fields are not reset.

When an error routine is in control (the IOB error correction indicator flag is set) and the request must be retried, the error EXCP routine tests the following UCB condition flags:

- Device busy.

- Not ready.

- Disk arm seeking.

- Disk data transfer.

The EXCP supervisor determines the result of the test, and the request element is either enqueued or a test channel module is entered.

When the error has been corrected and the error routine is no longer in control, the channel end appendage is entered. If the error has not been corrected, the error routine interface of the I/O interruption supervisor is entered, which indicates a permanent error condition and enters either the I/O purge routine or the abnormal end appendage, depending on whether or not the request is related.

TEST CHANNEL MODULES

When the device necessary for the I/O request is available, a test channel module determines whether or not a physical channel in the device's logical channel is available for device operation. If a physical channel is not available, control passes to an enqueue module and the request element is queued.

There are two types of test channel modules: one for a selector channel; the other for a multiplexor channel. A selector channel test channel module exists for each logical channel in the system. One multiplexor channel test channel module exists for the logical channel associated with the multiplexor channel. <u>Module Selection:</u> The test channel module associated with the device and its logical channel is selected by means of the logical channel word indexing value, which is contained in the UCB, and the logical channel word table. The proper logical channel word contains the address of the test channel module for the device.

#### Selector Channel Test Channel Module

The selector channel test channel module issues a test channel (TCH) instruction for each physical channel attached to the requested device to determine whether or not a physical channel is available for that device. If an available channel is found, the select subroutine attempts to start the channel program for the I/O request. If one is not found, the request element is queued.

#### Multiplexor Channel Test Channel Module

Because a multiplexor channel never presents a busy condition to a TCH instruction, one is not issued and control immediately passes to the select subroutine, which attempts to start the I/O request. The multiplexor channel test channel module is included to facilitate channelindependent coding.

ENQUEUE AND DEQUEUE MODULES

If the channel program for an I/O request cannot be immediately started because a device or a physical channel is unavailable, the request element that represents the I/O request is queued. The queueing procedure used depends on the type of device and the type of enqueueing specified by the user at SYSGEN time.

The queueing procedures that are available are: FIFO, priority, and ordered. Logical channel queues are maintained in either FIFO or priority arrangements; seek queues are maintained in FIFO, priority, or ordered arrangements.

The dequeueing procedures depend on the type of enqueue module assigned to a device. The normal dequeue module is used for the dequeueing requirements of all queues maintained in FIFO and priority arrangements. The dequeue module for ordered seeks is used for seek queues maintained in an ordered arrangement. <u>Module Selection:</u> The address of the appropriate enqueue module is contained in the device table entry for the device class of the particular device. The proper entry in the table is found by use of the device table indexing value contained in the UCB that represents the device.

To determine the dequeue module to be used for a particular type of enqueueing, the enqueue module address that is contained in the device table is incremented by eight; at the resultant address is a branch to the dequeue module.

#### Normal Enqueue Module

The normal enqueue module queues request elements in a FIFO arrangement. The module is used for the enqueueing requirements of both logical channel queues and seek queues.

This module places the address of the request element that represents an I/O request into the link field of the last request element in the pertinent logical channel queue or seek queue. This request element becomes the "last" element in the queue and the dummy address is placed into its link field. The previous last request element is then updated to point at the new last request element.

#### Priority Enqueue Module

At SYSGEN time, the user specifies priority queueing for certain logical channel queues and seek queues. The request elements that represent the I/O requests are queued in an order that maintains the priority specified in the DEB for the pertinent task.

Priority queueing is effected by searching the logical channel or seek queue until the priority point at which the request element is to be queued is found. The address of the request element is placed into the link field of the next highest or equal priority request element in the queue. The highest priorities are at the top of the queue. Within a given priority, requests are in a FIFO arrangement.

#### Normal Dequeue Module

The normal dequeue module is used by the I/O supervisor to dequeue request elements

from queues maintained in FIFO and priority arrangements. A search is made of the queue until the request element to be dequeued is located. The element is unlinked and the queue is relinked by means of the 2-byte link field.

#### Ordered Seek Enqueue Module