## LOGICON 2+2 ASSEMBLER MANUAL

LOGICON INC.

1075 CAMINO DEL RIO, SOUTH

SAN DIEGO, CALIFORNIA

15 December 1970

#### TABLE OF CONTENTS

| Section |                                                                                                                                                                      | Page                                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|         | PREFACE                                                                                                                                                              |                                                          |

| I       | NUMBER SYSTEM                                                                                                                                                        | 1-1<br>1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2     |

| II      | INSTRUCTIONS                                                                                                                                                         | 2-1<br>2-1<br>2-1<br>2-5<br>2-5<br>2-5                   |

|         | E = Exponent Register                                                                                                                                                | 2-5<br>2-5<br>2-5<br>2-6<br>2-6                          |

|         | S = Status Register                                                                                                                                                  | 2-6<br>2-7<br>2-7<br>2-7<br>2-7<br>2-8                   |

|         | Address Interpretation  Assembly Language Programming.  Label Field.  Operation Field.  Variable Field.  Comments Field.  Field Separation.  Character Set  Symbols. | 2-8<br>2-8<br>2-9<br>2-9<br>2-10<br>2-10<br>2-10<br>2-10 |

| Section |                                                                                                                                                                                                           | Page                                                                                                                                     |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|         | Types of Symbols                                                                                                                                                                                          | 2-11<br>2-11<br>2-12<br>2-13                                                                                                             |

|         | DESCRIPTION OF MACHINE INSTRUCTIONS  Loads and Stores  LDX.  LDXEA.  LDXI  STX.  XXM  LDU.  LDU.  LDUI  STU  LDA.  LDAEA.  LDAEA.  LDAI  STA.  XAM  LDE.  LDEI  STE.  LDM  STM.  PUSHM.  POPM PUSHN  MSKM | 3-1<br>3-1<br>3-3<br>3-3<br>3-3<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4<br>3-4<br>3-5<br>3-5<br>3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8 |

|         | Input Output                                                                                                                                                                                              | 3-8<br>3-8                                                                                                                               |

|         | LDMAP  LLDB.  SIM SET.  DOUT.  DIN.                                                                                                                                                                       | 3-8<br>3-9<br>3-9<br>3-9<br>3-10                                                                                                         |

|         | SIL                                                                                                                                                                                                       | 3-10<br>3-10<br>3-11                                                                                                                     |

| Section |                     |                    |     | $\underline{\text{Page}}$ |

|---------|---------------------|--------------------|-----|---------------------------|

|         | SRTRN               |                    |     | 3-11                      |

|         | IRTRN               |                    |     |                           |

| •       | HLT                 |                    |     |                           |

|         | Character Instructi |                    |     | -                         |

|         | LDC                 |                    |     |                           |

|         | STC                 |                    |     |                           |

|         | CPRS                |                    |     |                           |

|         | GFC                 |                    |     | 3-14                      |

|         | GFCT                |                    |     | 3-14                      |

|         | GCI                 |                    |     | 3-15                      |

|         | GCIT                |                    |     |                           |

|         | IFC                 |                    |     | 3-16                      |

|         | IFCT                |                    | · · |                           |

|         | ICI                 |                    |     | 3-16                      |

|         | ICIT                |                    |     | 3-17                      |

|         | Privileged Instruct | ions               |     | 3-17                      |

|         | LDAOM               |                    |     | 3-18                      |

|         | STAOM               |                    |     | 3-18                      |

|         | TSLOM               |                    |     | 3-18                      |

|         | LDAOMF              |                    |     | 3-18                      |

|         | LDASM               |                    |     | 3-19                      |

|         | STASM               | • •, • • • • • • • |     | 3-19                      |

|         | LDXSM               |                    |     | 3-19                      |

|         | LDASMF              |                    |     | 3-19                      |

| ·       | MRGM                | • • • • • • • • •  |     | 3-19                      |

|         | POPN                |                    |     | 3-20                      |

|         | LDB                 |                    |     | 3-20                      |

|         | STB                 | • • • • • • • • •  |     | 3-21                      |

|         | LDSP                |                    |     | 3-21                      |

|         | LDBTL               |                    |     | 3-21                      |

|         | STSP                |                    |     | 3-21                      |

|         | STZ                 |                    |     | 3-22                      |

|         | LSABM               |                    |     | 3-22                      |

|         | SSABM               |                    |     | 3-22                      |

|         | MOVE                |                    |     |                           |

| •       | CLX                 |                    |     |                           |

|         | CLU                 |                    |     |                           |

|         | CLA                 |                    |     |                           |

| •       | CLF                 |                    |     | 3_23                      |

| Section |                             |           | Page |

|---------|-----------------------------|-----------|------|

|         | LDF                         |           | 3-23 |

|         | STF                         |           | 3-24 |

|         | LDD                         |           | 3-24 |

|         | LINK                        |           | 3-24 |

|         | DLINK                       |           | 3-25 |

|         | Inter-Register Instructions |           | 3-25 |

|         | RCPY                        |           | 3-25 |

|         | RNEG                        |           | 3-25 |

|         | RXCH                        |           | 3-25 |

|         | XSA                         |           | 3-26 |

|         | RDS                         |           | 3-26 |

|         | Fixed-Point Arithmetic      |           | 3-26 |

|         | ADX                         | • • • • • | 3-26 |

|         | ADXI                        |           | 3-26 |

|         | ADXIS                       |           | 3-27 |

|         | SBX                         |           | 3-27 |

|         | RSBX                        |           | 3-27 |

|         | MPX                         |           | 3-27 |

|         | ADU                         |           | 3-27 |

|         | ADUI                        |           | 3-27 |

|         | SBU                         |           | 3-28 |

|         | ADA                         |           | 3-28 |

|         | ADAI                        |           | 3-28 |

|         | SBA                         |           | 3-28 |

|         | RSBA                        |           | 3-28 |

|         | MPA                         |           | 3-28 |

| •       | DVUA                        |           | 3-29 |

|         | DVA                         |           | 3-29 |

|         | RDVA                        |           | 3-29 |

|         | RADD                        |           | 3-29 |

|         | RSUB                        |           | 3-30 |

|         | ADDM                        |           | 3-30 |

| •       | SUBM                        | • • • • • | 3-30 |

|         | MINC                        |           | 3-30 |

|         | MDEC                        |           | 3-31 |

|         | TAD                         |           | 3-31 |

| •       | NT AD                       |           | 3-32 |

|         | TSB                         |           | 3-32 |

|         | RTSB                        |           | 3-32 |

| Section |              |                          | Page   |

|---------|--------------|--------------------------|--------|

|         |              | TMP                      | 3-32   |

|         |              | TMPF                     | 3-33   |

|         |              | TDV                      | 3-33   |

|         |              | TDVF                     | 3-33   |

|         |              | ADAS                     | 3-33   |

| I .     |              | SBAS                     | 3-33   |

| :       |              | RSBAS                    | 3-34   |

|         |              | MPAS                     | 3-34   |

|         |              | DVAS                     | 3-34   |

|         |              | RDVAS                    | 3-35   |

|         |              | ADVS                     | 3-35   |

|         |              | SBUA                     | 3 - 35 |

| ٠       |              | DVUAS                    | 3-35   |

|         |              | ADXS                     | 3-36   |

|         |              | SBXS                     | 3-36   |

|         |              | RSBXS                    | 3-36   |

|         |              | MPXS                     | 3-36   |

|         |              | TADS                     | 3-37   |

|         |              | NT ADS                   | 3-37   |

|         |              | TSBS                     | 3-37   |

|         |              | RTSBS                    | 3-38   |

|         |              | TMPS                     | 3-38   |

|         |              | TMPFS                    | 3-38   |

| •       |              | TDVS                     | 3-39   |

|         |              | TDVFS                    | 3-39   |

|         |              | TNEG                     | 3-40   |

|         | $\mathbf{F}$ | loating Point Arithmetic | 3-40   |

| •       |              | FAD                      | 3-40   |

|         |              | NF AD                    | 3-40   |

|         |              | FSB                      | 3-40   |

|         |              | RFSB                     | 3-41   |

|         |              | FMP                      | 3-41   |

|         |              | FDV                      | 3-41   |

|         |              | RFDV                     | 3-41   |

|         |              | FADS                     | 3-41   |

|         |              | NFADS                    | 3-42   |

|         |              | FSBS                     | 3-42   |

|         |              | RFSBS                    | 3-42   |

|         |              | FMPS                     | 3-43   |

| Section |                      | Page |

|---------|----------------------|------|

|         | FDVS                 | 3-43 |

|         | RFDVS                | 3-43 |

|         | FIX                  | 3-43 |

|         | FLOAT                | 3-44 |

|         | NORM                 | 3-44 |

|         | FNEG                 | 3-44 |

|         | Logical Instructions | 3-44 |

|         | ANX                  | 3-45 |

|         | ANU                  | 3-45 |

|         | ANUI                 | 3-45 |

|         | ANUA                 | 3-45 |

|         | ANA                  | 3-45 |

|         | ANAI                 | 3-45 |

|         | ORA                  | 3-46 |

| •       | ORAI                 | 3-46 |

|         | XRA                  | 3-46 |

|         | XRAI                 | 3-46 |

|         | RAND                 | 3-46 |

|         | SETBA                | 3-47 |

|         | CLRBA                | 3-47 |

|         | CMPBA                | 3-48 |

|         | SETBM                | 3-48 |

|         | CLRBM                | 3-48 |

|         | CMPBM                | 3-49 |

|         | ANAS                 | 3-49 |

|         | OR AS                | 3-50 |

|         | XRAS                 | 3-50 |

|         | ANXS                 | 3-50 |

|         | Shift Instructions   | 3-51 |

|         | LLX/LRX              | 3-51 |

|         | ALU/ARU              | 3-51 |

|         | LLU/LRU              | 3-51 |

|         | RLU/RRU              | 3-52 |

|         | ALA/ARA              | 3-52 |

|         | LLA/LRA              | 3-52 |

|         | RLA/RRA              | 3-52 |

|         | LLUAE/LRUAE          | 3-53 |

|         | ALUA/ARUA            | 3-53 |

|         | LLUA/LRUA            | 3-53 |

| Section |                    | Page   |

|---------|--------------------|--------|

|         | RLUA/RRUA          | . 3-54 |

|         | LLO                | . 3-54 |

|         | Compares and Tests | . 3-54 |

|         | SKXEI              | . 3-54 |

|         | SKXNI              | . 3-55 |

|         | SKAE               | . 3-55 |

|         | SKAN               | . 3-55 |

|         | SKAEI              | . 3-55 |

|         | SKANI              | . 3-56 |

|         | ACX                | . 3-56 |

|         | ACU                | 3-56   |

|         | ACA                | 3-57   |

|         | ACE                | 3-57   |

|         | FCP                | 3-57   |

|         | FCPS               | . 3-58 |

|         | LCX                | 3-58   |

|         | LCU                | 3-58   |

|         | LCA                | 3-59   |

|         | LCE                | 3-59   |

|         | MSK                | 3-59   |

|         | SKZA               |        |

|         | SKOA               | 3-60   |

|         | SKZM               | 3-61   |

|         | SKOM               |        |

|         | SKNOF              |        |

|         | SKNCO              |        |

|         | TSL                | 3-62   |

|         | DSK                |        |

|         | Jumps              |        |

|         | JMP                |        |

|         | JZE                |        |

|         | JNZ                |        |

|         | JPL                |        |

|         | JMI                |        |

|         | XJP                |        |

|         | UJP                |        |

|         | AJP                |        |

|         | EJP                |        |

|         | TIP                | . 3-65 |

| Section |                                                                                                                                                                                                                                                                                                 | Page                                                                                                                |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|         | IJXN                                                                                                                                                                                                                                                                                            | 3-66<br>3-66<br>3-66<br>3-66                                                                                        |

|         | JSPX JSPM CALL RTRN SCALL IJSPX IJSPM                                                                                                                                                                                                                                                           | 3-66<br>3-67<br>3-67<br>3-67<br>3-68<br>3-69                                                                        |

|         | ICALL                                                                                                                                                                                                                                                                                           | 3 <b>-</b> 69                                                                                                       |

| IV      | PSEUDO OPERATIONS  General  Control Pseudo Operations.  RADIX 8  RADIX 10  END.  Program Linking Pseudo Operations  ENTRY.  BENTRY.  Storage Allocation Pseudo Operations  BSS  BES  Symbol Defining Pseudo Operations  EQU.  SET  Data Generating Pseudo Operations  PAR.  BPAR.  BPAR.  DATA. | 4-1<br>4-1<br>4-1<br>4-1<br>4-1<br>4-3<br>4-3<br>4-3<br>4-3<br>4-3<br>4-3<br>4-4<br>4-4<br>4-5<br>4-5<br>4-5<br>4-5 |

|         | STR                                                                                                                                                                                                                                                                                             | 4-6<br>4-6<br>4-7<br>4-10<br>4-11                                                                                   |

|         | MACRO, LMACRO, and ENDM                                                                                                                                                                                                                                                                         | 4-19                                                                                                                |

| Section |                                            | Page         |

|---------|--------------------------------------------|--------------|

|         | Carrie Date than Caller D. Carte an        | 4 10         |

|         | Some Details of the Definition             | 4-19         |

|         | Dummy Arguments                            | 4-20         |

|         | Generated Symbols                          | 4-22         |

|         | Concatenation                              | 4-23         |

|         | Conversion of a Value to a Digit String    | 4-23         |

|         | A Note on Subscripts                       | 4-24         |

|         | NARG and NCHR                              | 4-24         |

|         | Macro Calls                                | 4-25         |

|         | Example of Conditional Assembly and Macros | 4-27         |

|         |                                            |              |

| V       | ASSEMBLER OPERATING INSTRUCTIONS           | 5 - 1        |

|         | Instructions                               | 5 <b>-</b> 1 |

|         | Examples                                   | 5-3          |

| VI      | LSIM LOADING, SIMULATING, AND DEBUGGING    | 6-1          |

|         | General                                    | 6-1          |

|         | Symbols                                    | 6-1          |

|         | Constants                                  | 6-1          |

|         | Expressions                                | 6-1          |

|         | Open Registers or Memory Cells             | 6-2          |

|         | Commands                                   | 6-3          |

|         |                                            | 6-6          |

|         | Error Messages                             | 6-7          |

|         | Using LSIM on Tymshare                     | 6-7          |

|         | Calling LSIM                               |              |

|         | Programming Considerations                 | 6-8          |

|         | Escapes                                    | 6-8          |

|         | Multiple Processing                        | 6-8          |

|         | Modes                                      | 6-8          |

|         | Mode Commands                              | 6-9          |

|         | Programming Considerations                 | 6-9          |

| Section |                                           | Page  |

|---------|-------------------------------------------|-------|

| APP. A  | LOGICON 2+2 CHARACTER SET                 | A - 1 |

| APP. B  | LOGICON 2+2 MNEMONICS IN                  |       |

|         | ALPHABETICAL ORDER                        | B - 1 |

| APP. C  | LOGICON 2+2 MNEMONICS BY FORMAT           | C-1   |

| APP. D  | LOGICON 2+2 MNEMONICS BY REGISTER         | D-1   |

| APP. E  | LOGICON 2+2 MNEMONICS BY FUNCTION         | E-1   |

|         |                                           |       |

|         |                                           |       |

|         | LIST OF ILLUSTRATIONS                     |       |

| Figure  |                                           | Page  |

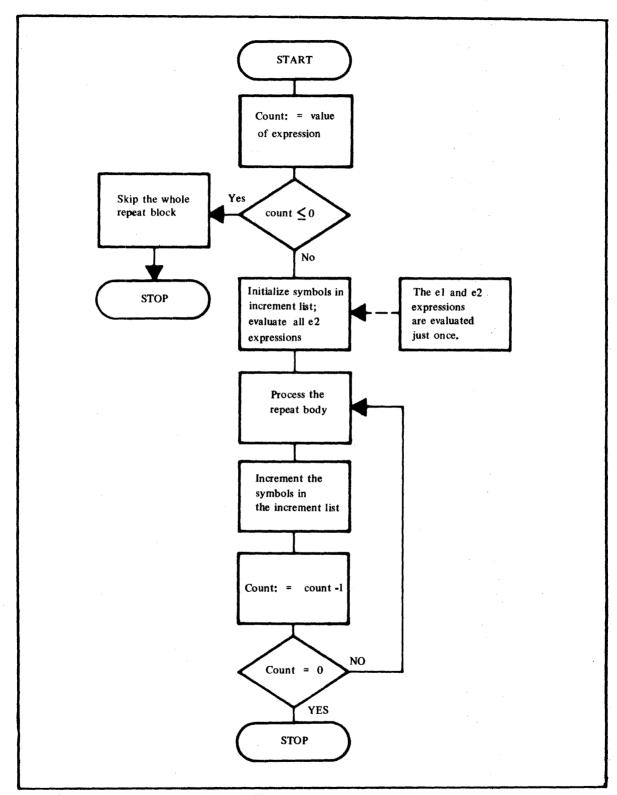

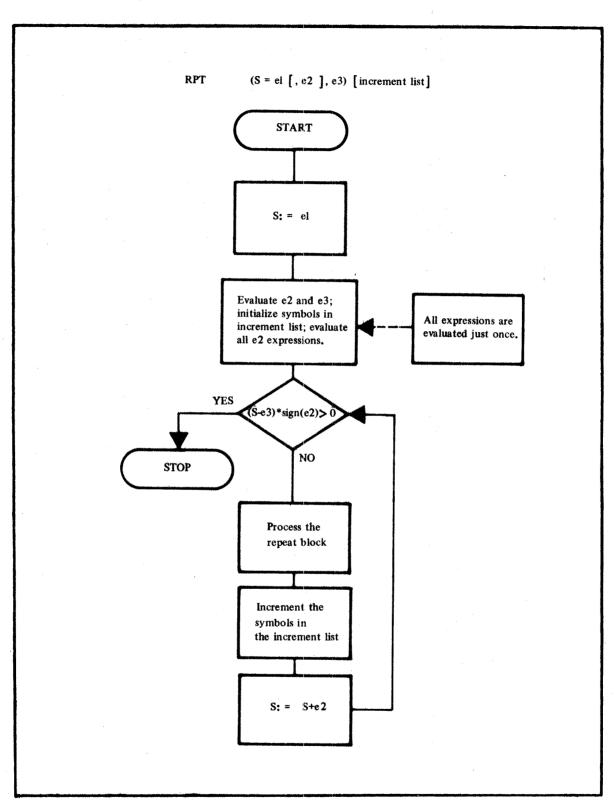

| 4-1     | RPT Repeat Options, Flow Chart            | 4-12  |

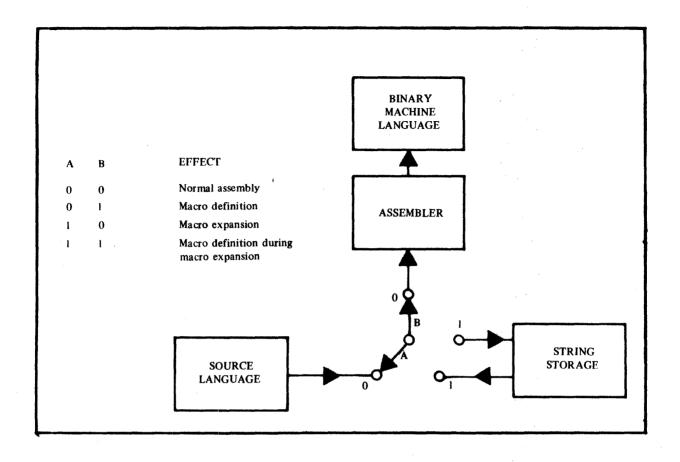

| 4-2     | Information Flow During Macro Processing  | 4-16  |

|         |                                           |       |

|         | LIST OF TABLES                            |       |

| Table   |                                           | Page  |

| 2-1     | Instruction Formats                       | 2-2   |

| 3-1     | Address Modifiers for Basic Instruction   |       |

|         | Formats 1A, B, C, D                       | 3-2   |

| 3-2     | Conditions for all Skip/Jump Instructions | 3-31  |

| 3 - 3   | Definitions of Boolean Operations         | 3-44  |

| 3-4     | Simulated System Calls                    | 3-70  |

| 4-1     | Initial Set of Offered Pseudo Operations  | 4-2   |

#### Preface

This Assembler Manual is the basic document for programming on the LOGICON 2+2 System. Essentially, it describes programming-related machine features, the instruction repertoire, and the symbolic machine-language-oriented Macro assembler. This manual is only one of a set of publications for programming the LOGICON 2+2. The user should contact his LOGICON representative for others of the set to obtain all the pertinent and necessary programming information.

This document is addressed to programmers experienced with coding in the environment of a computer installation. It assumes knowledge and experience in the use of address modification with indirection, and other features normally encountered in a computer with a very flexible instruction repertoire -- under control of a master monitor program. It is also assumed that the programmer is familiar with the 2's complement number system as used in a sign-number machine. Note that some of the examples given use SDS-940 instructions. These were taken from the SDS-940 NARP manual as it was felt they would be helpful to the programmer unfamiliar with these features.

It is intended that this manual be updated and added to frequently in order to properly reflect errors, changes, and the required additions leading to the final LOGICON 2+2 system.

### Number System

#### GENERAL

The binary system of notation is used throughout the LOGICON 2+2 system.

In the "arithmetic" case of addition, subtraction, and comparison, operands and results are considered as binary numbers in 2's complement form. Subtraction, for example, is carried out internally by adding the 2's complement of the subtrahend.

The assumed location of the binary point has significance only for multiplication and division. For integer arithmetic, the binary point may be assumed to the right of the least-significant bit position (i.e., to the right of bit position 15); and for fractional arithmetic, the position of the binary point may be assumed to the left of the most-significant position (i.e., between bit positions 0 and 1).

#### REPRESENTATION OF INFORMATION

The processor is fundamentally organized to deal with 16-bit grouping of information. Special features are also included for ease of manipulating bits, bytes, and multiple words as groups.

These bit groupings are used by the hardware and software to represent a variety of forms of information.

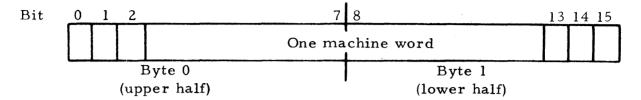

#### MACHINE WORD

The machine word consists of 16 bits. The numbering of bit position, character positions, words, etc. increases in the direction of conventional reading from the most-to least-significant.

Data transfers between processor and memory are bit, byte, and word oriented as illustrated below.

#### ALPHANUMERIC DATA

Alphanumeric data are represented by 8-bit bytes. One machine word contains 2 bytes or characters. The character set used is standard ASCII. Note, however, that for teletype use and access, the 64 character subset indicated in Appendix A is all that is allowed within the assembler.

#### ONE WORD BINARY INTEGERS

For the "algebraic" group of instructions, results are regarded as signed binary numbers, the leftmost bit being used as a sign bit (a 0 being plus and 1 minus). When the sign is positive all the bits represent the absolute value of the number; and when the sign is negative, they represent the 2's complement of the absolute value of the number. Overflow occurs when the magnitude of a number does not fit within a given word or register. That is, if the carryout of the sign position does not agree with the resultant sign (bit position), overflow has occurred. There are no conditions for underflow. A signed integer ranges from -2<sup>15</sup> through 2<sup>15</sup> - 1.

For the "logical" group of instructions, results are regarded as unsigned, positive binary numbers in the range of 0 through  $2^{16} - 1$ .

#### THREE WORD BINARY INTEGERS

The three word integers are sign magnitude, the left most bit of the first word is sign followed by 47 bits of magnitude. The range of three-word extended integers is from  $-(2^{47} - 1)$  through  $2^{47} - 1 = 140$ , 737, 488, 355, 327. Overflow occurs when the magnitude of a number does not fit within the 47 bits.

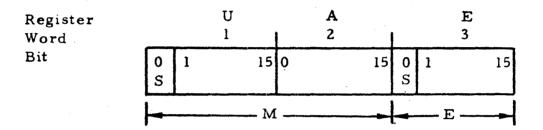

#### THREE WORD BINARY FLOATING-POINT NUMBERS

The instruction set contains instructions for binary floating-point arithmetic with numbers of two-word precision. The lower word

represents the integral exponent E in 2's complement form, and the upper two words (32 bits) represent the fractional mantissa M in sign magnitude form. The notation for a floating-point number N is:

$$N = M \times 2^{E}$$

The three word format is shown below. S represents the sign bit.

Any number with an absolute value in the range of .353 x  $10^{-9864}$  through .708 x  $10^{9864}$  can be represented to more than nine significant decimal digits. For normalized floating-point numbers, the binary point is placed at the left of the most significant bit of the mantissa. Numbers are normalized by shifting the mantissa (and adjusting the exponent) until no leading zeros are present in the mantissa.

To maintain accuracy, the lowest possible exponent (-32768) together with a zero mantissa has been defined as the machine representation of the number zero.

#### FOUR WORD BINARY FLOATING POINT NUMBERS

These numbers are similar to the 3 word floating point with the exception of one more word of precision. This permits a number with an absolute value in the range of .353 x  $10^{-9864}$  through .708 x  $10^{9864}$  to be represented to more than 14 significant decimal digits.

|  |   |  | • |  |

|--|---|--|---|--|

|  | ÷ |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

|  |   |  |   |  |

#### II ...

#### Instructions

#### GENERAL

Machine instructions are comprised of 10 different format types. In addition, some of these formats may be subdivided into one or more sub-formats. Functionally, the formats are divided as follows:

- l. Basic instructions.

- 2. Miscellaneous instructions.

- 3. System Calls.

- 4. Multi-register and register bit instructions.

- 5. Memory bit instructions.

- 6. Two-word general instructions.

- 7. Register operation instructions.

- 8. Single register shift instructions.

- 9. Double register shift instructions.

- 10. Immediate data instructions.

#### FORMATS

The specific formats (1 thru 10) are shown in Table 2-1, Instruction Formats.

TABLE 2-1. INSTRUCTION FORMATS

| NUMBER     | TYPE                                  | FORMAT                          |

|------------|---------------------------------------|---------------------------------|

| 1A         | BASIC:                                | OP (<25D) I X R DISP            |

| 1B         | IMMEDIATE FORM<br>OF BASIC            | OP (<25D) 0 0 1 0 0 0 0 0 0 1   |

| 10         | TWO-WORD FORM OF<br>BASIC, WITHOUT B: | OP (< 25D) 1 X 1 0 0 0 0 0 0 1  |

| 1D         | TWO-WORD FORM OF<br>BASIC, WITH B:    | 1 1 0 0 1 0 0 0 OP (<25D) 0 X 0 |

| 2          | MISCELLANEOUS:                        | 1 1 0 0 1 0 0 1 MOD OP          |

| 2В         | MISCELLANEOUS:                        | 1 1 0 0 1 0 0 1 MOD OP          |

| 3          | SYSTEM CALL:                          | 1 1 0 0 1 0 1 0 CALL NO.        |

| <b>4</b> A | MULTI-REG. INST :                     | 1 1 0 0 1 0 1 1 OP 0 XSUSASES   |

| 4B         | REG. BIT INST.:                       | 1 1 0 0 1 0 1 1 OP N BIT NO.    |

| 5          | MEMORY BIT<br>INSTRUCTION:            | 1 1 0 0 1 1 X B OP N BIT NO.    |

| 6A         | NORMAL TWO-WORD:                      | 1 1 0 1 0 B X MOD OP  I ADDRESS |

TABLE 2-1. INSTRUCTION FORMATS (Cont)

| NUMBER     | ТҮРЕ                               | FORMAT                                     |

|------------|------------------------------------|--------------------------------------------|

| 6B         | TWO-WORD, DIRECT<br>BYTE ADDRESS:  | 1 1 0 1 0 B X 0 MOD OP  BYTE ADDRESS       |

| 6C         | TWO-WORD, INDIRECT<br>BYTE ADDRESS | 1 1 0 1 0 B X 1 MOD OP    X   WORD ADDRESS |

| 6D         | MULTIPLE LOAD AND STORE:           | 1 1 0 1 0 B X XSUSAS ES OP  ADDRESS        |

| <b>6</b> E | "SPECIFIED MAP" INSTRUCTIONS:      | 1 1 0 1 0 B X MOD OP  M ADDRESS            |

| 6F         | "OTHER MEMORY" INSTRUCTIONS:       | 1 1 0 1 0 B X I MOD OP  ADDRESS            |

| <b>6</b> G | TWO-WORD IMMEDIATE:                | 1 1 0 1 1 0 0 MOD OP                       |

| 7A         | OPERATE (EXC. RNEG):               | 1 1 0 1 1 0 1 SOURCE DEST. OP              |

| 7B         | RNEG:                              | 1 1 0 1 1 0 1 SOURCE 1 1 1 DEST.           |

| 8          | ONE-REG. SHIFT:                    | 1 1 0 1 1 1 0 X OP COUNT                   |

| 9          | TWO-REG. SHIFT:                    | 1 1 0 1 1 1 1 X OP COUNT                   |

| 10         | IMMEDIATE                          | 1 1 1 OP DATA                              |

The symbols used in Table 2-1 refer to fields of the different instruction formats, where:

| OP | = | the operation code, | can occur | as | a |

|----|---|---------------------|-----------|----|---|

|    |   | 2- to 8-bit field.  |           |    |   |

I = indirect bit, indicating indirect addressing.

X = indexing according to contents of X register.

R = relative addressing with respect to the P counter and the DISP field (i.e., P + DISP or P +D).

DISP = displacement address (D).

DATA = 9-bit (Sign Extended) or 16-bit (full word) data field.

ADDRESS = 15-bit word address (<32768).

16 bits in case of 6B.

CALL NO. = specified System Call number.

X<sub>S</sub> = X-register select.

U<sub>S</sub> = U-register select.

A<sub>S</sub> = A-register select.

$E_{S}$  = E-register select.

BIT NO. = bit number referenced in register bit instruction.

N = bit number; indexing by low order 4 bits of X-register.

B = relative addressing with respect to B-register.

BYTEADDRESS = 16-bit byte address (<65536).

M = specifies user or system map.

Source = code indicates source register selected

(i.e., X, U, A, etc.)

Destination = code indicates destination register

selected (i.e., X, U, A, etc.)

Count = shift count. (Left shift >0. Right shift 0.)

#### ABBREVIATIONS AND SYMBOLS

The following abbreviations and symbols are used for description of the machine operation. All registers are 16 bits long, although quantities contained within some of the registers may be less than 16 bits long.

#### A = Accumulator register

The primary accumulator in the machine. Arithmetic, logical and shift operations are performed directly on this register. It may also be linked with U to form a 32-bit accumulator. A is the low order half of this two-word accumulator.

#### U = Upper Accumulator register

Some arithmetic, logical, and shift operations are performed directly on the register. In other cases, it is linked with the A register to form a 32-bit accumulator. In these cases, U is the high order half of the two-word accumulator.

#### E = Exponent register

Contains the exponent in floating point operations. The exponent is expressed as a 2's complement number. This register can be loaded from memory or other registers. It has very limited arithmetic and logical capabilities.

#### X = Index register

Indexing may be 15-bit word addresses, 16-bit byte addresses, or 16-bit 2's complement displacements. Arithmetic operations on this register do not affect the overflow or carryout status indicators.

#### P = Program Counter register

This register generally contains the address of the next instruction to be executed. In forming relative addresses in basic instructions it contains the address of the current instruction. The register is 16 bits long but the addresses it contains are all 15-bit quantities.

#### B = Base of stack register

This register contains the 15-bit address of the base of the stack as seen by the main program or subroutine currently running. Attempts to "pop" the stack beyond this address will result in a stack underflow trap. If the high order bit is set, erroneous results and tests on B may result.

#### T = Top of stack register

This register contains the 15-bit address of the next word to be pushed into the stack. This address should not be less than the address contained in B nor greater than that contained in L as the result of a stack operation. Checks are made before the stack operation. Note that checks are made only in the appropriate direction (i.e., check for overflow on a "push", and underflow on a "pop").

#### L = Limit of stack space register

This register contains the 15-bit address of the first word beyond the stack (i.e., the address of the first word the stack is not allowed to occupy). An attempt to "push" the stack beyond this address results in a stack overflow trap.

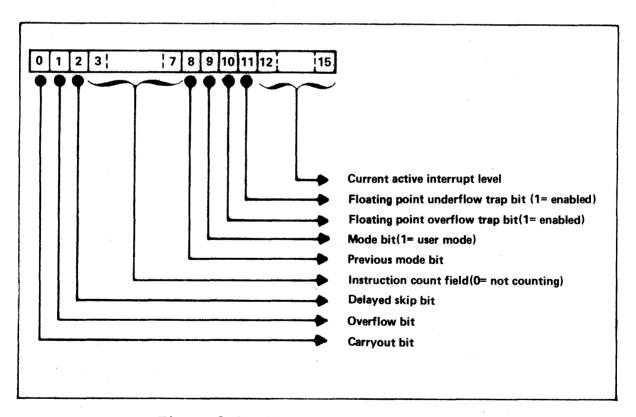

#### S = Status register

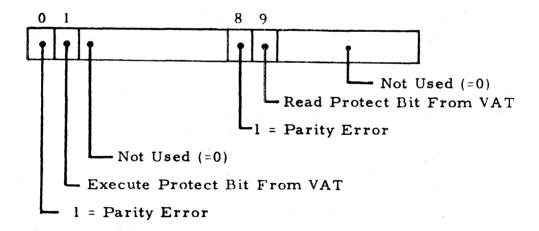

Bits in this register describe the current status of the machine. Bit positions within the word are defined in Figure 2-1, Status Word Contents.

Figure 2-1. Status Word Contents.

Mode - The current mode of the machine.

0 = system mode

1 = user mode.

Previous mode - Defined only if the mode is system.

0 = system mode

1 = user mode.

#### CO = Carryout

Describes the result of the previous arithmetic instruction.

0 = no carryout occurred

1 = carryout occurred

This bit can be set to either state as a result of an arithmetic operation.

#### OF = Overflow

Describes the result of all arithmetic and shift instructions on U and A (except register-register instructions) executed since the indicator was last reset.

0 = no overflow has occurred

1 = at least one overflow has occurred.

#### Floating point Overflow Trap

Indicates whether floating point overflow will result in a trap, or be ignored.

0 = ignored

1 = trap.

#### Floating point Underflow Trap

Indicates whether floating point underflow will result in a trap, or be ignored.

0 = ignored

1 = trap.

#### Notation

= effective address of instruction У U. A. E. X. B. T. L = respective registers (Y) = contents of effective address Y YR = effective address of byte Y = bit position i of A register = replaces = AND= OR= Exclusive OR [LC] = Logical compare [AC] = Arithmetic compare

#### ADDRESS INTERPRETATION

Instructions are translated in a number of ways. The manner of interpretation is governed by the type of instruction. In general, there are the following types of addresses:

- An instruction address, which is the address used for fetching instructions.

- A tentative address, which is the address used for fetching an indirect word.

- An effective address, which is the final address produced by the address modification process. It is the address used for obtaining an operand, for storing a result, or for other special operations during which memory is accessed using the effective address.

#### ASSEMBLY LANGUAGE PROGRAMMING

The normal operating mode of the LOGICON 2+2 assembler in processing input subprograms is relocatable; that is, each subprogram is handled individually and is assigned memory locations nominally beginning with zero and extending to the upper limit required for that subprogram. Since a job stream can contain many such subprograms, it is apparent that they cannot all be loaded into memory area starting with location zero; they must be loaded into different areas.

Furthermore, they must be movable (relocatable) among the areas. Then for relocatable subprograms, the LOGICON 2+2 assembler provides:

- Delineators identifying each subprogram.

- Symbol linking information.

- Length of each subprogram.

- Relocation control bits for each assembled word.

#### Label Field

In machine instructions, certain pseudo-operations, and macros, this location may contain a symbol (1 to 6 characters) or may be left blank if no reference is made to the instruction.

#### Operation Field

The operation field may contain from one to six characters. The group of characters must be a LOGICON 2+2 operation code or pseudo-operation, or a programmer defined macro operation code. Anything else appearing in the operation field is illegal and results in an error message.

An asterisk (\*), appearing immediately following the operation code, is a special modifier indicating indirect addressing.

#### Variable Field

The variable field contains zero, or more subfields separated by the programmer through the use of commas placed between subfields. The number and type of subfields vary depending upon the content of the operation field, machine instruction, pseudo-op, or macro operation.

The subfields within the variable field of machine instructions consist of the address and address modifiers. The address may be any legitimate expression. This is usually the first subfield of the variable field and is separated from modifiers by a comma. Through address modification as directed by the modifier, a program address is defined.

The subfields used with pseudo-operations vary considerably; they are described individually under each pseudo-operation. Subfields used with macro operations are substitutable arguments which, in themselves, may be pseudo-operations, or other macro operations. All of these types of subfields are presented in the discussion on macro operations.

The end of the variable fields is designated by the first blank, semicolon, carriage return, or end-of-file encountered in the variable field.

Any null subfield is interpreted to be zero.

#### Comments Field

The comments field exists solely for the convenience of the programmer; it plays no part in the assembly process. Programmer comments normally follow the variable field and are separated from that field by at least one blank column or by a semicolon.

A comment may be introduced in several ways:

- An asterisk (\*) in column 1.

- A semicolon (;) in any column position.

- By detecting the end of the variable field.

#### Field Separation

Fields are separated by one or more blanks.

#### Character Set

All the characters listed in Appendix A have meaning except for '?'. The following classification of character set is useful.

letter: A-Z

octal digit: 0-7

digit: 0-9

alphanumeric character: letter or digit

terminator: , ; blank CR (denotes carriage

return)

operator: ! # % & \* + - / <=> @ 1

delimiter: "\$ '()[].-

#### Symbols

Any string of alphanumeric characters beginning with an alphabetic character is a symbol, but only the first six characters distinguish the symbol (thus, Q12345 is the same symbol as Q123456).

#### Types of Symbols

Symbols are classified as the following types:

- Absolute if a symbol refers to a specific number.

- Relocatable if a symbol appears in the label field of an instruction.

- External if a symbol is considered to be defined external to the subprogram being assembled, and is, furthermore, considered specially by the loader.

#### Symbol Definitions

Due to the way in which programs are assembled on the Tymshare version of the LOGICON 2+2 assembler, the statement that a symbol or expression is "defined" usually means that it is defined at that instant and not somewhere later in the program. Thus, assuming ALPHA is defined nowhere else, the following

BETA EQU ALPHA ALPHA BSS 3

is an error because the EQU pseudo-op demands a defined operand and ALPHA is not defined until the next statement. This convention is not strictly adhered to, however, since sometimes the statement XYZ is not defined will mean that XYZ is defined nowhere in the program.

A symbol is defined in one of two ways: by appearing as a label or by being assigned a value with an EQU pseudo-op (or equivalently, by being assigned a value by NARG, NCHR).

- Labels: If a symbol appears in the label field of an instruction (or in the label field of some pseudo-ops) then it is defined with the current value of the current location counter. If the symbol is already defined, either as a label or as an equated symbol, the re-defined error message is typed and the old definition is completely replaced by the new one.

- Equated symbols: These symbols are usually defined by EQU or SET, getting the value of the expression in the operand field of the pseudo-op. This expression must be defined. If the symbol has been previously defined as a label, then the "redefined" error message is typed and the old definition is completely replaced by the new one; if the symbol has already been defined as an equated symbol, then no error message is given, and the old value is replaced by

the new one. Thus, an equated symbol can be defined over and over again, getting a new value each time.

Note that both the SET and EQU pseudo-ops are processed by the EQU pseudo-op when using the Tymshare version of the LOGICON 2+2 assembler. In the final version, both pseudo-ops will be implemented. SET should be used when "redefinition" is desired. The reader should choose the pseudo-op appropriately.

A defined symbol is always local, and may also be external. If a symbol in routine A is to be referred to from routine B, it must be declared external in routine A. This is done in one of the following ways:

Declared external by \$: If a label or equated symbol is preceded by a \$ when it is defined, then it is declared external.

| \$LABEL1 | LDA | ALPHA           |                      |

|----------|-----|-----------------|----------------------|

| LABEL 2  | STA | $\mathtt{BETA}$ | LABEL2 IS LOCAL ONLY |

| \$GAMMA  | EQU | DELTA           |                      |

Declared external by the ENTRY pseudo-op: The symbol in the label field is declared external; it may have already been declared external or may even have a \$ preceding it.

If a given symbol is referred to in a program, but is not defined when the END directive is encountered, then it is assumed that this symbol is defined as external in some other package. Whether this is the case cannot be determined until the various packages have been loaded. Such symbols are called "undefined symbols" or "external symbol references." It is possible to perform arithmetic upon them (e.g., LDA UNDEF+1); an expression in post-fix Polish form will be transmitted to the loader.

#### Expressions

Loosely speaking, an expression is a sequence of constants and symbols connected by operators. Examples:

```

100-2*ABC/(ALPHA+BETA)

GAMMA

F>=Q

```

The value of an expression is obtained by applying the operators to the values of the constants and symbols, evaluating from left to right except when this order is interrupted by the precedence of the operators or by parenthesis "(,)"; the result is interpreted as a 16-bit signed integer. The following table describes the various operators and lists

their precedences (the higher the precedence, the tighter the operator binds its operands):

| Operator      | Precedence | Comment                              |                  |  |

|---------------|------------|--------------------------------------|------------------|--|

| <b>†</b>      | 6          | exponentiation; exponent must be ≥0. |                  |  |

| *             | 5          | multiplication                       |                  |  |

| /             | 5          | integer division                     |                  |  |

| +(u)          | 4          | u <b>nary pl</b> us                  |                  |  |

| - (u)         | 4          | negation (arithmetic)                |                  |  |

| +             | 4          | addition                             |                  |  |

| -             | 4          | subtraction                          |                  |  |

| <             | 3          | less than                            |                  |  |

| <b>&lt;</b> = | 3          | less than or equal to                | result of opera- |  |

| =             | 3          | equal to                             | tion is 0 if re- |  |

| #             | 3          | not equal to                         | lation is false, |  |

| >==           | . 3        | greater than or equal to             | otherwise l      |  |

| >             | 3          | greater than                         | <b>)</b>         |  |

| @ (u)         | 2.         | logical not                          |                  |  |

| &z            | 1          | logical and                          | logical opera-   |  |

| !             | 0          | logical or                           | tion applied to  |  |

| %             | 0          | logical exclusive or                 | all 16 bits      |  |

If an expression contains an illegal or undefined symbol, then the entire expression is undefined.

#### Symbolic Operation Coding and Modifiers

There are several symbolic syntactical elements. They are defined as follows:

| \$      | A label preceded by a dollar sign is declared external.                                              |

|---------|------------------------------------------------------------------------------------------------------|

| Label   | The label is defined with the current value of the location counter.                                 |

| Opcode  | The opcode must be an instruction, pseudo-<br>operation, or macro operation already defined.         |

| *       | If an asterisk follows immediately after the opcode then the indirect bit of the instruction is set. |

| Operand | The operand can be an expression which may or may not be defined.                                    |

Modifiers

The modifiers affect address translation. There are several such characters, and their effect or use is governed by the particular operation code appearing in the operation code field. The symbols allowed are the following:

\*

The asterisk is a multi-functional element. It is used as the multiplication operator, designates a comment line, and also indicates indirect addressing. In addition to the above interpretations, it may be used to refer to the location of the instruction in which it appears; for example,

A10 JMP \*+2

is equivalent to

A10 JMP A10+2

and represents a jump to the second location following the jump instruction. Note, however, that because of the complexity of implementing the LOGICON 2+2 assembler on Tymshare, this element may appear only as the first character of an expression. Thus,

A10 JMP \*+2

is legal, but

A10 JMP 2+\*

is not.

P

the displacement field (D) is computed relative to the P counter (P + D).

LDA A (effective address is P + D)

is equivalent to

LDA A, P (effective address is P + D)

The presence of the P modifier forces relative to P counter addressing.

В

the displacement field (D) is computed relative to the contents of the B register (B + D) where D = A-P. Thus,

LDA A, B

results in the effective address, B + D.

$\mathbf{X}$

the contents of the index register is added to the computed address to complete address translation. Thus,

#### LDA A, XP results in P + D + X

=

signifies an effective address. If the variable following the equals sign is a literal (i.e., constant), the literal itself is generated as the second word of the instruction. If the variable is a label, the address of the label is generated as the second word of the instruction. The = sign only applies to 1B and 6G formats.

F.

is used to indicate an extended or two-word expansion for certain instructions. This is necessary, in many instances due to limitations imposed by the 8-bit displacement field. This field allows direct addressing of locations only within the range of the P counter -  $128 \le D \le 127$ .

When it is necessary to access a memory location outside of this range, two word formats are necessary to accommodate full 15-bit word and/or 16-bit byte addresses.

For example,

#### LDA A, E

generates (P + 1) as an address -- which means the contents of the second location is used as the effective address for the instruction. The programmer uses the "E" to indicate to the assembler the address A is not in range of the current instruction.

Bit

No.

an absolute expression used to select a particular bit involved in a memory- or register-bit type instruction. The bit number is a 4-bit field and may be modified (computed modulo 16).

N

modifier symbol used in memory- and registerbit instruction to indicate that the low order 4 bits of the X register are to be added to the bit number field. Selected Registers

X, U, A, E

Instructions involving multiple registers or multiple loads and stores, the symbols X, U, A, and E are placed in the variable field to indicate the registers involved in loads, stores, pushes, and pops. The symbols X, U, A, and E represent the X, U, A, and E registers respectively.

# III... Description of Machine Instructions

#### **GENERAL**

In describing each instruction, five items may appear underlined preceding the instruction summary. The items are:

Mnemonic Name OpCode (Mod) Format

LOADS AND STORES

LDX Load X 00 1A, B, C, D

$(y) \rightarrow X$

Load the contents of memory into the X register.

Modifiers: P, X, E, B, \*, =

Refer to Table 3-1 for the allowable address modifiers (and legal combinations) for basic instructions under formats 1A, B, C, D.

<u>lA formats</u>. In general, these are used most frequently to load and store variables where the "address" is within the range of the displacement field, D. That is,

$-128 \le address \le 127$

is within the range of the current instruction.

1B formats. These are used, generally, to access constants. It is the closest thing to a literal in the 2+2 assembler. Literal pools, themselves, do not exist.

IC formats. This is the extended or two word form of the basic instruction and is used to access address outside the range of the displacement field.

TABLE 3-1. ADDRESS MODIFIERS FOR BASIC INSTRUCTION FORMATS 1A, B, C, D

#### where,

\* = Indirect Addressing

P = Relative to P counter

X = Indexing

B = Relative to B register

E = Extended address format (2 word form)

#### and,

- All other combinations of modifiers are illegal

- The modifiers may be specified in any order

- "A" may not be a literal but is the address of the word to be loaded

| Format | Example     | Address<br>Code   | Modifier<br>Codes |   |   | Restrictions                  |

|--------|-------------|-------------------|-------------------|---|---|-------------------------------|

|        |             |                   | I                 | X | R |                               |

| 1A     | LDA A       | P+D               | 0                 | 0 | 1 | $D = A-P; -128 \le D \le 127$ |

| 1A     | LDA* A      | (P+D)             | 1                 | 0 | 1 | $D = A-P; -128 \le D \le 127$ |

| 1A     | LDA A,X     | D+X or            | 0                 | 1 | 0 | if $-128 \le A \le 127$       |

|        |             | P+D+X             | 0                 | 1 | 1 | if A < -128 or A > 127        |

| 1A     | LDA A,XP    | P+D+X             | 0                 | 1 | 1 | $D = A-P; -128 \le D \le 127$ |

| 1A     | LDA* A,X    | (P+D)+X           | 1                 | 1 | 1 | $D = A-P; -128 \le D \le 127$ |

| 1A     | LDA A,B     | B+D               | 0                 | 0 | 0 | $D = A-P; -128 \le D \le 127$ |

| 1A     | LDA* A,B    | (B+D)             | 1                 | 0 | 0 | $D = A-P; -128 \le D \le 127$ |

| 1A     | LDA* A, BX  | (B+D)+X           | 1                 | 1 | 0 | $D = A-P; -128 \le D \le 127$ |

| 1B     | LDA =A      | P+1               |                   |   |   |                               |

| 1C     | LDA A,E     | (P+1)             |                   |   |   |                               |

| 1C     | LDA* A,E    | ((P+1))           |                   |   |   |                               |

| 1C     | LDA A, EX   | (P+1)+X           |                   |   |   |                               |

| 10     | LDA* A,XE   | ((P+1))+X         |                   |   |   |                               |

| 1D     | LDA A,BE    | B + (P + 1)       |                   |   |   |                               |

| 1D     | LDA* A,EB   | (B + (P + 1))     |                   |   |   | ·                             |

| 1D     | LDA A, BXE  | B + (P + 1) + X   |                   |   |   |                               |

| 1D     | LDA* A, EXB | (B + (P + 1)) + X |                   |   | X |                               |

1D format. The format is used to force address translation relative to the base of stack or B register. This is needed only if the displacement added to the contents of B is not in the -128 to +127 range, or if both B and X are to be added to the displacement.

LDXEA Load X with Effective Address 04(0) 6A

$Y \rightarrow X$

Load the effective address of memory into the X register.

Modifiers: B, X, \*

LDXI Load X, Immediate 00 10

$LIT9 \rightarrow X$

The 9-bit literal contained in bit positions 7-15 of the instruction is loaded into the X register. The sign of the literal is extended through  $X_{0-6}$ .

Modifiers: None.

STX Store X 01 1A, C, D

$(X) \rightarrow y$

Store the contents of the X register in memory location y.

Modifiers: P, X, B, E, \*

XXM Exchange X and Memory 05(0) 6A

$(y) \rightarrow X; (X) \rightarrow y$

The contents of the X register and memory location y are exchanged.

Modifiers: B, X, \*

LDU Load U 02 1A, B, C, D

$(y) \rightarrow U$

Load the contents of memory into the U register.

Modifiers: P, X, E, B, \*, =

LDUI LoadU, Immediate 01 10

LIT9 - U

The 9-bit literal contained in bit positioning 7-15 of the instruction is loaded into the U register. The sign of the literal is extended through  $U_{0-6}$ .

Modifiers: None.

STU Store U 03 1A, C, D

$(U) \rightarrow y$

Store the contents of the U register in memory location y.

Modifiers: P, X, B, E, \*

LDA Load A 04 1A, B, C, D

$(y) \rightarrow A$

Load the contents of memory into the A register.

Modifiers: P, X, E, B, \*, =

LDAEA Load A with Effective Address 04(2) 6A

$y \rightarrow A$

Load the effective address of memory into the A register.

Modifiers: B, X, \*

LDAI Load A, Immediate 02 10

$LIT9 \rightarrow A$

The 9-bit literal contained in bit positions 7-15 of the instruction is loaded into the A register. The sign of the literal is extended through  $A_{0-6}$ .

#### STA Store A 05 1A, C, D

$$(A) \rightarrow y$$

Store the contents of the A register in memory location y.

Modifiers: P, X, B, E, \*

# XAM Exchange A and Memory 05(22) 6A

$$(y) \rightarrow A; \quad (A) \rightarrow y$$

The contents of the A register and memory location y are exchanged.

Modifiers: B, X, \*

$$(y) \rightarrow E$$

Load the contents of memory into the E register.

Modifiers: P, X, B, E, \*, =

# LDEI Load E, Immediate 03 10

LIT9

$$\rightarrow$$

E

The 9-bit literal contained in bit positions 7-15 of the instruction is loaded into the E register. The sign of the literal is extended through  $E_{0-6}$ .

Modifiers: None.

#### STE Store E 07 1A, C, D

$$(E) \rightarrow y$$

Store the contents of the E register in memory location y.

Modifiers: P, X, B, E, \*

#### LDM Load Multiple 01, 41 6D

$$(y, \ldots, y+n, 0 \le n \le 3) \rightarrow X$$

, U, A, and/or E

The selected registers, X, U, A, and/or E, are loaded from the contents of memory locations y, y+1,..., y+n, where n is determined by the number of registers selected. The variable field of the instruction has three subfields: the selected registers, the memory address, and modifiers, if any. For example:

The contents of A + X is loaded into the U register, and A + X + 1 is loaded into the E register. Registers are always loaded in the order X, U, A, and/or E, no matter how the order is specified in the symbolic instruction.

Modifiers: B, X, \*

#### STM Store Multiple 02, 42 6D

$$(X, U, A, and/or E) \rightarrow y, ..., y+n, 0 \le n \le 3$$

The contents of the X, U, A, and/or E registers are stored in memory locations y, y+1,...,y+n, where n is determined by the number of registers selected.

The variable field for this instruction contains three subfields: the selected registers, the memory address, and modifiers; if any. For example:

The contents of the X and A registers are stored in memory locations B+A and B+A+1, respectively. Registers are always stored in the order X, U, A, and/or E, no matter how the order is specified in the symbolic instruction.

Modifiers: B, X, \*

#### PUSHM Push Multiple 0 4A

$$(X, U, A, and/or E) \rightarrow (T), \ldots, (T) + n; 0 \le n \le 3$$

$(T) + n + 1 \rightarrow T$

The contents of the selected registers, X, U, A, and/or E are stored in consecutive locations defined by the contents of the top of stack pointer, T. T is then incremented by n + 1 so that the pointer is set to the next available word in the stack. Registers are pushed into the stack in the order X, U, A, and/or E, no matter how the order is specified in the symbolic instruction.

Stack overflow trap if (T) > (L).

Modifiers: None.

# POPM Pop Multiple 1 4A

$$((T) - 1), \ldots, ((T) - n - 1) \rightarrow E$$

, A, U, and/or X;  $0 \le n \le 3$ ;  $(T) - n - 1 \rightarrow T$

The selected registers, E, A, U, and/or X are loaded from the memory location specified by the top of stack pointer, T.

T is then decremented by n + 1 to reflect the next available word in the stack. Registers are popped from the stack into registers in the order E, A, U, and/or X, regardless of the order specified in the symbolic instruction.

Stack underflow trap if (T) < (B).

Modifiers: None.

#### PUSHN Push Null 06(0) 6A, G

$$(T) + (y) \rightarrow T$$

The contents of the top of stack pointer, T, is incremented by the contents of the memory location y. There are two forms to the instruction:

6A format - Normal two word form

PUSHN A

The contents of A are added to the T register.

Modifiers: B, X, \*

6G format - Immediate or literal form

PUSHN = A

The address or value A is added to the T register.

Modifiers: None.

Stack overflow trap if (T) > (L). Stack underflow trap if (T) < (B).

"Specified map" instructions will be set to select the user map, which is the map in which the address is valid.

#### MSKM Mask Mode Bit 56(0) 2

The complement of the previous mode bit in the status register is logically "anded" with bit 0 of the X register, and the result left in bit 0 of the X register. That is, if the previous mode bit is 1, bit 0 of the X register is cleared. This is useful for passing addresses back from a system call to a calling routine: if the calling routine is system code, then bit 0 (map select bit) is left alone. If the calling routine is user code, then bit 0 (which is no longer map select in user code) is cleared.

#### INPUT OUTPUT

# LDAC Load A from Console Switches 57 2

The 16 data switches on the programmer's console are interrogated and their state placed in the A register.

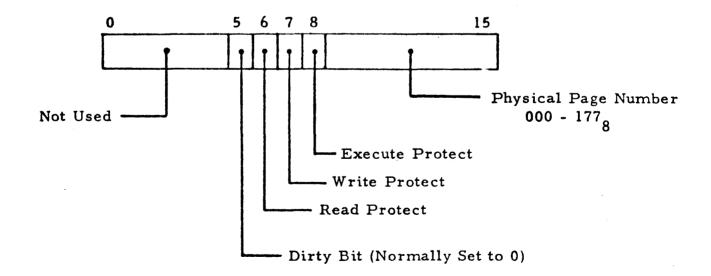

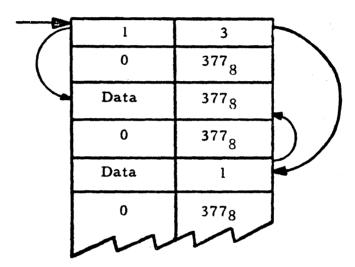

#### LDMAP Load Map 60 2

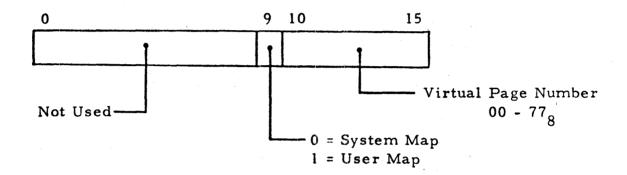

A number of consecutive map entries are set from consecutive core locations: the starting map page number is in A (00-77, system map pages 00 to 77; 100-177, user map pages 00 to 77), the starting core location is in X, and the number of map cells to be loaded is in U. The format of the core locations to be transferred to the map is as follows:

#### LLDB Locate Leading Dirty Bit 70 2

The map entries are inspected, beginning at the page number in X, for a "dirty" bit that is set. If one is found, the next instruction will be skipped and X will contain the page number of the page containing the dirty bit. If none is found, the next instruction will be executed with no skip. The format of the X register when a dirty bit is found is as follows:

#### SIM SET Interrupt Mask 75 6A, 6G

The operand is logically ANDed with a constant of 137777B (all 1's except for the system stack overflow interrupt mask bit) and placed in the software interrupt mask register. The firmware interrupt mask register is then loaded from the software mask down to, but not including, the bit number specified in bits 12-15 of the current status register. The system stack overflow interrupt is generated by firmware rather than by an external signal, so it is always enabled regardless of the contents of the mask registers.

#### DOUT Direct Output 75 2

The contents of the X register are placed on the I/O address lines. The contents of the A register are placed on the I/O data lines, and an I/O cycle is initiated. See descriptions of the I/O system for the address codes used to access the various I/O devices.

#### DIN Direct Input 74 2

The contents of the X register are placed on the I/O address lines. The I/O data lines are sampled after an appropriate delay and the data sampled is placed in the A register. See descriptions of the I/O system for the address codes used to access the various I/O devices.

#### IOC Input/Output Control 71 2

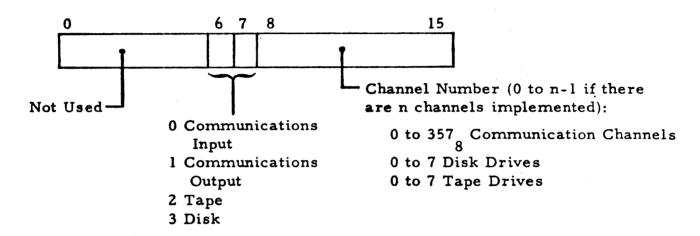

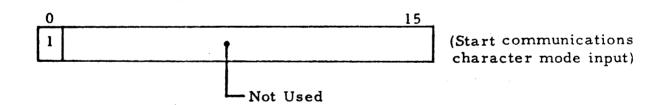

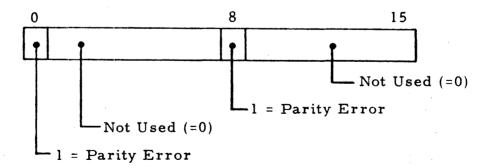

This instruction is used in the Disk, Tape, and Communications I/O subsystems. A channel code is given in X and a function code in A, to control input or output to a tape unit, disk drive or communications channel. The register formats are:

#### X Register (Channel Code)

#### A Register (Function Code)

# SIL Set Interrupt Lockout 72(0) 2

The firmware interrupt mask is set to zero, locking out all interrupts except system stack overflow. The software mask is unchanged.

# RIL Release Interrupt Lockout 73(0) 2

The firmware interrupt mask is loaded from the software mask down to, but not including, the bit number specified in bits 12-15 of the current status register.

# SRTRN System Return 2 4A

This instruction is used to return from system calls. It resets the status, program location counter, and stack pointers to the states they had when the system call was entered. It also restores any of the registers X, U, A, and E that are not used for passing parameters. If a return to user mode occurs, then the stack pointers are shifted back to the user stack. Symbolically,

If mode is now user (after S is restored), then:

If (B)>(T), stack underflow trap

$$((T)-3) \rightarrow B$$

$$((T)-1) \rightarrow L$$

$$((T)-2) \rightarrow T$$

The instruction count mechanism may be activated by setting ((B)-7) properly before executing SRTRN.

#### IRTRN Interrupt Return 64 2

Return from an interrupt routine, restoring registers to the state they had when the interrupt became active:

$$(B)-7 \rightarrow T$$

$$((T)) \rightarrow S$$

$$((T)+1) \rightarrow X$$

$$((T)+2) \rightarrow U$$

$$((T)+3) \rightarrow A$$

$$((T)+4) \rightarrow E$$

$$((T)+5) \rightarrow P$$

$$((T)+6) \rightarrow B$$

If (B)>(T), stack underflow trap

If mode is now user (after S is restored), then:

$$((T)-3) \rightarrow B$$

$$((T)-1) \rightarrow L$$

$$((T)-2) \rightarrow T$$

The firmware interrupt mask is loaded from the software interrupt mask down to but not including the bit number specified in bits 12-15 of the restored status register. This enables all interrupts of higher priority (lower number) than the one to which the return is made.

#### HLT Halt 77 2

The processor enters the halt mode, lights the HALT status light on the control panel, and stops executing instructions. The programmers control panel is enabled while the processor is in the halt mode.

#### CHARACTER INSTRUCTIONS

LDC Load Character 64(0) 6B, C

$$(y_B) \to A_{8-15}; 0 \to A_{0-7}$$

Load the contents of byte location y<sub>B</sub> into bit positions 8-15 of the A register. Bit positions 0-7 of A are set to zero.

Modifiers: B, X, \*

STC Store Character 64(1) 6B, C

$$(A_{8-15}) \rightarrow y_B$$

Store bit positions 8-15 of the A register into byte location y<sub>B</sub>. The A register is unchanged.

Modifiers: B, X, \*

#### CPRS Compare Strings 052 2

Two byte strings in memory are compared. The byte addresses of the first character of each string must initially be contained in the X and A registers. The number of characters to be compared must be contained in the U register.

A simple ASCII comparison is performed, character by character. Hence, "G" is > "F", and "5" is > "4".

If the string designated in the A register > string in the X register, the next sequential instruction is executed.

If the string designated in the A register = string in the X register, the next sequential instruction is skipped, and execution continues with the following instruction.

If the string designated in the A register < string in the X register, the next two sequential instructions are skipped, and execution continues with the following instruction.

If an equal compare is made, the contents of the X and A registers point one character beyond the last character compared. If an unequal compare is made, the contents of the X and A registers point to the characters found to be unequal.

The CPRS instruction is interruptable and may be restarted.

Modifiers: None.

$$((y)_B) \rightarrow A_{8-15}; \quad 0 \rightarrow A_{0-7}$$

Memory location y contains a byte address used to access a string. The instruction loads the contents of the specified byte address into bit positions 8-15 of the A register. Bit positions 0-7 of the A register are set to zero.

The byte address referred to above is interpreted as a string pointer. A string is thought of as being defined by two string pointers: a left pointer (LP), and a right pointer (RP). For purposes of utilizing the character instructions, these pointers are thought of as occurring in pairs, left and right, respectively. The pointers are described in more detail in the subsequent discussion of the GFCT instruction. The reader is referred to this section for further explanation.

The GFC instruction simply loads one byte of a string into the A register. No modification of the string pointers occurs. Therefore, repeated execution of a GFC instruction results in repeatedly loading the same byte.

Modifiers: B, X, \*

GFCT Get First Character with Test 65(1) 6A

String is tested for null; If not null,

$$((y)_B) \rightarrow A_{8-15}$$

;  $0 \rightarrow A_{0-7}$

Assume that the memory word pair BA and BA + 1 are memory locations containing byte addresses for two string pointers — the left pointer and right pointer, respectively,

| вА | LP |

|----|----|

| +1 | RР |

Both the left and right pointers (LP and RP) are 16 bit byte addresses. The left pointer indicates the first byte of the string. The right pointer is set at the last byte of the string plus one.

The length of a designated string is always defined as RP-LP. A string is defined as null if  $LP \ge RP$ . That is, if the left pointer has caught up with or passed beyond the right pointer. All "get" and "insert" character instructions access and modify strings via the left and right string pointers.

The instruction GFCT executes in the following manner. First the string pointers indicated at memory locations y and y + l are tested for a null string. If the left pointer is greater than or equal to the right pointer ( $LP \ge RP$ ), the string is null, and execution continues with the next sequential instruction. The contents of the A register are unchanged.

If the string is not null, the contents of the byte address specified in memory location y are loaded into bit positions 8-15 of the A register. Bit positions 0-7 of A are set to zero. The next sequential instruction is skipped and execution continues with the following instruction.

Modifiers: B, X, \*

# GCI Get Character and Increment 65(2) 6A

$$((y)_B) \rightarrow A_{8-15}; \quad 0 \rightarrow A_{0-7}; \quad (y) + 1 \rightarrow y$$

Memory location y contains a byte address used to access a string. The instruction loads the contents of the specified byte address into bit positions 8-15 of the A register. Bit positions 0-7 of A are set to zero, and the byte address is incremented by one.

Modifiers: B, X, \*

GCIT Get Character and Increment with Test 65(3) 6A String is tested for null; If not null,  $((y)_B) \rightarrow A_{8-15}$ ;  $0 \rightarrow A_{0-7}$ ;

$$(y) + 1 \rightarrow y$$

The string pointers indicated at memory locations y and y + 1 are tested for a null string. If the left pointer is greater than or equal to the right pointer ( $LP \ge RP$ ), the string is null and execution resumes at the next sequential instruction. The contents of A are unchanged, and the left pointer is not incremented.

If the string is not null, the contents of the byte address specified in memory location y are loaded into bit positions 8-15 of the A register.

Bit position 0-7 of A are set to zero, and the byte address left pointer is incremented by one. The next sequential instruction is skipped, and execution resumes with the following instruction.

Modifiers: B, X, \*

# IFC Insert First Character 65(4) 6A

$$(A_{8-15}) - (y)_{B}$$

The contents of bit positions 8-15 of the A register replace the contents of the byte address referred to by the contents of memory location y of the instruction.

The byte in the A register is placed in the byte address defined by the left pointer of the string. This instruction may develop a null string since no test concerning the right pointer is made.

Modifiers: B, X, \*

# IFCT Insert First Character with Test 65(5) 6A

String is tested for null; If not null,  $(A_{8-15}) \rightarrow (y)_B$

The string pointers indicated at memory location y and y + 1 are tested for a null string. If the left pointer is greater than or equal to the right pointer ( $LP \ge RP$ ), the string is null and execution resumes at the next sequential instruction. The byte specified by the left pointer is unchanged.

If the string is not null, the contents of bit positions 8-15 of the A register replace the contents of the byte address referred to by the contents of memory location y of the instruction. The next sequential instruction is skipped and execution resumes with the following instruction.

Modifiers: B, X, \*

# ICI Insert Character and Increment 65(6) 6A

$$(A_{8-15}) \rightarrow (y)_B; (y) + 1 \rightarrow y$$

The contents of bit positions 8-15 of the A register replace the contents of the byte address referred to by the contents of memory location y of the instruction. The byte address (left pointer) is incremented by one.

This instruction may develop a null string since no test concerning the right pointer is made.

Modifiers: B, X, \*

# ICIT Insert Character and Increment, with Test 65(7) 6A String is tested for null; if not null, $(A_{8-15}) \rightarrow (y)_B$ ; $(y) + 1 \rightarrow y$

The string pointers indicated at memory locations y and y + 1 are tested for a null string. If the left pointer is greater than or equal to the right pointer ( $LP \ge RP$ ), the string is null and execution continues with the next sequential instruction. The byte specified by the left pointer is unchanged, and the left pointer is not incremented.

If the string is not null, the contents of bit positions 8-15 of the A register replace the contents of the byte address referred to by the contents of memory location y of the instruction. The byte address (left pointer) is incremented by one. The next sequential instruction is skipped and execution continues with the following instruction.

Modifiers: B, X, \*

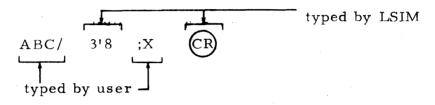

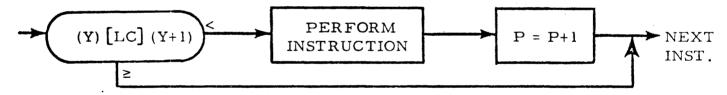

#### PRIVILEGED INSTRUCTIONS