# LOGICON 2+2 SYSTEM REFERENCE MANUAL

LOGICON INC.

1075 CAMINO DEL RIO, SOUTH

SAN DIEGO, CALIFORNIA

15 December 1970

### TABLE OF CONTENTS

| Section |                                          | Page         |

|---------|------------------------------------------|--------------|

|         | PREFACE                                  |              |

| I       | INTRODUCTION                             | 1 - 1        |

| II      | SYSTEM DESCRIPTION                       | 2-1          |

|         | Functional Organization                  | 2-1<br>2-3   |

|         | Equipment Organization                   | 2-3          |

|         | Programmable Processors (CP and AP)      | 2-5          |

|         | Virtual Address Translator (VAT)         | 2-6          |

|         | Drum Processor (DP)                      | 2-8          |

|         | Peripheral Processor                     | 2-10         |

| III     | PROCESSOR ORGANIZATION                   | 3 - 1        |

|         | Registers                                | 3 - 1        |

|         | A = Accumulator Register                 | 3 - 1        |

|         | U = Upper Accumulator Register           | 3 - 1        |

|         | E = Exponent Register                    | 3 - 1        |

|         | X = Index Register                       | 3-2          |

|         | P = Program Counter Register             | 3-2<br>3-2   |

|         | B = Base of Stack Register               | 3-2          |

|         | L = Limit of Stack Space Register        | 3-2          |

|         | S = Status Register                      | 3-2          |

|         | Representation of Information            | 3-2          |

|         | Machine Word                             | 3-3          |

|         | Alphanumeric Data                        | 3-3          |

|         | One Word Binary Integers                 | 3-4          |

|         | Three Word Binary Integers               | 3-4          |

|         | Three Word Binary Floating Point Numbers | 3-4          |

|         | Four Word Binary Floating Point Numbers  | 3 - 5        |

|         | Processor Features                       | 3 <b>-</b> 5 |

|         | Stack                                    | 3 <b>-</b> 5 |

|         | Skips and the Delayed Skip (DSK)         |              |

|         | Instruction                              | 3-6          |

|         | Processor Mode                           | 3-7          |

|         | Status Register                          | 3-8          |

| •       | Traps, System Calls, and Interrupts      | 3-11<br>3-18 |

|         | Clock                                    | 2-10         |

| Section |                                | Page |

|---------|--------------------------------|------|

|         | Stall Alarm                    | 3-19 |

|         | Programmer Panel (Prototype)   | 3-19 |

|         | HALT Condition                 | 3-23 |

|         | Power Up/Down                  | 3-24 |

|         | Dedicated Memory Locations     | 3-25 |

|         | Instruction Formats            | 3-26 |

|         | Addressing                     | 3-27 |

|         | General                        | 3-27 |

|         | Symbols                        | 3-27 |

|         | General Addressing Conventions | 3-30 |

| ΙV      | INSTRUCTION REPERTOIRE         | 4-1  |

|         | Loads and Stores               | 4-1  |

|         | LDX.                           | 4-1  |

|         | LDXEA                          | 4-3  |

|         | LDXI                           | 4-3  |

|         | STX                            | 4-3  |

|         | XXM                            | 4-3  |

|         | LDU                            | 4-3  |

|         | LDUI                           | 4-4  |

|         | STU                            | 4-4  |

|         | LDA                            | 4-4  |

|         | LDAEA                          | 4-4  |

|         | LDAI                           | 4-4  |

|         | STA                            | 4-5  |

|         | XAM                            | 4-5  |

|         | LDE                            | 4-5  |

|         | LDEI                           | 4-5  |

|         | STE                            | 4-5  |

|         | LDM                            | 4-6  |

|         | STM                            | 4-6  |

|         | PUSHM                          | 4-6  |

|         | POPM                           | 4-7  |

|         | PUSHN                          | 4-7  |

|         | MSKM                           | 4-8  |

|         | Input Output                   | 4-8  |

| . •     | LDAC                           | 4-8  |

|         | LDMAP                          | 4-8  |

|         | LLDB                           | 4-9  |

| Section |                         | Page      |

|---------|-------------------------|-----------|

|         | SIM SET                 | 4-9       |

|         | DOUT                    |           |

|         | DIN                     | 4-9       |

|         | IOC                     | 4-10      |

|         | SIL                     | 4-10      |

|         | RIL                     | 4-11      |

|         | SRTRN                   | 4-11      |

|         | IRTRN                   |           |

|         | HLT                     | 4-12      |

|         | Character Instructions  | 4-13      |

|         | LDC                     | 4-13      |

|         | STC                     | 4-13      |

|         | CPRS                    |           |

|         | GFC                     | 4-14      |

|         | GFCT                    |           |

|         | GCI                     |           |

|         | GCIT                    |           |

|         | IFC                     |           |

|         | IFCT                    |           |

|         | ICI                     |           |

|         | ICIT                    |           |

|         | Privileged Instructions |           |

|         | LDAOM                   |           |

|         | STAOM                   |           |

|         | TSLOM                   |           |

|         | LDAOMF                  |           |

|         | LDASM                   |           |

|         | STASM                   | •         |

|         | LDXSM                   | •         |

|         | LDASMF                  | ·         |

|         | MRGM                    |           |

|         | POPN                    |           |

|         | LDB                     |           |

|         |                         | • • • • • |

|         | STB                     |           |

|         | LDSP                    |           |

|         | LDBTL                   |           |

|         | STSP                    |           |

|         | STZ                     | 4-22      |

|         | 1 0 2 CA 1 3 IVI        | 4 = /./   |

| Section |                             | Page |

|---------|-----------------------------|------|

|         | SSABM                       | 4-22 |

|         | MOVE                        | 4-22 |

|         | CLX                         | 4-23 |

|         | CLU                         | 4-23 |

|         | CLA                         | 4-23 |

|         | CLE                         | 4-23 |

|         | LDF                         | 4-23 |

|         | STF                         | 4-24 |

|         | LDD.                        | 4-24 |

|         | LINK                        | 4-24 |

|         | DLINK                       | 4-25 |

|         | Inter-Register Instructions | 4-25 |

|         | RCPY                        | 4-25 |

|         | RNEG                        | 4-25 |

|         | RXCH                        | 4-25 |

|         | XSA                         | 4-26 |

|         | RDS                         | 4-26 |

|         | Fixed-Point Arithmetic      | 4-26 |

|         | ADX                         | 4-26 |

|         | ADXI                        | 4-26 |

|         | ADXIS                       | 4-27 |

|         | SBX                         | 4-27 |

|         | RSBX                        | 4-27 |

| •       | MPX                         | 4-27 |

|         | ADU.                        | 4-27 |

|         | ADUI                        | 4-27 |

|         | SBU                         | 4-28 |

|         | ADA                         | 4-28 |

|         | ADAI                        | 4-28 |

|         | SBA                         | 4-28 |

|         | RSBA                        | 4-28 |

|         | MPA                         | 4-28 |

|         | DVUA                        | 4-29 |

|         | DVA                         | 4-29 |

| · ·     | RDVA                        | 4-29 |

|         | RADD                        | 4-29 |

|         | RSUB                        | 4-30 |

|         | ADDM                        | 4-30 |

|         | SUBM                        | 4-30 |

|         | 3.5737.00                   | 4 20 |

| Section |                           | Page |

|---------|---------------------------|------|

|         | MDEC                      | 4-31 |

|         | TAD                       | 4-31 |

|         | NT AD                     | 4-32 |

|         | TSB                       | 4-32 |

|         | RTSB                      | 4-32 |

|         | TMP                       | 4-32 |

|         | TMPF                      | 4-33 |

|         | TDV                       | 4-33 |

|         | TDVF                      | 4-33 |

|         | ADAS                      | 4-33 |

|         | SBAS                      | 4-33 |

| •       | RSBAS                     | 4-34 |

|         | MPAS                      | 4-34 |

|         | DVAS                      | 4-34 |

|         | RDVAS                     | 4-35 |

|         | ADUS                      | 4-35 |

|         | SBUA                      | 4-35 |

|         | DVUAS                     | 4-35 |

|         | ADXS                      | 4-36 |

| •       | SBXS                      | 4-36 |

|         | RSBXS                     | 4-36 |

|         | MPXS                      | 4-36 |

|         | TADS                      | 4-37 |

|         | NT ADS                    | 4-37 |

|         | TSBS                      | 4-37 |

|         | RTSBS                     | 4-38 |

|         | TMPS                      | 4-38 |

|         | TMPFS                     | 4-38 |

|         | TDVS                      | 4-39 |

|         | TDVFS                     | 4-39 |

|         | TNEG                      | 4-40 |

|         | Floating Point Arithmetic | 4-40 |

|         | FAD                       | 4-40 |

|         | NFAD                      | 4-40 |

|         | FSB                       | 4-40 |

|         | RFSB                      | 4-41 |

|         | FMP                       | 4-41 |

|         | FDV                       | 4-41 |

|         | RFDV                      | 4-41 |

|         | FADS                      | 4-41 |

|         | ·                    |      |

|---------|----------------------|------|

| Section |                      | Page |

|         | NFADS                | 4-42 |

|         | FSBS                 | 4-42 |

|         | RFSBS                | 4-42 |

|         | FMPS                 | 4-43 |

|         | FDVS                 | 4-43 |

|         | RFDVS                | 4-43 |

|         | FIX                  | 4-43 |

|         | FLOAT                | 4-44 |

|         | NORM                 | 4-44 |

|         | FNEG                 | 4-44 |

|         | Logical Instructions | 4-44 |

|         | ANX                  | 4-45 |

|         | ANU                  | 4-45 |

|         | ANUI                 | 4-45 |

|         | ANUA                 | 4-45 |

|         | ANA                  | 4-45 |

|         | ANAI                 | 4-45 |

|         | ORA                  | 4-46 |

|         | ORAI                 | 4-46 |

|         | XRA                  | 4-46 |

| •       | XRAI                 | 4-46 |

|         | RAND                 | 4-46 |

|         | SETBA                | 4-47 |

|         | CLRBA                | 4-47 |

|         | CMPBA                | 4-48 |

|         | SETBM                | 4-48 |

|         | CLRBM                | 4-48 |

|         | CMPBM                | 4-49 |

|         | ANAS                 | 4-49 |

| •       | ORAS                 | 4-50 |

|         | XRAS                 | 4-50 |

|         | ANXS                 | 4-50 |

|         | Shift Instructions   | 4-51 |

|         | LLX/LRX              | 4-51 |

|         | ALU/ARU              | 4-51 |

|         | LLU/LRU              | 4-51 |

|         | RLU/RRU              | 4-52 |

|         | ALA/ARA              | 4-52 |

|         | T T A /T D A         | 4 52 |

| Section |                                  |                       |                         | Page  |

|---------|----------------------------------|-----------------------|-------------------------|-------|

|         |                                  |                       |                         |       |

|         |                                  |                       |                         | 4-52  |

|         |                                  | E                     |                         | 4-53  |

|         |                                  |                       |                         | 4-53  |

|         | LLUA/LRUA.                       |                       |                         | 4-53  |

|         | RLUA/RRUA.                       |                       | • • • • • • • •         | 4-54  |

|         | LLO                              |                       |                         | 4-54  |

|         | Compares and Te                  | sts                   |                         | 4-54  |

|         | SKXEI                            |                       |                         | 4-54  |

|         | SKXNI                            |                       |                         | 4-55  |

|         | SKAE                             |                       |                         | 4-55  |

|         | SKAN                             |                       |                         | 4-55  |

|         | SKAEI                            |                       |                         | 4-55  |

|         |                                  |                       |                         | 4-56  |

|         |                                  |                       |                         | 4-56  |

|         |                                  | • • • • • • • • • • • |                         | 4-56  |

|         |                                  |                       |                         | 4-57  |

|         |                                  |                       |                         | 4-57  |

|         |                                  |                       |                         | 4-57  |

|         |                                  |                       |                         | 4-58  |

|         | *                                |                       |                         | 4-58  |

|         |                                  |                       |                         | 4-58  |

|         |                                  |                       |                         | 4-59  |

|         |                                  |                       |                         | 4-59  |

|         |                                  |                       |                         | 4-59  |

|         |                                  |                       |                         | 4-60  |

|         |                                  |                       |                         | 4-60  |

|         |                                  |                       |                         | 4-61  |

|         |                                  | • • • • • • • • • • • |                         | 4-61  |

|         |                                  |                       |                         | 4-61  |

|         |                                  |                       |                         | 4-62  |

|         |                                  | • • • • • • • • • • • |                         |       |

|         |                                  |                       |                         |       |

|         |                                  | • • • • • • • • • • • |                         | 4-62  |

|         | *                                |                       |                         | 4-63  |

|         |                                  | • • • • • • • • • • • |                         | 4-63  |

|         |                                  |                       |                         | 4-63  |

|         | <del>-</del>                     |                       |                         | 4-63  |

|         | <b>v</b> = <b></b> · · · · · · · | • • • • • • • • • • • |                         | 4-63  |

|         | JMI                              |                       | · · · · · · · · · · · · | 4-64  |

|         | 37.77                            |                       |                         | 4 ( 1 |

| Section |                               | Page         |

|---------|-------------------------------|--------------|

|         | UJP                           | 4-64         |

|         | AJP                           | 4-65         |

|         | EJP                           | 4-65         |

|         | TJP                           | 4-65         |

|         | IJXN                          | 4-66         |

|         | DJXN                          | 4-66         |

|         | IJMP                          | 4-66         |

|         | Subroutine and System Linkage | 4-66         |

|         | JSPX                          | 4-66         |

|         | JSPM                          | 4-67         |

|         | CALL                          | 4-67         |

|         | RTRN                          | 4-67         |

|         | SCALL                         | 4-68         |

| -       | IJSPX                         | 4-69         |

|         | IJSPM                         | 4-69         |

|         | ICALL                         | 4-69         |

| V       | INPUT/OUTPUT                  | 5 <b>-</b> 1 |

|         | General                       | 5 <b>-</b> 1 |

|         | Peripheral Processor (PP)     | 5-2          |

|         | Interrupts Generated by PP    | 5-10         |

|         | Drum Processor                | 5-10         |

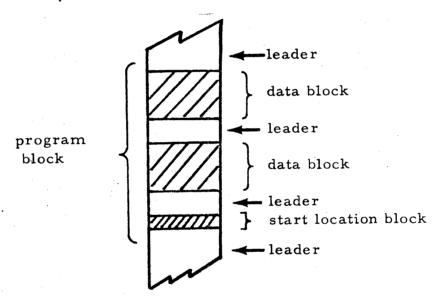

| APP. A  | BOOTSTRAP FORMATS             | <b>A-</b> 1  |

### LIST OF ILLUSTRATIONS

| Figure |                                                        | Page         |

|--------|--------------------------------------------------------|--------------|

| 1 - 1  | Typical LOGICON 2+2 Installation                       | 1 - 1        |

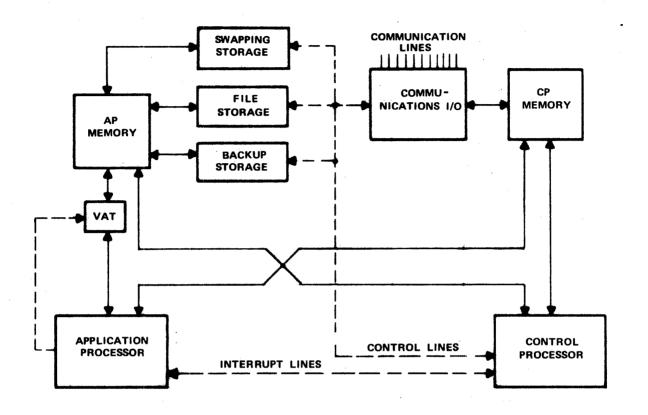

| 2-1    | LOGICON 2+2 System, Functional Block Diagram           | 2-2          |

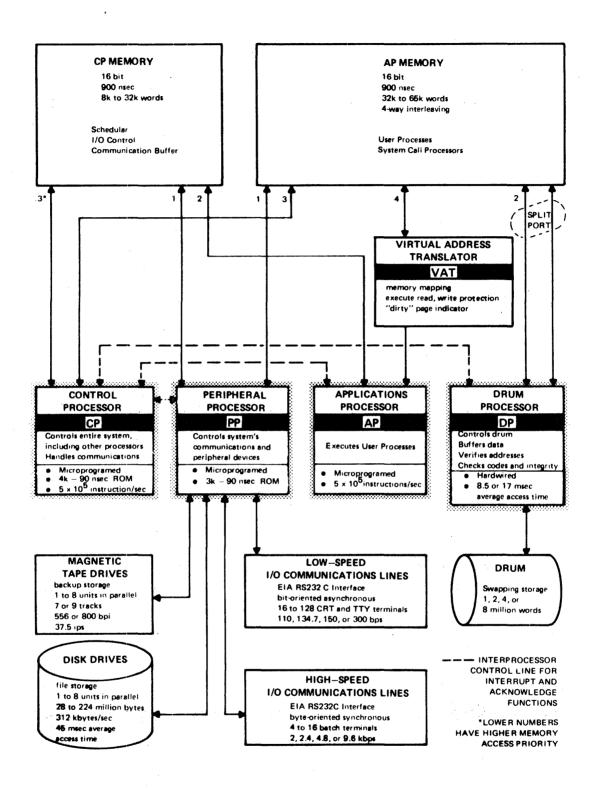

| 2-2    | LOGICON 2+2 Hardware Organization and Information Flow | 2-4          |

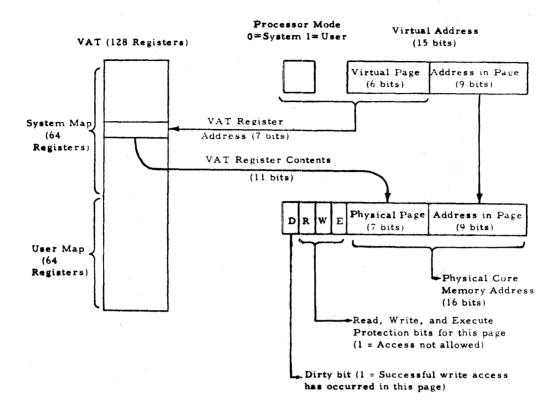

| 2-3    | VAT Operation                                          | 2-7          |

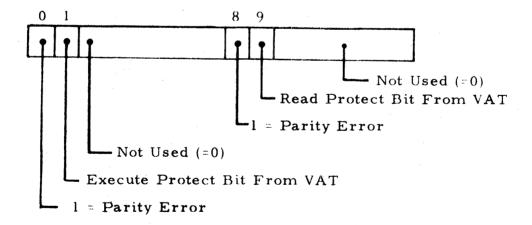

| 3 - 1  | Status Register Contents                               | 3-9          |

| 3-2    | Programmer Panel Layout                                | 3-20         |

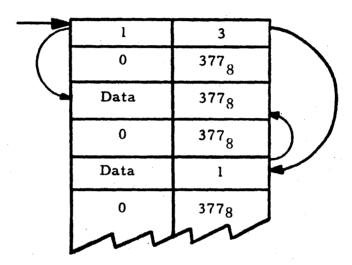

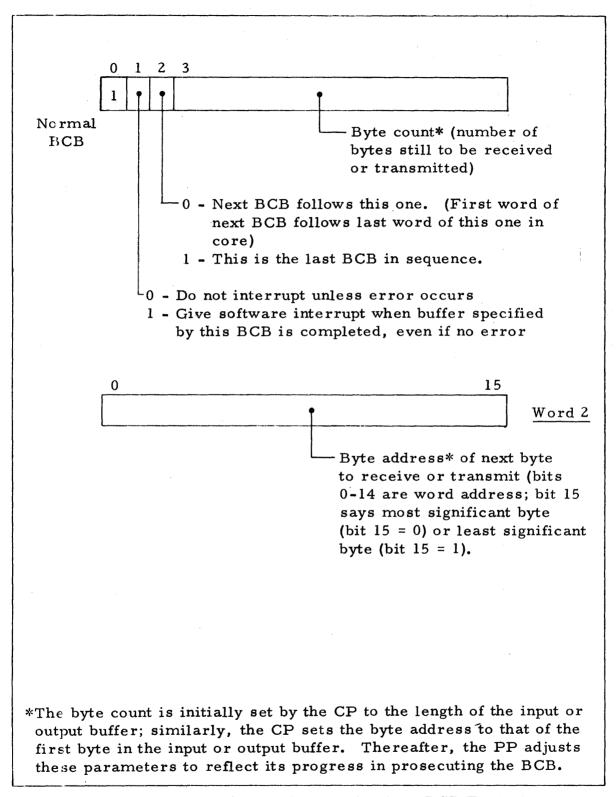

| 5 - 1  | Normal Communications BCB Format                       | 5 <b>-</b> 6 |

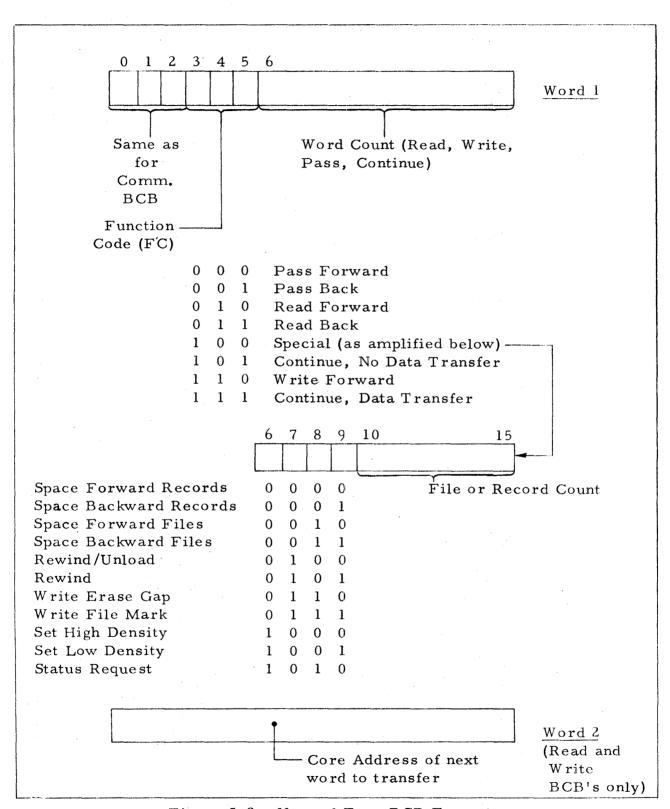

| 5-2    | Normal Tape BCB Format                                 | 5 <b>-</b> 7 |

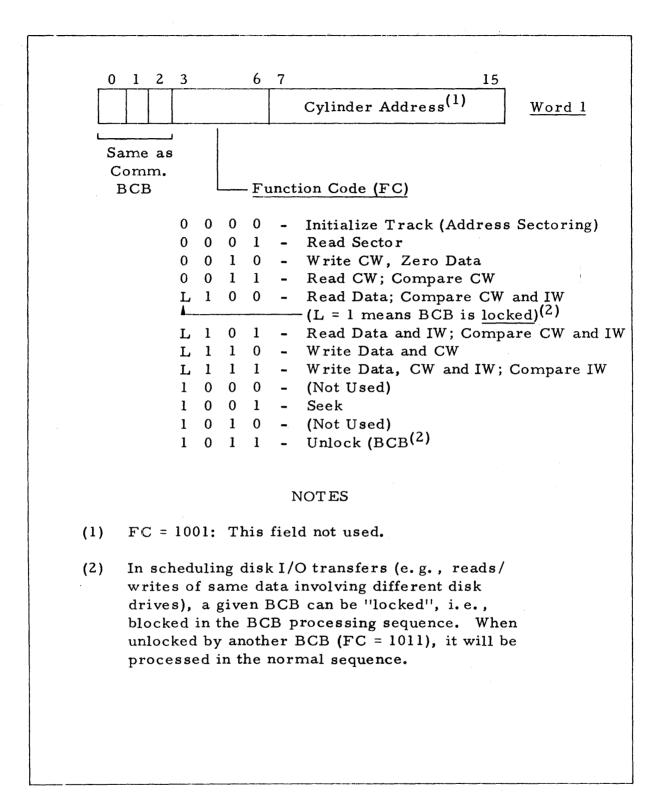

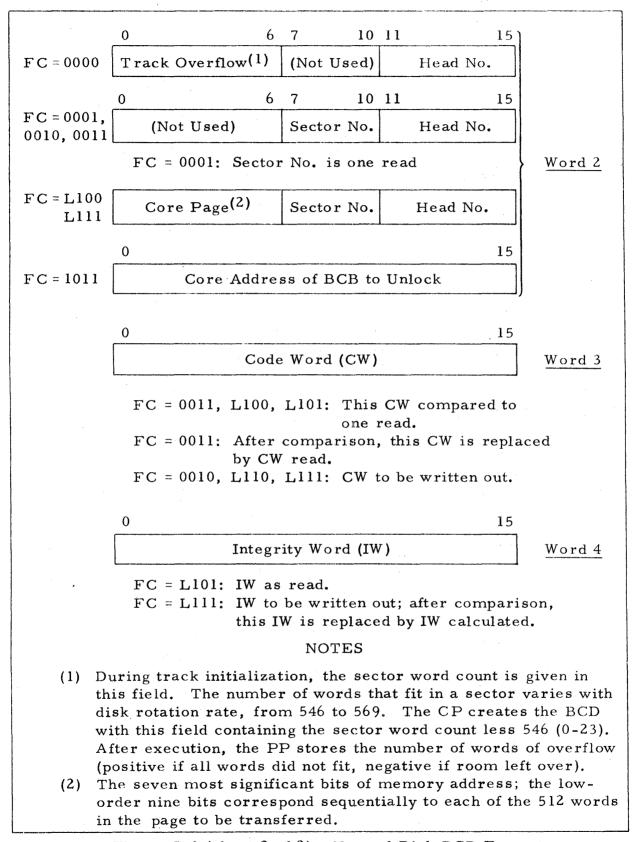

| 5-3    | Normal Disk BCB Format                                 | 5-8          |

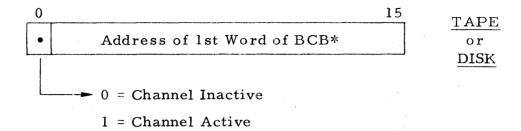

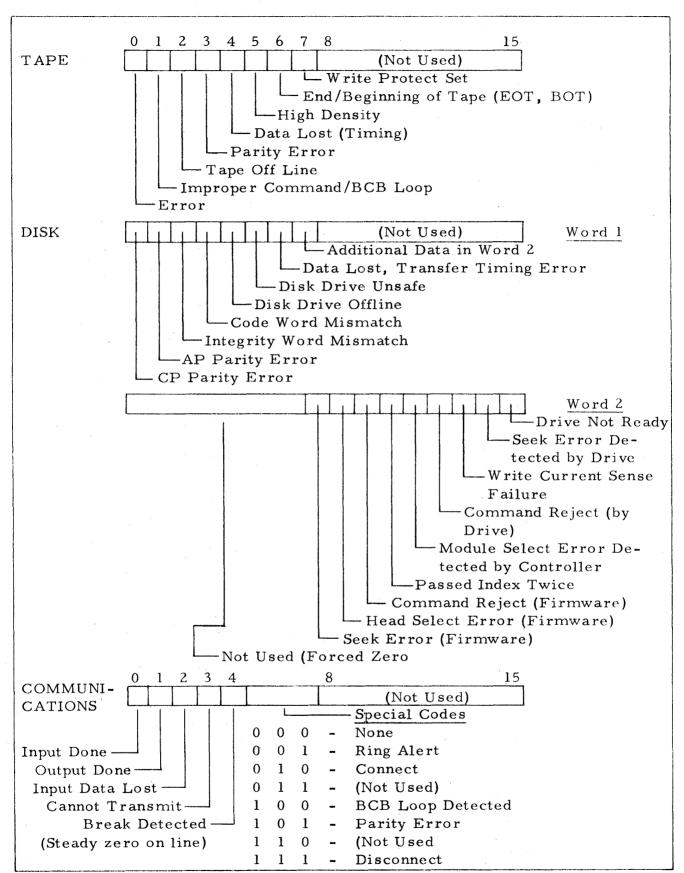

| 5-4    | PP Generated Interrupt Formats                         | 5-11         |

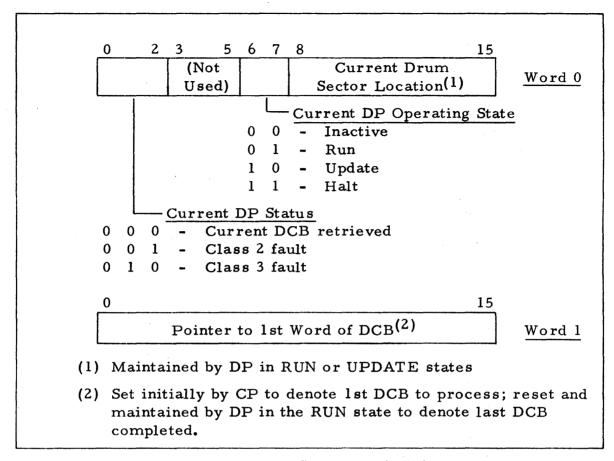

| 5-5    | Current State Cell (CSC) Format                        | 5-12         |

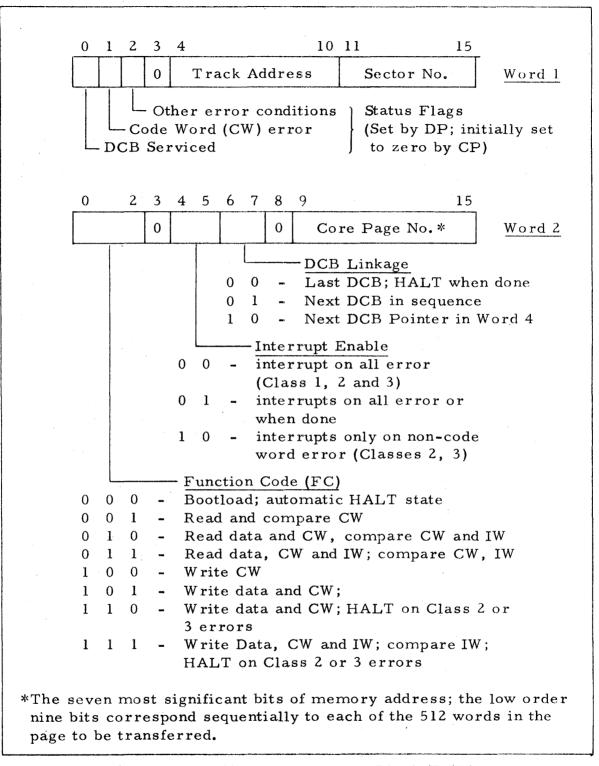

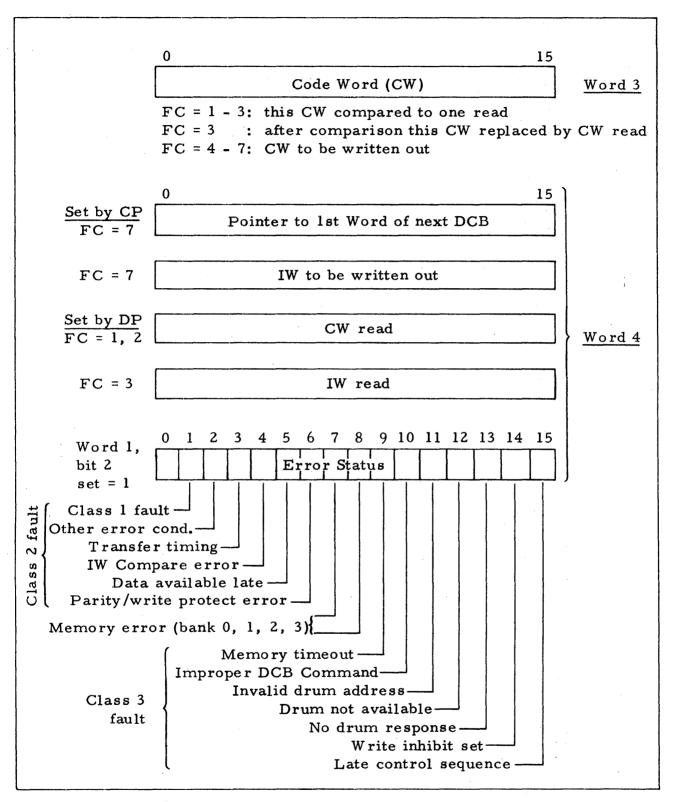

| 5-6    | Drum Control Block (DCB) Format                        | 5-13         |

|        |                                                        |              |

|        | I IOM OT MADI DO                                       |              |

|        | LIST OF TABLES                                         |              |

| Table  |                                                        | Page         |

| 3 - 1  | Interrupt Entry Locations (in System Address Space).   | 3 - 14       |

| 3-2    | Trap Entry Locations (in System Address Space)         | 3 - 15       |

| 3-3    | System Call Entry Locations (in System Address Space)  | 3-16         |

| 3-4    | Dedicated Memory Locations                             | 3-26         |

| 3 - 5  | Instruction Formats                                    | 3-28         |

| 4-1    | Address Modifiers for Basic Instruction Formats        | 4-2          |

| 4-2    | Conditions for all Skip/Jump Instructions              | 4-31         |

| 4-3    | Definitions of Boolean Operations                      | 4-44         |

| 4-4    | Simulated Systems Calls                                | 4-68         |

# Preface

This reference manual defines the LOGICON 2+2 System hardware configuration, the characteristics of the major components, the organization and instruction repertoire of the processors, and the characteristics of the software interface with the I/O subsystem and peripheral devices.

As we expect to improve this manual in future revisions, all readers are earnestly requested to send corrections and comments to:

LOGICON 2+2 System Documentation LOGICON, Inc., San Diego, Calif.

I . . .

# Introduction

Figure 1-1. Typical LOGICON 2+2 Installation

The 2+2 System is LOGICON's answer to the demand for a medium-sized, modular, highly responsive, inter-active shared-access system. The 2+2 exemplifies the versatility required for today's computing tasks. With its 215-instruction repertoire, micro-programmed hardware, "virtual memory" capability, and flexible peripheral interface it provides a tremendous capacity and excellent response for a multitude of applications.

With the wide range of system hardware and software, the 2+2 user can operate with a minimum of system components to serve his present needs, yet easily expand to meet future system requirements.

The LOGICON 2+2 (Figure 1-1) offers the user a new, more efficient approach to time-sharing.

# System Description

The LOGICON 2+2 is a multiprocessor system, the heart of which consists basically of two processors organized as computers and two processors organized as peripheral controllers. The following paragraphs discuss this system both in terms of its functional and its equipment organization.

#### FUNCTIONAL ORGANIZATION

A functional block diagram of the LOGICON 2+2 System is given in Figure 2-1. In this figure, solid lines represent information lines — dotted lines are control lines. The various blocks have the following general functions:

- The Application Processor (AP) is a microprogrammed computer that executes all user programs. It communicates with both AP and CP memory, and with the CP via interrupt lines.

- The Control Processor (CP) is a microprogrammed computer that performs system scheduling and I/O control functions. It communicates with AP and CP memory, with the AP via interrupt lines, and with all storage and communication devices.

- Memory accesses by the AP to its own memory are made through a mapping and protection unit called the Virtual Address Translator (VAT), which is controlled by the AP.

- AP memory may also be accessed by the swapping storage system, the file storage system, the backup storage system, and the CP. AP memory contains the active portion of the program currently being run for a user, some resident system code, and possibly parts of other users programs waiting to be swapped out or run.

Figure 2-1. LOGICON 2+2 System, Functional Block Diagram

- CP memory is accessed by the CP, AP, and the Communication I/O subsystem. It holds the bulk of the Monitor program and all communications I/O buffers.

- The swapping storage subsystem is mechanized by a drum and a Drum Processor (DP). It is capable of swapping programs and data in or out of AP memory at a rate of 1 million 16-bit words per second, under control of the CP. It has storage capacity for 1 to 8 million words.

- The file storage subsystem consists of from 1 to 8 disk drives, each capable of storing 14 million words, controlled by a Peripheral Processor (PP) which executes commands given it by the CP. Data is exchanged with AP memory at a rate of approximately 156,000 words per second. Average access time is 45 milliseconds.

- The backup storage system consists of from 1 to 8 magnetic tape units, controlled by the PP which executes commands given it by the CP. Data is exchanged with AP memory at a rate of approximately 15,000 words per second.

- The communication I/O subsystem handles low and high speed lines, full and half duplex, synchronous and asynchronous. It is controlled by the PP which executes commands given it by the CP. Data is exchanged with CP memory in a byte mode, at rates from 10 to 1200 bytes per second depending on line speed. Note that all system I/O is communications oriented.

#### EQUIPMENT ORGANIZATION

The organization of LOGICON 2+2 System hardware to accomplish these functions is shown in Figure 2-2. This is the same as Figure 2-1, except that the Swapping Storage subsystem is shown to consist of a Drum Processor (DP) and a drum; and the File Storage, Backup Storage, and Communications I/O subsystems are shown to be all implemented with a single Peripheral Processor (PP) connected to the appropriate devices.

The characteristics of each of the devices are described in more detail in the following paragraphs.

#### Core Memory

There are two core memories in the system, CP and AP memory, named after the programmable processor that executes instructions from each. Each memory has a basic 900 nanosecond cycle time, and stores data in words of 16 bits plus parity.

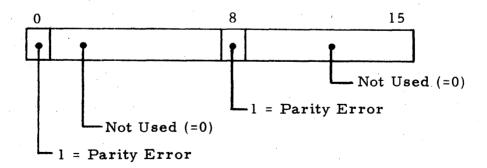

CP Memory. CP memory can have sizes of from 8K to 32K words in 4K increments. It is accessed by the PP (port priority 1), AP (port priority 2), and by the CP (port priority 3). Read accesses to CP memory may result in a parity error, resulting in action as follows:

- AP access: Other memory parity error trap in AP.

- CP access: Own memory parity error trap in CP.

- PP access: Error interrupt to CP.

AP Memory. AP memory can have sizes of 32K or 48K four-way interleaved, or 65K with eight-way interleaving. Interleaving refers to

Figure 2-2. LOGICON 2+2 Hardware Organization and Information Flow

assigning addresses in such a way that consecutive locations are in separate banks of memory, so that accesses can be overlapped. Interleaving is important in AP memory, because the swapping storage subsystem makes accesses to consecutive locations at a rate of 1 million words per second, and must be able to overlap accesses in order to "catch up" after interference with other devices has occurred.

AP memory is accessed by the PP (port priority 1), DP (port priority 2), CP (port priority 3), and AP via the VAT (port priority 4). Read accesses to AP memory through ports 1 through 3 can result in parity errors, processed as follows:

- PP access: Error interrupt in CP.

- DP access: Error interrupt in CP.

- CP access: Other memory parity error trap in CP.

Accesses through the VAT are more complex, in that both parity and protection violations may occur. Separate software trap entrances are provided in the AP for own memory parity error, read protection violation, write protect violation, execute protect violation, and indirect address protect violation. The VAT protection mechanism is discussed in more detail later in this section.

#### Programmable Processors (CP and AP)

The CP and AP are programmable processors with nearly identical instruction repertoires, determined by microcode in a read-only control memory. They are high speed, general purpose, binary computers with single address instructions, each capable of communicating with two separate 900 nanosecond memories of up to 32K words (64K words with a VAT).

The design features include:

- A microprogrammed read-only control memory for flexible and economical internal logic.

- Highly modular integrated circuit construction with etched circuit back planes.

- Programmable memory protection and mapping via the VAT.

- Byte and byte string manipulation instructions for efficient handling of character information.

- Hardware floating point and multiple precision instructions for "number-crunching" applications.

- Hardware stack for efficient processing of recursive routines, multilevel interrupts, and nested system calls.

- Bit, Byte, word, and triple word addressing capability, all fully indexed.

- Real time clock, providing both a "time-of-day" and a countdown clock.

- Stall alarm for detection of program loops.

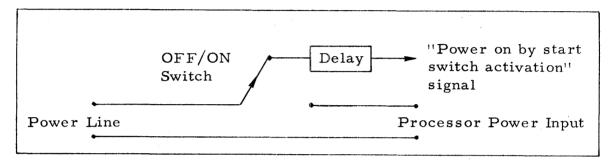

- Power fail-safe features in hardware and firmware.

The organization of these processors in terms of registers, stack operation, instruction repertoire, and I/O structure is covered in detail in Section III.

#### Virtual Address Translator (VAT)

The VAT is a program-controlled memory mapping and protection unit that can be inserted on any processor-to-memory access path. In the LOGICON 2+2 System it is used on the AP to AP-memory connection path.

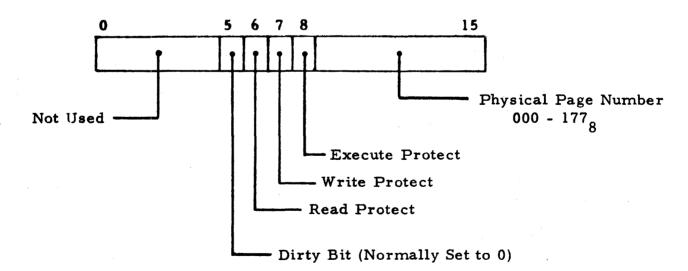

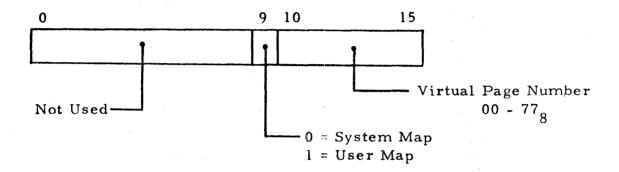

The VAT considers memory to be organized in 512-word pages. It provides memory mapping, access control, and changed data detection for each of 64 pages in system mode virtual memory and each of 64 pages in user mode virtual memory. The two separate mapping and protection sections are called the System Map and User Map, respectively. When the AP is in system mode, all AP accesses to AP memory are made via the System Map. When in user mode, all accesses are made through the User Map (except for certain privileged instructions). The operation of the VAT is shown in Figure 2-3.

The VAT contains 128 registers, 64 for the system map and 64 for the user map. Each register contains the following data:

• A 7-bit physical memory page number

Figure 2-3. VAT Operation

- Read, write, and execute protection bits

- A ''dirty'' bit, or ''data changed'' flag.

The contents of the 128 registers may be set by software control, and the dirty bits may be interrogated by software. (See the Load Map, LDMAP, and Locate Leading Dirty Bit, LLDB, instructions.)

When an AP memory access is initiated from the AP, the VAT in conjunction with AP firmware performs the following functions:

- Selects the proper map depending on processor mode (system or user)

- Selects one of 64 registers in the proper map, as addressed by the high order 6 bits of the 15-bit virtual address from the processor.

- Checks protection bits in the selected register as follows:

- --Read access: if read protect bit is on, generate a read violation trap.

- --Write access: if write protect bit is on, generate a write violation trap.

- --Execute access: if execute protect bit is on, generate an execute protection trap.

- --Indirect address access: if both execute and read protect are on, generate an indirect address protection trap.

This allows indirect addresses to be accessed in either read only or execute only pages.

- If no protection violation occurs, take the 7-bit physical page number from the selected VAT register, together with the nine least significant bits of the original virtual address, and initiate the appropriate memory access to the word addressed by the resulting 16-bit quantity.

- If a parity error occurs, generate an own memory parity error trap.

- Return the data read to the processor (read references only).

- Set the dirty bit for the page accessed (write reference only).

Memory references made through the VAT have a cycle time of approximately 1 microsecond, as opposed to the normal memory cycle time of 900 nanoseconds.

#### Drum Processor (DP)

The Drum Processor controls data exchanges between the AP memory (core) of the 2+2 System and the swapping memory (high data-rate drum).

<u>Data Transfer Characteristics</u>. All data transfers handled by the DP are 512-word pages. Associated with each page there is also an address word, a code word, and an integrity word, which assure data integrity and access control.

The characteristics and capabilities of the drum processor have been balanced to enhance overall system performance. The DP operates with a family of fixed-head drums with capacities ranging from 1/2 to 16 million 8-bit bytes. Average access time is 17 ms or 35 ms, depending on drum size.

Data transfer is carried out at sustained rates of up to 2 million bytes per second with burst mode transfers up to 4 million bytes per second. The controller features control word look-ahead to combine a contiguous sector transfer capability with list-driven command word chaining.

Control Characteristics. The DP communicates directly with the Control Processor (CP) by means of interrupts. This direct communication is initiated by the CP to cause the DP to examine its Current State Cell (CSC) Ø in core memory for a state change command.

The DP will send an interrupt to the CP when the DP has:

- 1. an interrupt condition encountered during data transfer.

- 2. an interrupt condition encountered during control word access.

Once initiated, via CP generated interrupt, the DP will examine the information contained in two predefined core locations in AP memory designated CSCØ and CSC1. Using this information, the DP then interprets its required mode of operation. When the RUN mode is designated, the CSC1 serves as a pointer to the core location of the initial Data Control Block (DCB) Ø-3. The DCB contains data transfer control information for a single data page. Thereafter, each DCB links with its successor by contiguous locations in a DCB list or by a special link pointer to a non-contiguous core location. The cycle continues until a Last DCB condition, or an interrupt condition capable of terminating the operation, is encountered.

The DP will always send an interrupt to the processor when it terminates operation. It may send interrupts at other times as defined by the DCB commands.

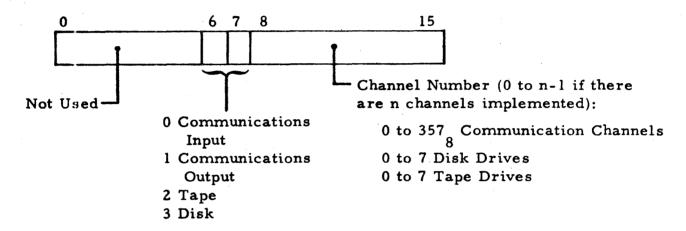

#### Peripheral Processor

The Peripheral Processor (PP) is a microprogrammed processor that controls disk, tape, and communication I/O functions, as specified by commands in CP memory. The three functions are effectively independent and can best be described separately.

<u>Disk Control</u>. The disk controller controls from 1 to 8 moving-head disk drives. The specifications for each disk drive are as follows:

| Number of heads                          | 20                                                       |

|------------------------------------------|----------------------------------------------------------|

| Number of cylinders (positions per head) | 200 (plus 3 spares)                                      |

| Number of tracks                         | $20 \times 200 = 4000$                                   |

| Sectors/track                            | 7                                                        |

| Total sectors                            | $7 \times 4000 = 28000$                                  |

| Seek time                                | 10 ms track to track,<br>45 ms average<br>75 ms maximum. |

| Rotation Period                          | 25 ms                                                    |

| Bit rate during transfer                 | 2.5 MHZ                                                  |

| Word transfer rate                       | 156.25 KHZ                                               |

The PP uses the same address verification, code word and integrity word checks as the DP to insure data protection and data validity.

Up to eight simultaneous seeks, or seven seeks and one simultaneous data transfer may be made. The software interface provides data and command chaining, with a single read or write command causing the transfer of precisely one page of data. Interrupts are sent to the CP when an error condition occurs, or when an interrupt is requested on command completion. Waiting interrupts are linked in a FIFO queue in CP memory.

Tape Control. The tape controller controls from one to eight magnetic tape drives, in any mixture of seven and nine track varieties. Standard IBM compatible tape drives are used, with a nominal tape speed of 37.5 ips, for a word transfer rate of 15 KHZ at 800 bits per inch. One data transfer at a time may be performed.

The software interface provides data and command chaining, with scatter/gather within a single record if desired. Interrupts are sent to the CP when an error condition occurs or when an interrupt is requested on command completion. Waiting interrupts are linked in a FIFO queue in CP memory.

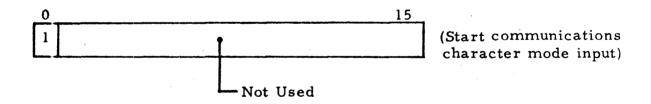

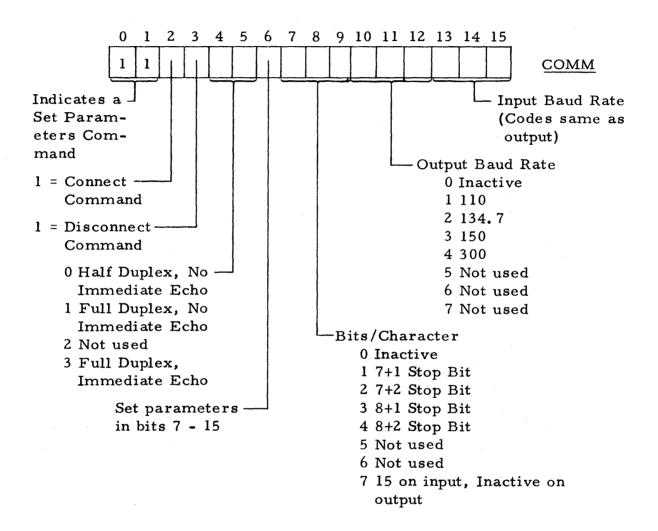

Communication Control. The communications input/output system controls up to 128 asynchronous and 16 synchronous lines. Asynchronous lines may be added in groups of 16; synchronous lines in groups of four.

Asynchronous lines are compatible with Bell 103A data sets at rates of 110, 134.7, 150, and 300 BAUD. Synchronous lines are compatible with 202 series data sets at rates of 2000, 2400, 4800, and 9600 BAUD.

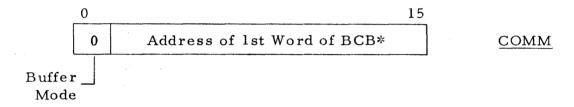

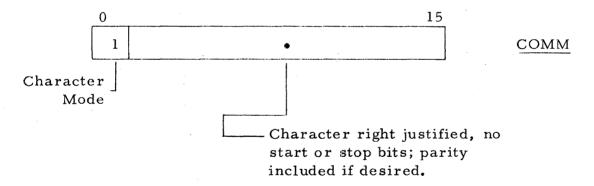

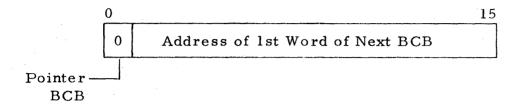

The software interface with the CP provides both character and buffer mode, full and half duplex, with data chaining in buffer mode. Waiting interrupts are linked in a first-in first-out (FIFO) queue for servicing in the proper order by the CP.

# III . . . Processor Organization

This section describes the basic organization of the Application Processor (AP) and the Control Processor (CP) in the LOGICON 2+2 System. Both processors are essentially identical in their physical characteristics and the information given in this section applies equally to understanding the internal organization of either the AP or the CP as hardware items.

#### REGISTERS

The programmable registers in the processors are described in the following paragraphs. All registers contain 16 bits, although the quantities stored in some registers may normally utilize fewer bits.

#### A = Accumulator Register

The primary accumulator in the machine. Arithmetic, logical and shift operations are performed directly on this register. It may be linked with U to form a 32-bit accumulator UA. It may be linked with U and E to form a 48-bit accumulator UAE.

#### U = Upper Accumulator Register

Some arithmetic, logical, and shift operations are performed directly on this register. In other cases, it is linked with the A register to form a 32-bit accumulator UA or with A and E to form a 48-bit accumulator UAE.

#### E = Exponent Register

Contains the exponent in floating point operations. The exponent is expressed as a 2's complement number. This register can be loaded from memory or other registers. It has very limited arithmetic and logical capabilities. It can be linked with the U and A registers to form a 48-bit accumulator UAE.

#### X = Index Register

Indexing may be performed on 15-bit word addresses, 16-bit byte addresses, or 16-bit 2's complement displacements. Arithmetic operations on this register do not affect the overflow or carryout status indicators.

#### P = Program Counter Register

This register generally contains the address of the next instruction to be executed. In forming relative addresses in basic instructions it contains the address of the current instruction. The register is 16 bits long but the addresses it contains are all 15-bit quantities.

#### B = Base of Stack Register

This register contains the 15-bit address of the base of the stack as seen by the main program or subroutine currently running. Attempts to "pop" the stack beyond this address will result in a stack underflow trap. If the high order bit is set, erroneous results may result from tests on B.

#### T = Top of Stack Register

This register contains the 15-bit address of the next word to be pushed into the stack. This address should not be less than the address contained in B nor greater than that contained in L as the result of a stack operation. Checks are made before the stack operation. Note that checks are made only in the appropriate direction (i.e., check for overflow on a "push," and underflow on a "pop").

#### L = Limit of Stack Space Register

This register contains the 15-bit address of the first word beyond the stack (i.e., the address of the first word the stack is not allowed to occupy). An attempt to "push" the stack beyond this address results in a stack overflow trap.

#### S = Status Register

Bits in this register describe the current status of the machine. Bit positions within the word are defined in this section under the discussion of Status Register.

#### REPRESENTATION OF INFORMATION

The binary system of notation is used throughout the LOGICON 2+2 System.

In the "fixed-point arithmetic" case of addition, subtraction, and comparison, operands and results are considered as binary numbers in 2's complement form. Subtraction, for example, is carried out internally by adding the 2's complement of the subtrahend.

The assumed location of the binary point has significance only for multiplication and division. For integer arithmetic, the binary point may be assumed to the right of the least-significant bit position (i.e., to the right of bit position 15); and for fractional arithmetic, the position of the binary point may be assumed to the left of the most-significant position (i.e., between bit positions 0 and 1).

Floating point numbers are stored with the mantissa in absolute value and sign, and the exponent stored in two's complement.

The processor is fundamentally organized to deal with 16-bit grouping of information. Special features are also included for ease of manipulating bits, bytes, and multiple words as groups. These bit groupings are used by the hardware and software to represent a variety of forms of information.

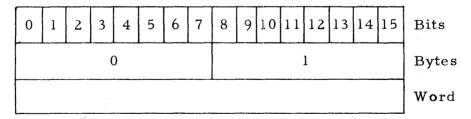

#### Machine Word

The machine word consists of 16 bits. The numbering of bit position, character positions, words, etc. increases in the direction of conventional reading from the most-to-least significant.

Data transfers between processor and memory are bit, byte, and word oriented as illustrated below.

#### Alphanumeric Data

Alphanumeric data are represented by 8-bit bytes. One machine word contains two bytes or characters. The character set used for most purposes is standard ASCII.

#### One Word Binary Integers

For the "algebraic" group of instructions, results are regarded as signed binary numbers, the leftmost bit being used as a sign bit (a 0 being plus and 1 minus). When the sign is positive all the bits represent the absolute value of the number; and when the sign is negative, they represent the 2's complement of the absolute value of the number. Overflow occurs when the magnitude of a number does not fit within a given word or register. That is, if the carryout of the sign position does not agree with the resultant sign (bit position), overflow has occurred. There are no conditions for underflow. A signed integer ranges from -2<sup>15</sup> through 2<sup>15</sup> - 1.

For the "logical" group of instructions, results are regarded as unsigned, positive binary numbers in the range of 0 through 2<sup>16</sup> - 1.

#### Three Word Binary Integers

The three word integers are sign magnitude, the left most bit of the first word is sign followed by 47 bits of magnitude. The range of three extended integers is from  $-(2^{47} - 1)$  through  $2^{47} - 1 = 140$ , 737, 488, 355, 327. Overflow occurs when the magnitude of a number does not fit within the 47 bits.

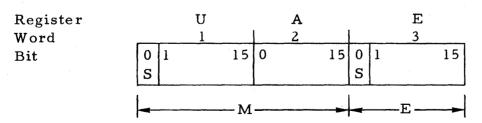

#### Three Word Binary Floating-Point Numbers

The instruction set contains instructions for binary floating-point arithmetic with numbers of two-word precision. The lower word represents the integral exponent E in 2's complement form, and the upper two words (32 bits) represent the fractional mantissa M in sign magnitude form. The notation for a floating-point number N is:

$$N = M \times 2^{E}$$

The three word format is shown below. S represents the sign bit.

Any number with an absolute value in the range of  $10^{-9863}$  through  $10^{9863}$  can be represented to more than nine significant decimal digits.

For normalized floating-point numbers, the binary point is placed at the left of the most significant bit of the mantissa. Numbers are normalized by shifting the mantissa (and adjusting the exponent) until no leading zeros are present in the mantissa.

7 To maintain accuracy, the lowest possible exponent (-32768) together with a zero mantissa has been defined as the machine representation of the number zero.

#### Four Word Binary Floating Point Numbers

These numbers are similar to the three word floating point with the exception of one more word of precision. This permits a number with an absolute value in the range of  $10^{-9863}$  through  $10^{9863}$  to be represented to more than 14 significant decimal digits. Arithmetic in this format is performed by software subroutines.

#### PROCESSOR FEATURES

#### Stack

The 2+2 processor includes three hardware registers that define a stack, or last-in first-out(LIFO) list structure. The registers are B (base of stack), T (top of stack) and L (limit of stack). The core storage locations making up the stack are (B) to (L-1) inclusive, and (T) is the address of the next word to be pushed into the stack.

Many 2+2 processor instructions push data into the stack (by storing data at the location in T and incrementing T) or pop data out of the stack (by decrementing T and reading data from the resulting location in T).

A subroutine call saves the current base of stack (B) value as well as (P), and resets B to the new value of T. This presents the subroutine with an empty stack insofar as any pushing or popping of entries is concerned. A subroutine return can then use this new value of B to restore the stack to the state it had at subroutine entry, even if T had not been restored to its initial setting.

System call, system return, trap entry, interrupt entry and interrupt return also use the stack mechanism, but reset B, T, and L to a special system stack while the system call, trap, or interrupt is being processed. When the processor is in user mode, the system stack is defined by a BASE location stored in memory location 4 of the system

address space, and a LIMIT location stored in location 5 of the system address space.

#### Skips and the Delayed Skip (DSK) Instruction

Many instructions allow conditional skips. All skips are skips of instructions rather than of words. Since instructions may be either one or two words long, skips are generated by reading up the next instruction and decoding it to determine whether it is a one-word instruction or the first word of a two-word instruction, then incrementing (P) by one or two.

#### CAUTION

Do not skip data words! If a data word is skipped, and it happens to have the format of a two-word instruction, then the word following it will also be skipped. If that is a one-word instruction, it will be skipped; if it is a two-word instruction, its first word will be skipped and the machine will try to execute its address.

If reading up an instruction to be skipped results in an execute violation or a parity error, the corresponding trap processor is entered at its second word, as shown:

| Trap Condition                | Transfers Control to:   |

|-------------------------------|-------------------------|

| Execute Violation             | (00032 <sub>8</sub> )   |

| Execute Violation During Skip | (00032 <sub>8</sub> )+1 |

| Parity Error                  | (00034 <sub>8</sub> )   |

| Parity Error During Skip      | (00034 <sub>8</sub> )+1 |

The Delayed Skip (DSK) instruction is used to force a skip, under program control. It is particularly useful for generating normal and exception returns from subroutines and system calls because it produces a true instruction skip, whereas incrementing the return address would produce a word skip. A DSK causes the instruction following the next instruction to be skipped; that is, the DSK does not affect the execution of the instruction immediately following it, but the instruction that would normally follow that one is skipped unconditionally. A DSK

can be used before any legal machine instruction except HLT, SCALL, CPRS or another DSK; if one is used preceding any of these instructions, it is ignored.

When a DSK is used before a conditional skip instruction - e.g., ACA, FCPS, MINC, SKXEI, etc. - the next instruction is skipped unconditionally, and if the skip condition was satisfied the one after that is also skipped. Thus, a DSK preceding a conditional skip instruction forces one extra skip. (This is the reason DSK is ignored before a CPRS instruction; the CPRS by itself can skip two instructions, and there is no provision in the processor for a skip of three instructions.)

When a DSK precedes an instruction that causes a transfer of control—e.g., JMP, JSPM, CALL, RTRN, SRTRN, etc.—the skip occurs after the jump, and the instruction jumped to is the one skipped. When a DSK precedes a conditional jump—e.g., JZE, XJP, TJP, etc.—the instruction skipped is either the one jumped to or else the one immediately following the jump instruction, depending on whether or not the jump condition is satisfied.

Traps and interrupts are essentially transparent to DSKs, even in those cases (e.g., floating point overflow and underflow) where the trap processor itself uses a DSK ahead of its SRTRN to skip over the instruction that caused the trap. If that instruction was preceded by a DSK, then the return will skip two instructions.

#### Processor Mode

The processor has two modes of operation, a System mode, used in Monitor programs, and a User mode, used by all programs running under control of the Monitor. The current mode of operation of the processor is indicated in bit 9 of the Status register (0 for system mode, 1 for user mode). The difference between modes and the ways of switching between modes are described in this section.

In System mode, all instructions including privileged instructions may be executed. On memory accesses made through the VAT, the system map is used. In User mode, an attempt to execute a privileged instruction will result in a privileged instruction execution trap. Memory references made through the VAT use the user map.

A system call (SCALL) instruction executed in User mode results in a transition to System mode. Furthermore, the user stack is "sealed off" and the stack registers are reset to use a system stack, defined

by locations stored in cells 4 (BASE) and 5 (LIMIT). Further system calls while in system mode continue to use the same system stack. As each system call is completed and control returned via a system return instruction, control eventually reverts to the original user mode code. At this point the processor status reverts to user mode, the system stack is abandoned, and use of the user stack resumed in the configuration it had at the time of the original system call.

An interrupt or trap occurring while in user mode similarly causes a transition to system mode, and to the system stack. The interrupt return or system return reverts to user mode and the user stack. Note that trap processing routines exit via the system return (SRTRN) instruction.

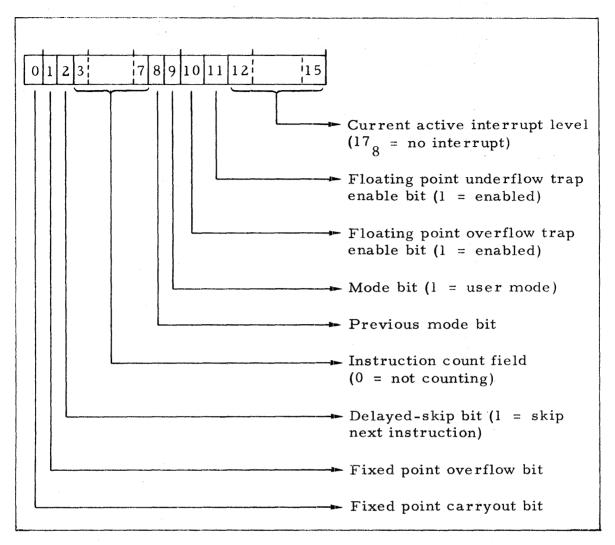

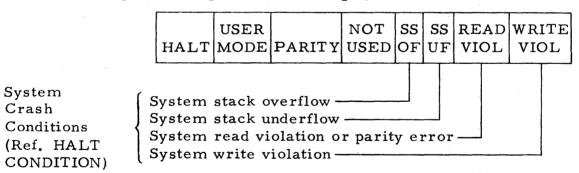

#### Status Register

The status register contains several items of information about the current state of the processor. Its format is as shown in Figure 3-1.

Fixed Point Carryout. This bit contains the carry or borrow from the high order (sign) bit position of the last fixed point add or subtract instruction affecting (A) or (U) executed, or zero if it has since been reset by a SKNCO (skip if no carry out) instruction.

Fixed Point Overflow. This bit contains a one if an arithmetic overflow has occurred since the last SKNOF (skip if no overflow) instruction. An overflow has occurred if the correct arithmetic result of an operation cannot be expressed in the register that the answer should go into. Note that overflow is not reset by arithmetic operations; it can only be set. Carryout may be either set or reset by arithmetic instructions.

Certain instructions are classified as being for primarily logical or address operations and do not effect overflow or carryout. The description of each individual instruction has this information. The general rules are as follows:

- Fixed point add and subtract operations on A and U, except for the interregister instructions RADD and RSUB, may affect carryout and overflow.

- Add and subtract to memory (ADDM, SUBM) may affect carryout and overflow, but MINC and MDEC do not.

Figure 3-1. Status Register Contents

- Fixed point division may set overflow.

- Fixed point multiply (MPA AND MPAS, but not MPX) sets overflow if the results will not fit in one register (this is an exception to the general definition of overflow).

- Arithmetic left shifts may set overflow.

Delayed-Skip Bit. When this bit is set on completion of an instruction, the instruction that would have normally been executed next is skipped, and the following instruction executed. This feature is used, for example, to give skip returns to system call instructions. Refer to description of "Skips and the DSK Instruction".

<u>Instruction Count Field</u>. The processor may be placed in a "trap after executing n instructions" mode for  $0 \le n \le 30$ . This field of the status register contains a number one greater than the count of instructions remaining before the trap. A count of zero means no trap is pending. This feature will be used primarily for debugging operations.

The count may be started by a system routine, by inserting a non-zero count in the saved status register location in the system stack, and then executing a system return instruction. This returns control to the calling routine with the instruction count set in the status register. The calling routine may execute exactly the indicated number of instructions, and then an instruction count trap will occur.

The following special comments apply to the implementation of the count mechanism:

- A system call counts as one instruction, independent of the number of instruction executions it may invoke.

- Interrupt routines are not counted.

- Many trap conditions repeat the instruction on which the trap occurred, following execution of the trap processor.

The instruction on which the trap occurred will be counted both on the aborted execution and the final execution. Trap processors must be written to correct for this condition.

- If a user program is swapped out while the count is in process, the count will be saved and resumed when that user is swapped in again. This feature is a property of the time sharing monitor and not of the processor hardware.

Mode and Previous Mode. Processor mode (0 = system, 1 = user) is stored in the status register. The previous mode bit is the state of the mode bit prior to the last system call, trap, or interrupt (i.e., in the routine that originally called the current system routine: not in a lower level routine that was called and returned control to the current routine).

Floating Point Trap Enable. Floating point overflow and underflow traps may be enabled and disabled by setting these bits. Note that they can be changed only by system code. When enabled, a floating point overflow (underflow) results in the corresponding trap.

A floating point overflow occurs when the result of a floating point operation is too large to be normalized (i.e.,

$$|R| > (1 - 2^{-31}) \times 2^{32767} \approx .708 \times 10^{9864}$$

).

A floating point underflow occurs when the result of a floating point operation is too small to be normalized (i.e.,

$$|R| < 1 \times 2^{-32769} \cong .353 \times 10^{-9864}$$

).

Current Interrupt Level. The current interrupt level is kept in the status register. It varies from 0 (highest priority) to 15 (lowest priority), with several states being effectively unused because of special hardware features. The state 15 is used to indicate 'no active interrupt.'

#### Traps, System Calls and Interrupts

Traps, system calls, and interrupts are very similar, the main differences between them being their causes. Traps are caused by the detection of internal error conditions, system calls are caused by the execution of SCALL instructions, and most interrupts are caused by external events which set bits in the external interrupt register. The exception is system stack overflow. This is an internal error, and as such ought to cause a trap, but to avoid conflicts it is made to cause an interrupt instead.

All system calls and most traps are always enabled, but two traps—floating point overflow and floating point underflow—can be enabled or disabled selectively by bits in the status register. When set to one, bit number 10 of the status register enables the floating point overflow trap, and bit number 11 enables the floating point underflow trap. Whether or not these traps are enabled, a floating point overflow always sets (U, A, E) to a very large floating point number (in octal: 077777, 000000, 077777), and a floating point underflow always sets it to a floating zero (in octal: 000000, 000000, 100000).

Most interrupts can be enabled or disabled selectively by using the SIM, SIL and RIL instructions. The SIL (Set Interrupt Lockout) instruction disables all interrupts except system stack overflow. The RIL (Reset Interrupt Lockout) instruction enables all interrupts allowed by the current interrupt mask. The interrupt mask is controlled

by the SIM (Set Interrupt Mask) instruction. At the beginning of each instruction, (before (P) is incremented) the interrupt mask is "anded" with the external interrupt register, and a check is made to see if there are any enabled interrupts, waiting to be honored, of higher priority than the current level as defined in the status register bits 12-15. The system stack overflow interrupt is, again, the exception. Since it is caused by an internal error rather than an external event it never appears in the external interrupt register, and therefore it cannot be disabled.

All traps and system calls, and all interrupts except the power-down interrupt, are processed as follows:

- 1. The VAT is set to system mode. This causes all subsequent memory references to use the system address space, regardless of the mode bit in the status register.

- 2. If the current status register mode bit indicates user mode, a transition to the system stack is made as follows:

- a. The contents of cells 00004 and 00005 are read out as the system stack BASE and LIMIT pointers, respectively.

- b. (B) is stored at the address given by (BASE), (T) is stored at (BASE)+1, and (L) is stored at (BASE)+2.

- c. B is set to (BASE), T is set to (BASE)+3, and L is set to (LIMIT).

This procedure establishes a new system stack, which will be used for all traps, system calls and interrupts as long as the machine remains in system mode.

3. Registers are saved in the system stack as follows:

The current status register (S) is stored at (T), (X) is

stored at (T)+1, (U) is stored at (T)+2, (A) is stored at

(T)+3, (E) is stored at (T)+4. If a trap or interrupt is being processed, (P) is stored at (T)+5; if a system call is

being processed, (P)+1 is stored at (T)+5. Thus a trap or

interrupt is set to return to the instruction where it occurred, and a system call is set to return to the next

instruction. (B) is stored at (T)+6.

- 4. B and T are both set to (T)+7.

- 5. If an interrupt is being processed,

- a. Its priority level is saved as the current interrupt lev-

- b. The current interrupt is acknowledged, thereby resetting the external interrupt line.

- c. The current interrupt level is stored in the low-order four bits (bits 12 15) of the status register, thereby disabling that level and all lower levels of interrupts.

- 6. The mode bit in the status register (bit number 9) is copied into the previous mode bit (bit number 8).

- 7. The status register is cleared except for the previous mode bit and the current interrupt level field (bits 12 through 15).

- 8. If a memory-related trap is being processed, X is set to the address where the error or violation occurred. In the AP, read write, execute and indirect reference violations, own-memory parity errors and indirect reference level overflows all produce mapped addresses in "specified map" form (i.e., the sign bit of (X) indicates which map was in use), but other-memory parity errors produce unmapped addresses. In the CP, all such traps produce unmapped addresses.

- 9. The appropriate dedicated cell is read and its contents are loaded into P. If a trap is being processed that resulted from an execute violation or own-memory parity error occurring during a skip, (P) is incremented by one.

- 10. If (T) > (L), (L) is incremented by 14 and a system stack overflow interrupt is generated; otherwise, normal execution resumes beginning at (P).

The dedicated transfer cell addresses for the various types of interrupts, traps and system calls are shown in Tables 3-1, 3-2, and 3-3.

TABLE 3-1. INTERRUPT ENTRY LOCATIONS (IN SYSTEM ADDRESS SPACE)

| Interrupt<br>Level | Octal Location<br>of Entry Address | Function                                            |

|--------------------|------------------------------------|-----------------------------------------------------|

| 0                  | 10                                 | Power down interrupt entry                          |

| 1                  | 11                                 | System stack overflow interrupt entry               |

| 2                  | 12                                 | Stall alarm interrupt entry (CP),<br>Unused (AP)    |

| 3                  | 13                                 | Drum interrupt entry (CP), Unused (AP)              |

| 4                  | 14                                 | Disk interrupt entry (CP), Unused (AP)              |

| 5                  | 15                                 | Communications interrupt entry (CP),<br>Unused (AP) |

| 6                  | 16                                 | Magnetic tape interrupt entry (CP),<br>Unused (AP)  |

| 7                  | 17                                 | Unused                                              |

| 8                  | 20                                 | Unused                                              |

| 9                  | 21                                 | Unused                                              |

| 10                 | 22                                 | Interprocessor interrupt #1 entry                   |

| 11                 | 23                                 | Interprocessor interrupt #2 entry                   |

| 12                 | 24                                 | Countdown clock interrupt entry                     |

It is particularly important to note that the trap, system call and interrupt processor does not behave like a typical stack instruction (e.g., PUSHM) with respect to stack overflows. If a stack overflow occurs the words are pushed in anyway, then (L) is incremented by 14 and a system stack overflow interrupt is generated, which itself pushes in 7 more words. Accordingly, when the system stack LIMIT pointer (cell 00005) is initialized it must be set to an address at least 14 words less than the last word actually available in the system stack's storage space.

This is why a system stack overflow must generate an interrupt instead of a trap. If it did generate a trap, the software routine that processes it might get interrupted before it has had time to extend the

TABLE 3-2. TRAP ENTRY LOCATIONS (IN SYSTEM ADDRESS SPACE)

| Tuen                                                                    | Octal Location of Entry Address | Notes                                                                                |

|-------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------|

| Trap                                                                    | of Entry Address                | Notes                                                                                |

| Read protection violation                                               | 00030                           | (X) = address. AP only.                                                              |

| Write protection violation                                              | 00031                           | (X) = address. AP only.                                                              |

| Execute protection violation                                            | 00032                           | <pre>(X) = address. AP only. Transfer is to (00032)+1 if detected during skip.</pre> |

| Indirect address protection violation (Both Read and Execute protected) | 00033                           | (X) = address. AP only.                                                              |

| Own-memory parity<br>error                                              | 00034                           | (X) = address.<br>Transfer is to<br>(00034)+1 if detected<br>during skip.            |

| Other-memory parity error                                               | 00035                           | <pre>(X) = other-memory address (unmapped).</pre>                                    |

| Illegal instruction                                                     | 00036                           |                                                                                      |

| Privileged instruction in user mode                                     | 00037                           |                                                                                      |

| Indirect reference<br>level overflow (more<br>than 8 levels)            | 00040                           | (X) = address of next level.                                                         |

| Stack overflow during user mode                                         | 00041                           |                                                                                      |

| Stack underflow during user mode                                        | 00042                           |                                                                                      |

| Floating point overflow                                                 | 00043                           | (U, A, E) = 077777,<br>000000, 077777.                                               |

TABLE 3-2. TRAP ENTRY LOCATIONS (IN SYSTEM ADDRESS SPACE) (Cont)

| Trap                          | Octal Location<br>of Entry Address | Notes                                  |

|-------------------------------|------------------------------------|----------------------------------------|

| Floating point under-<br>flow | 00044                              | (U, A, E) = 000000,<br>000000, 100000. |

| Instruction counter countdown | 00045                              | ·                                      |

TABLE 3-3. SYSTEM CALL ENTRY LOCATIONS (IN SYSTEM ADDRESS SPACE)

|           | System Call Number      |                         | Octal Location               |  |

|-----------|-------------------------|-------------------------|------------------------------|--|

| Processor | Decimal                 | Octal                   | of Entry Address             |  |

| CP        | 0<br>1<br>:<br>:<br>23  | 0<br>1<br>:<br>:<br>27  | 00050<br>00051<br>:<br>00077 |  |

| AP        | 0<br>1<br>:<br>:<br>255 | 0<br>1<br>:<br>:<br>377 | 00050<br>00051<br>:<br>00447 |  |

NOTE: System call numbers 24-255 are trapped as illegal instructions in the CP.

stack. This would result in another stack overflow and another, nested, trap. By making system stack overflow a very high priority interrupt, all other interrupts can be locked out while it is being processed.

However, there is one interrupt, power down, that must be of higher priority even than system stack overflow if it is to be processed in time. Since it must be able to interrupt the system stack overflow

processor, it cannot use the stack; accordingly, a power down interrupt is processed differently than any other interrupt, as follows:

- 1. The map is set to system mode.

- 2. The contents of cell 00010, the dedicated address pointer for external interrupt line number 0, are read out.

- 3. (P) is stored at the address given by (10).

- 4. The current status register is stored at (10)+1.

- 5. The mode bit in the status register (bit number 9) is copied into the previous mode bit (bit number 8).

- 6. The status register is cleared except for the previous mode bit. By setting the active interrupt level to zero, this disables all interrupts.

- 7. P is set to (10)+2.

- 8. Normal execution resumes beginning at (P).

#### NOTE

The only registers saved by a power down interrupt are (P) and status. It is up to the interrupt routine to save (X), (U), (A), (E), (B), (T) and (L).

Except for floating point overflow and floating point underflow, all error conditions that result in traps (or interrupts, in the case of system stack overflows) are detected before any changes sufficient to prevent restarting the instruction are made to either registers or memory cells. Thus, in most cases where the cause of the trap is something that can be fixed, the trap processor can fix it and then restart the instruction. When this is done, the fact that a trap occurred is essentially invisible to the instruction.

Processing of trap conditions and system cells is terminated by a SRTRN (system return) instruction. Processing of interrupts is

terminated by an IRTRN (interrupt return) instruction. These instructions operate in very nearly the same way:

- The T register is restored to the value it had at entry to the trap, system call, or interrupt processing routine:

(B)-7→T.

- All processor registers are restored from the stack:

```

((T))\rightarrow S

((T)+1)\rightarrow X [on SRTRN, only if XS bit set]

((T)+2)\rightarrow U [on SRTRN, only if US bit set]

((T)+3)\rightarrow A [on SRTRN, only if AS bit set]

((T)+4)\rightarrow E [on SRTRN, only if ES bit set]

((T)+5)\rightarrow P

((T)+6)\rightarrow B

```

Check for stack underflow:

If (B) > (T), generate stack underflow trap

• Restore B, T, L to user mode stack if a transition to user mode was made: If the mode bit in the status register is now 1, then

$$((T)-3)\rightarrow B$$

$((T)-1)\rightarrow L$

$((T)-2)\rightarrow T$ .

• In IRTRN, enable all interrupt levels allowed by the current interrupt mask, up to but not including the interrupt level being returned to.

#### Clock

The processor has a one millisecond real-time clock, used to furnish both a time-of-day clock and a countdown clock for interval timing. The time-of-day clock is a double precision (32 bit) quantity stored in memory locations 00001 (most significant) and 00002 (least significant) in system mode address space. It is incremented once every millisecond. Thus, cell two counts in a cyclic pattern, repeating every 65,538 milliseconds, and cell one counts with a least significant bit of 65.538 seconds. The time-of-day clock may be set by software to any desired starting value.

A countdown clock, stored in cell 00003 of system mode address space, is decremented once every millisecond. When it reaches zero, an interrupt is set (priority level 12) to software. If not reset by software, it will supply an interrupt every 65.538 milliseconds (counting from  $177777_8$  to 0).

#### Stall Alarm

The processor may be equipped with a stall alarm feature. This device furnishes an interrupt (priority 2) approximately one second after the last reset signal it receives from software. Thus, if not reset for a period of more than one second, it furnishes an interrupt that may be used to detect inadvertent program loops.

In the LOGICON 2+2 System, the CP is equipped with a stall alarm — the AP is not. The stall alarm is reset by executing a DOUT instruction with X = 036000.

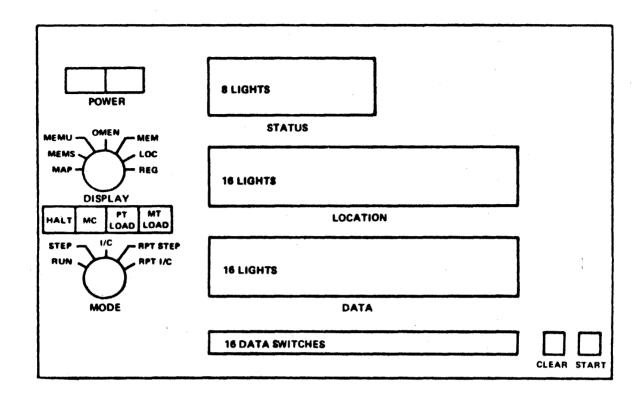

#### Programmer Panel (Prototype)

The prototype LOGICON 2+2 System uses two modified DSC model 4153 programmer's control panels as its programmer panel. After determination of requirements through use, these panels will be replaced with a single integrated system control panel. The physical layout of each of the panels is as shown in Figure 3-2.

One panel is connected to the Applications Processor (AP), and one to the Control Processor (CP). The lights and controls have the following functions:

- POWER: (CP only) Controls system power on/off.

- <u>DISPLAY</u>: Controls the display in LOCATION and DATA lights, and the interpretation of DATA switches, when the processor is halted.

- MODE: Determines the processor's response to an activation of the START switch.

Figure 3-2. Programmer Panel Layout

• STATUS LIGHTS: Display processor status when in halt. Light meanings are (left to right):

- LOCATION Lights: Display a 16-bit number that tells, in conjunction with the DISPLAY switch, what is being displayed in DATA Lights. Used during halt only.

- <u>DATA Lights</u>: Display a 16-bit number, as selected by the DISPLAY switch and an internal address register (which is displayed in LOCATION Lights). Used during halt only.

- DATA switches: A bank of 16 switches used to enter data into DATA Lights and thence into internal registers if desired. Also sampled by software via the load A from console (LDAC) instruction. Off or 0 in center position, or on 1 in momentary down or latching up positions.

- <u>CLEAR</u>: Causes the register driving DATA Lights to be cleared, used in data entry during halt mode only.

- START: Causes an action determined by the MODE switch.

Used during halt only.

- <u>HALT</u>: Generates an interrupt to the processor that causes it to enter the halt mode.

- MC: Sends a master clear to the I/O system, clears all internal registers (P, A, E, U, X, B, T, L, and STATUS).

- PT LOAD: Bootstrap load from paper tape, setting P to an address specified on tape. PARITY light activated if a checksum occurs. (CP only.) The format of a paper tape for Bootstrap load is shown in Appendix A.

- MT LOAD: Magnetic tape bootstrap, into page ∅ of system memory, setting P to contents of cell ∅. PARITY light activated if checksum error occurs. The format of a magnetic tape record for Bootstrap load is shown in Appendix A.

The data displayed in the LOCATION and DATA light registers is controlled by the DISPLAY switch as follows:

- MAP, display addressed map cell. (AP only)

- MEMS, display addressed cell in own memory using system map. (Mapped in AP, unmapped in CP)

- MEMU, display addressed cell in own memory using user map. (Mapped in AP, unmapped in CP)

- OMEN, display addressed cell in other memory.

- MEM, display addressed cell in own memory using map corresponding to processor mode. (Mapped in AP, unmapped in CP)

- LOC, display LOCATION register used in memory and map display.

- REG, display register selected by DATA switches:

| BIT | REGISTER       |

|-----|----------------|

| 0   | Р              |

| 1   | X              |

| 2   | U              |

| 3   | Α              |

| 4   | E              |

| 5   | В              |

| 6   | T              |

| 7   | L              |

| 8   | STATUS         |

| 9   | INTERRUPT MASK |

Entry of data is controlled by the DATA and CLEAR switches. The displayed data is in DATA Lights, and the address of the data is in LOCATION Lights. In all display modes except REGISTER, the DATA and CLEAR switches may be used to modify the displayed data: The DATA switches are logically "ored" bit by bit into the DATA light register. All bit positions not held on by activated DATA switches may be cleared by the CLEAR switch.

An activation of the START switch when the MODE switch is in inspect and change (I/C) has the following effect on display:

- MAP or memory display:

DATA Lights addressed cell, increment address, display new address and contents

- LOC display