# Causal and Teleological Reasoning In Circuit Recognition

Johan De Kleer

MIT Artificial Intelligence Laboratory

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

| REPORT DOCUMENTATION PAGE                                                   |                                | READ INSTRUCTIONS BEFORE COMPLETING FORM      |  |

|-----------------------------------------------------------------------------|--------------------------------|-----------------------------------------------|--|

| 1. REPORT NUMBER                                                            | 2. GOVT ACCESSION NO.          | 3. RECIPIENT'S CATALOG NUMBER                 |  |

| AI-TR-529 -                                                                 |                                |                                               |  |

| 4. TITLE (and Subtitle)                                                     |                                | 5. TYPE OF REPORT & PERIOD COVERED            |  |

| Causal and Teleological Reason                                              | ing In Circuit                 | Technical Report                              |  |

| Recognition                                                                 |                                | £ BEREALING OR DESCRIPTION                    |  |

|                                                                             |                                | 6. PERFORMING ORG. REPORT NUMBER              |  |

| 7. AUTHOR(e)                                                                |                                | 8. CONTRACT OR GRANT NUMBER(a)                |  |

| Johan de Kleer                                                              |                                | N00014-75-C-0643                              |  |

| Johan de Rieer                                                              |                                | MCS77-04828                                   |  |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS                                 |                                | 10. PROGRAM ELEMENT, PROJECT, TASK            |  |

| Artificial Intelligence Laborato                                            |                                | AREA & WORK UNIT NUMBERS                      |  |

| 545 Technology Square                                                       | Ť                              |                                               |  |

| Cambridge, Massachusetts 02139                                              |                                |                                               |  |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                                     |                                | 12. REPORT DATE                               |  |

| Advanced Research Projects Agency<br>1400 Wilson Blvd                       | y l                            | September 1979                                |  |

| Arlington, Virginia 22209                                                   | •                              | 13. NUMBER OF PAGES                           |  |

| 14. MONITORING AGENCY NAME & ADDRESS(If differen                            | t from Controlling Office)     | 216 18. SECURITY CLASS. (of this report,      |  |

| Office of Naval Research                                                    |                                | UNCLASSIFIED                                  |  |

| Information Systems                                                         |                                |                                               |  |

| Arlington, Virginia 22217                                                   |                                | 154. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE |  |

| 16. DISTRIBUTION STATEMENT (of this Report)                                 |                                |                                               |  |

| Distribution of this document is unlimited.                                 |                                |                                               |  |

|                                                                             |                                |                                               |  |

|                                                                             |                                |                                               |  |

| 17. DISTRIBUTION STATEMENT (of the abetract entered                         | in Block 20, if different from | n Report)                                     |  |

|                                                                             |                                |                                               |  |

|                                                                             |                                | I                                             |  |

|                                                                             |                                |                                               |  |

| 18. SUPPLEMENTARY NOTES                                                     |                                |                                               |  |

| None                                                                        |                                | i                                             |  |

| None                                                                        |                                |                                               |  |

|                                                                             |                                |                                               |  |

| 19. KEY WORDS (Continue on reverse side if necessary an                     |                                |                                               |  |

| Causal Reasoning Tr bleshooting                                             |                                |                                               |  |

| Qualitative Reasoning Qualitative Simulation                                |                                |                                               |  |

| Electronics Teleology Circuit Design                                        |                                |                                               |  |

| Circuit Design Circuit Recognition                                          |                                |                                               |  |

| 20. ABSTRACT (Continue on reverse side if necessary and                     | i identify by block number)    |                                               |  |

| This thesis presents a theory of human-like reasoning in the general domain |                                |                                               |  |

| of designed physical systems, and                                           |                                | -                                             |  |

DD 1 FORM 1473

aspect of the theory, causal analysis, describes how the behavior of

individual components can be combined to explain the behavior of composite systems. Another aspect of the theory, teleological analysis, describes how the notion that the system has a purpose can be used to aid this causal analysis. The theory is implemented as a computer program, which, given a

# Causal and Teleological Reasoning

In Circuit Recognition

by

Johan de Kleer

Massachusetts Institute of Technology September 1979

This report is a revised version of a dissertation submitted to the Department of Electrical Engineering and Computer Science on January 10, 1979 in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

This report describes research done at the Artificial Intelligence Laboratory of the Massachusetts Institute of Technology. Support for the laboratory's artificial intelligence research is provided in part by the Advance Research Projects Agency of the Department of Defense under Office of Naval Research contract N00014-75-C-0643 and in part by National Science Foundation Grant MCS77-04828.

## ABSTRACT

This thesis presents a theory of human-like reasoning in the general domain of designed physical systems, and in particular, electronic circuits. One aspect of the theory, causal analysis, describes how the behavior of individual components can be combined to explain the behavior of composite systems. Another aspect of the theory, teleological analysis, describes how the notion that the system has a purpose can be used to aid this causal analysis.

The theory is implemented as a computer program, which, given a circuit topology, can construct by qualitative causal analysis a mechanism graph describing the functional topology of the system. This functional topology is then parsed by a grammar for common circuit functions. Ambiguities are introduced into the analysis by the approximate qualitative nature of the analysis. For example, there are often several possible mechanisms which might describe the circuit's function. These are disambiguated by teleological analysis. The requirement that each component be assigned an appropriate purpose in the functional topology imposes a severe constraint which eliminates all of the ambiguities. Since both analyses are based on heuristics, the chosen mechanism is a rationalization of how the circuit functions, and does not guarantee that the circuit actually does function. This type of coarse understanding of circuits is useful for analysis, design and troubleshooting.

#### **ACKNOWLEDGEMENTS**

I would like to express my thanks to all of the people v ho encouraged and aided me in this work:

- Gerald J. Sussman, my thesis supervisor, for providing guidance when I needed it, and for an endless series stimulating arguments;

- John S. Brown, for his constant excitement about what I was doing, and for helping me articulate my ideas when I did not know what they were;

- Marvin Minsky, for providing the intellectual point of view that made this type of research possible, and for being an insightful reader;

- Patrick H. Winston, my second reader, for his contribution to the organization of the thesis, and for his effort to maintain the environment where this research was possible;

- Seymour Papert, for first suggesting that I examine how people reason about physical systems; Ira Goldstein, for supporting my investigation into how students reason about simple mechanics;

- Ken Forbus, for reading unreadable first drafts and giving useful comments, and for believing that envisioning is important;

- Jon Doyle, for reading early drafts;

- Gerry Roylance, for reading early drafts, and for knowing more Electrical Engineering than I do;

- Ray Reiter, for first suggesting that I study artificial intelligence, but who probably did not expect that I would write a thesis like this one;

- Marilyn de Kleer, for contributing to the presentation, for putting up with my randomness, and for forcing me to remain a real person while I was working on the thesis.

# TABLE OF CONTENTS

| 1   | INTRODUCTION                                            |    |

|-----|---------------------------------------------------------|----|

| 1.1 | The Thesis                                              | 1  |

| 1.2 | Scenario                                                | 3  |

| 1.3 | Reader's Guide                                          | 8  |

| 1.4 | Methodology                                             | 10 |

| 1.5 | The Engineering Problem Solving Project at MIT          | 13 |

| 1.6 | Other Related Work                                      | 15 |

| 2   | OVERVIEW AND BACKGROUND                                 |    |

| 2.1 | The Overall Recognition Process                         | 18 |

| 2.2 | Causal Analysis                                         | 20 |

| 2.3 | Function Extraction                                     | 25 |

| 2.4 | Parsing                                                 | 27 |

| 2.5 | *Propagation of Constraints Applied to Circuit Analysis | 29 |

| 3   | THEORETICAL FOUNDATIONS                                 |    |

| 3.1 | Chapter Outline                                         | 36 |

| 3.2 | Points of View and Levels of Detail                     | 36 |

| 3.3 | Envisioning and Rationalization                         | 37 |

| 3.4 | Causality and Constraint                                | 40 |

| 3.5 | Teleology                                               | 44 |

| 4 CAUSAL REASONING                                     |     |

|--------------------------------------------------------|-----|

| 4.1 Causal Explanations of Circuit Behavior            | 47  |

| 4.2 Causality is an Artifact                           | 49  |

| 4.3 The Machinery for Causal Analysis                  | 50  |

| 4.4 Electrical Device Models                           | 53  |

| 4.5 Analysis of a DTL-Inverter                         | 57  |

| 4.6 The KVL Connection Heuristic                       | 62  |

| 4.7 The KCL Connection Heuristic                       | 65  |

| 4.8 Example IQ Analyses                                | 67  |

| 4.9 Quiescent Analysis                                 | 71  |

| 4.10 Recognition and Rationalization                   | 74  |

| 4.11 Capacitance and Elapsed Time                      | 79  |

| 4.12 The Relationship Between Causality and Constraint | 84  |

| 5 INTERPRETATIONS                                      |     |

| 5.1 Points of View on Circuit Behavior                 | 86  |

| 5.2 Measurement Interpretations                        | 87  |

| 5.3 Fault Localization                                 | 93  |

| 5.4 Intrinsic and Extrinsic Descriptions of Behavior   | 100 |

| 5.5 Causal Interpretations                             | 101 |

| 5.6 Computing Interpretations                          | 103 |

| 5.7 The Causal Cranh                                   | 105 |

| 6   | FEEDBACK -                                 |     |

|-----|--------------------------------------------|-----|

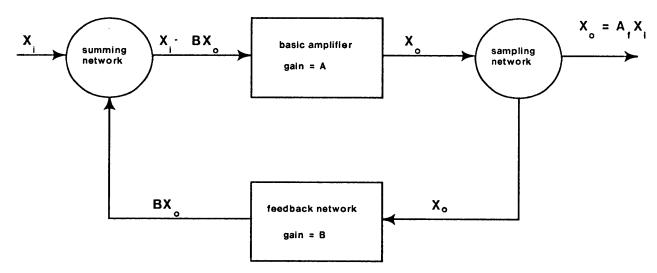

| 6.1 | Feedback is a Global Mechanism             | 110 |

| 6.2 | The Feedback Graph                         | 111 |

| 6.3 | Feedback Configurations                    | 113 |

| 6.4 | Sample Feedback Analyses                   | 118 |

| 6.5 | Local Feedback and Reflections             | 121 |

| 6.6 | Non Signal-Processing Feedback Circuits    | 125 |

| 6.7 | Regenerative Circuits                      | 131 |

| 6.8 | The Feedback Analysis Process              | 135 |

| 6.9 | Feedback and Constraint                    | 140 |

| 7   | TELEOLOGY                                  |     |

| 7.1 | The Teleological Perspective               | 141 |

| 7.2 | 2 Designed Artifacts and Natural Systems   | 141 |

| 7.3 | Explanation, Proof and Rationalization     | 142 |

| 7.4 | Design                                     | 145 |

| 7.5 | Teleology and Calculus                     | 146 |

| 7.6 | A Taxonomy of Implementation Purposes      | 148 |

| 7.7 | 7 Amplifier Recognition                    | 155 |

| 7.8 | 3 Disambiguating Interpretations           | 162 |

|     | Positive and Negative Purpose Descriptions |     |

|     | 10 *Applications to SVN                    |     |

# viii TABLE OF CONTENTS

| 8 ABSTRACTION                           |     |

|-----------------------------------------|-----|

| 8.1 Bottom-Up Abstraction Teleology     | 171 |

| 8.2 *Voltage and Current Sources        | 173 |

| 8.3 *Complex Amplifiers                 | 176 |

| 8.4 *Power-Supplies                     | 180 |

| 8.5 *Summary of the Recognition Process | 183 |

| 9 CONCLUSION                            |     |

| 9.1 Summary                             | 191 |

| 9.2 Future Research I                   | 192 |

| 9.3 Further Research II                 | 195 |

| 9.4 Design                              | 197 |

| REFERENCES                              | 198 |

| APPENDIX 1                              | 204 |

## Chapter 1

#### INTRODUCTION

#### 1.1 The Thesis

This thesis presents a theory of human-like reasoning in the general domain of deliberately designed physical systems. Formal quantitative theories have been developed to explain the behavior of electrical and mechanical systems, but these theories bear little resemblance to the informal qualitative reasoning of humans. For example, Network Theory is very powerful and general, but an engineer only uses it as a last resort, and then only to restricted subproblems. Most of the time he employs informal and qualitative techniques. The generality and apparent simplicity of the quantitative theories originate from their use of mathematics. People are very bad at the kind of symbol manipulation required by these theories. Instead they employ a variety of strategies to reason about engineered systems. This research develops a computational theory of two of the fundamental strategies observed in human reasoning about electrical circuits, envisioning and teleological reasoning.

Envisioning is a qualitative simulation of the system under study. The result of the envisioning is a mechanistic argument consisting of a sequence of events occurring in the functioning of the physical system where each event can be causally related to events earlier in the sequence. Each event is an assertion about some behavioral parameter of some constituent of the system (e.g. a change of current through a transistor). Although this apparent causality imposes a temporal order on the events, there need not be any actual time flow involved. The temporal order and the assignment of causality are entirely in the mind of the understander which need have little to do with what is actually the case. Nevertheless this rather mythical understanding is crucial in reasoning about physical systems. Elementary questions about a system's behavior can be answered directly by envisioning, and the mechanistic argument provides the foundation for more sophisticated reasoning about a system.

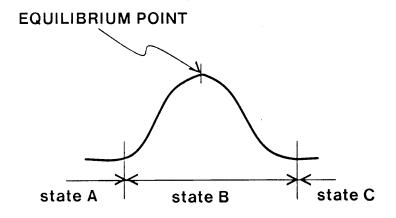

Since qualitative simulation describes behavior in only limited detail, it discovers multiple

2

mechanistic arguments for the same system. In deliberately designed systems the intended overall behavior, or teleology, can be used to resolve the ambiguity. The correct argument is the one which exhibits the intended behavior. Constituent objects of designed systems are grouped together in particular ways so that the purpose of the system is achieved. Since electrical circuits have been studied extensively, a fairly complete taxonomy of these groupings and their purposes has been developed. Knowledge of this taxonomy aids in resolving the ambiguities since those event sectiences which cannot be accounted for by this taxonomy are probably incorrect.

Envisioning and teleological reasoning are only two aspects of the strategies humans use to reason about physical systems. However, these two are sufficient to explain a wide range of phenomena.

The central aim of this research is the development of a calculus for the causal reasoning involved in envisioning and an associated calculus for teleological reasoning. These two calculi and their interaction are explored in the context of recognition. The task of recognition is to determine, from a description of the structure of a system, a description of the mechanism by which the system achieves its behavior. Electrical engineering has a formal language for representing electrical systems: the circuit schematic. Since electrical engineering does not have a formal representation for mechanisms, I will develop an ontology for the representation of mechanisms that is consistent with the current engineering literature. Since the central goal of this research is to study causal and teleological reasoning and not recognition, the recognizer built on the calculi never reasons in terms of the topology or geometry of the circuit itself. Recognition thus serves as a task to evaluate the informative content of the two calculi. Although topological pattern matching, as well as geometry, certainly plays a role in human recognition of circuits, any recognizer built solely on topological pattern matching will ultimately fail. (Chapter 2 presents a detailed argument of this.)

The circuits considered for recognition are amplifiers, logic gates and regulated power supplies. The recognition focuses on the dc behavior of these circuits and ignores the ac and transient aspects; thus rf amplifiers or switching power supplies are not considered. Applications to analysis, troubleshooting and design will be evident.

Success on the recognition task is determined by whether circuits can be identified and whether the explanations for the circuits' behavior are similar to those an engineer would give. Another test of the plausibility of envisioning and teleology is how complex a recognition mechanism based on them must be. Electrical circuits have been studied for a long time and, as a consequence, have a great deal of structure. The theory of qualitative reasoning presented here must tie directly into this structure. Current analysis, troubleshooting and design programs face difficulties which originate from their inability to understand circuit behavior at a more qualitative level. The theory of qualitative reasoning developed here should help these programs overcome their difficulties.

The remaining sections of this chapter consist a scenario, a reader's guide, a presentation of my methodology, and a discussion of related work. Chapter 2 presents an overview of a recognition process, and chapter 3 discusses the theory underlying it. Chapter 3 makes little reference to electronics, and the overview in chapter 2 can be understood without dealing with the electrical details. I suggest that the reader who knows no electronics quickly skim the remainder of chapter 1 and read chapter 3, followed by chapter 2.

#### 1.2 Scenario

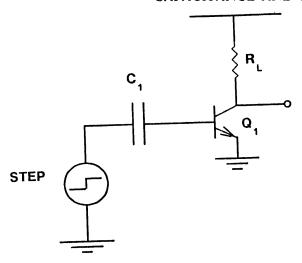

I have constructed a program QUAL based on envisioning and teleological reasoning which recognizes circuits. QUAL is written in Maclisp and can run on both the Artificial Intelligence Laboratory's PDP-10 and the Greenblatt Lisp Machine [Weinreb & Moon 79]. QUAL is completely working and has been run on hundreds of examples. Unless otherwise indicated, every part of the theory has been implemented. The program generated every example without any direct assistance from me. The following three scenarios illustrate some of its current capabilities.

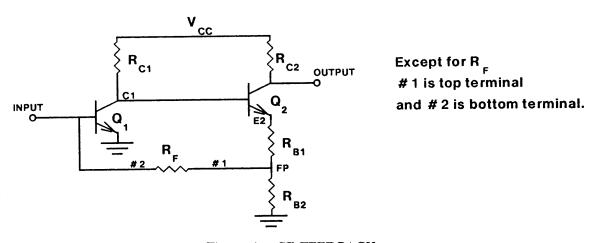

The circuit schematic is presented as an unannotated topological description and is accompanied with a notation indicating the relevant input and output quantities of the circuit. If the goal of the recognition was to determine the type of the circuit (e.g. "amplifier"), this notation of the input-output quantities essentially characterizes circuit's type. However, QUAL's goal is to determine the mechanism by which that amplifier amplifies, not just that the circuit is an amplifier. Although the examples are presented in part via an English dialogue, QUAL has no natural language input-output capability. The data structures that QUAL constructs to describe circuit behavior are too complex to present in this introduction. Hence I will take the liberty of summarizing these in English (later in the thesis, the actual data structures that QUAL constructs will be presented).

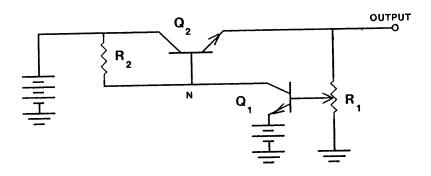

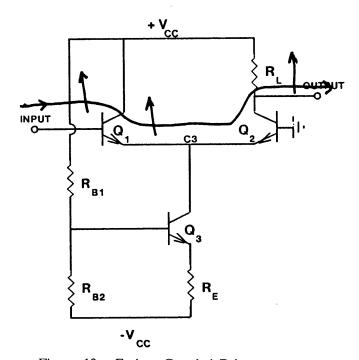

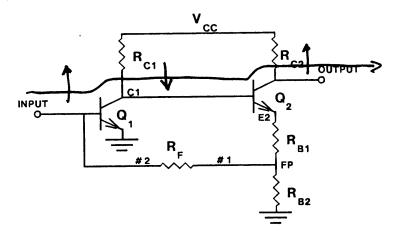

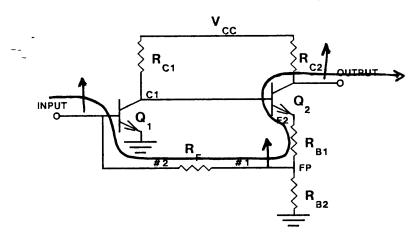

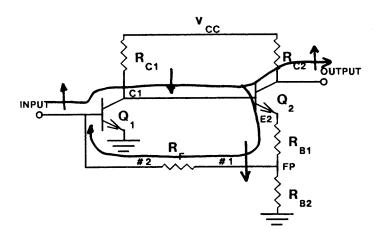

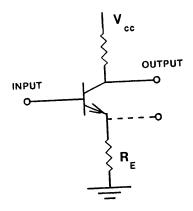

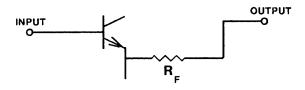

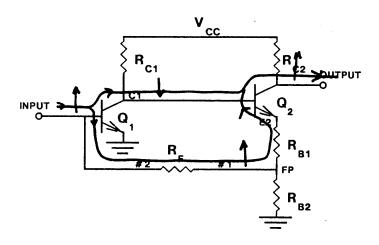

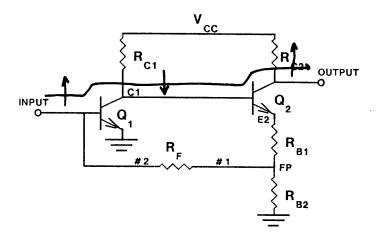

The first circuit is a simple feedback amplifier. The following description is all that QUAL is told about the amplifier and the Lisp description is only included to show exactly what QUAL

is told about the circuit it is to recognize.

```

SCENARIO 1:

(circuit: ce-feedback

nodes: (vcc ground b1 c1 output e2 fp)

devices: ((q1 (npn-transistor emitter: ground base: b1 collector: c1))

(q2 (npn-transistor emitter: e2 base: c1 collector: output))

(rc1 (resistor vcc c1))

(rc2 (resistor vcc output))

(rb1 (resistor e2 fp))

(rb2 (resistor fp ground))

(rf (resistor fp b1))

(input (terminal b1))

(output (terminal output))

(common (terminal ground))

(supply (battery vcc ground)))

(current input)

input:

(voltage output ground))

output:

OUTPUT

INPUT

```

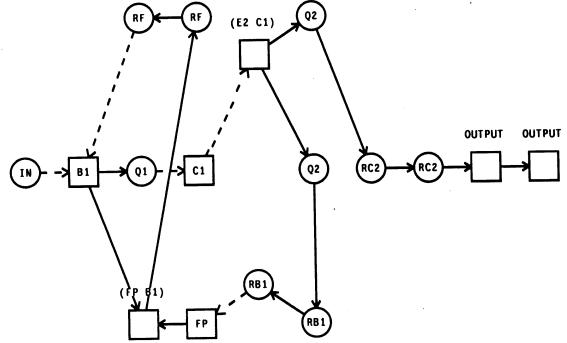

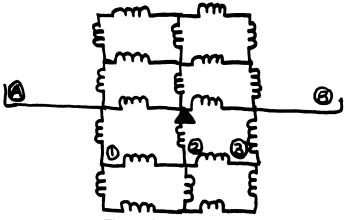

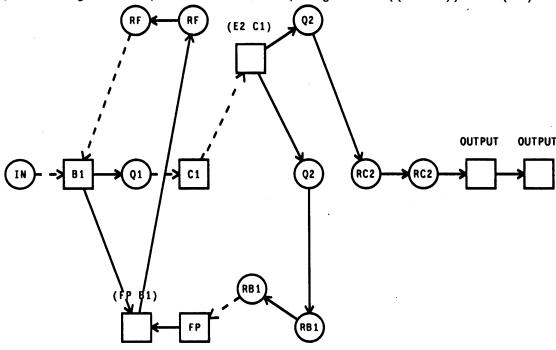

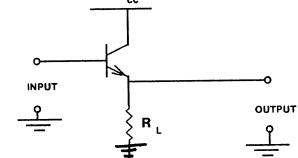

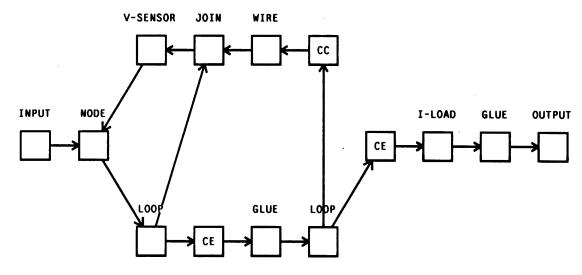

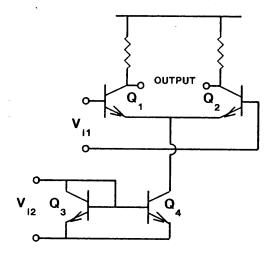

Figure 1: Schematic for CE-FEEDBACK

I have followed standard electrical conventions for naming devices and nodes, but QUAL does not utilize these hints embedded in the symbol names. For example, RF is a Feedback

Resistor, RC1 is the Collector Resistor for Q1, VCC is the main Voltage source, RB1 is Bias Resistor 1, node C1 is tied to the Collector of Q1, and node FP is a Feedback Point. A more complete program would detect these hints as well as use geometric and topological information. Node VCC or device RB1 could have be named G0001 and G0002 without having any effect on QUAL's ability to recognize the circuit.

The dialog commences with QUAL's description of the circuit's behavior. QUAL produces its explanations in a formal language which I abridge and summarize here for readability. The scenarios are included here to be suggestive of QUAL's reasoning ability, and not of any natural language or question answering capabilities. Hence, these descriptions may seem a little terse to one not familiar with electrical circuits. When the QUAL's determination these explanations is presented in subsequent chapters, the electrical details of the dialogs will become clearer.

The circuit is a noninverting amplifier with high power gain. It has a low input impedance and high output impedance. The feedback action tends to stabilize the circuit's current gain.

What is the purpose of RC1?

RC1 is the load for Q1 which is functioning in the common-emitter configuration.

What is the purpose of RF?

RF couples the output signal to the input. Without it the circuit would not exhibit feedback.

Describe the feedback path.

The input signal is first amplified by a common-emitter stage. Q2 functions as a common-collector stage coupling the output current through RBI and RF back to the input. This feedback samples the output current and compares this to the input current, thereby causing the amplifier to have stable current gain, higher output impedance and lower input impedance.

What contributes to the circuit's power gain?

The cascaded common-emitter stages exhibit both current and voltage gain. Therefore the circuit has power gain.

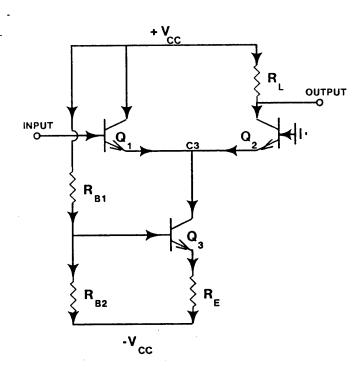

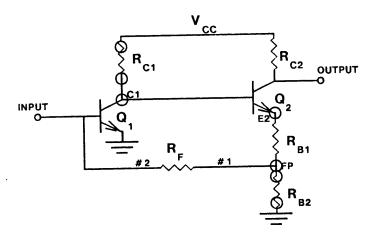

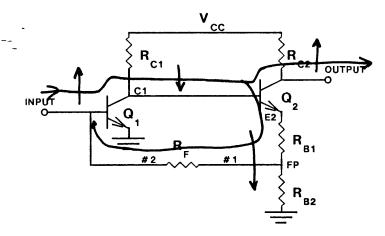

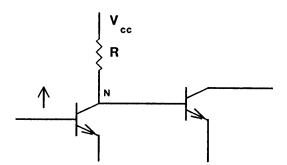

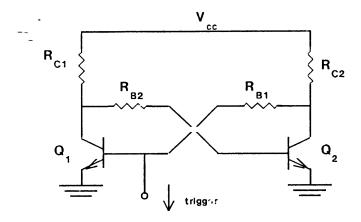

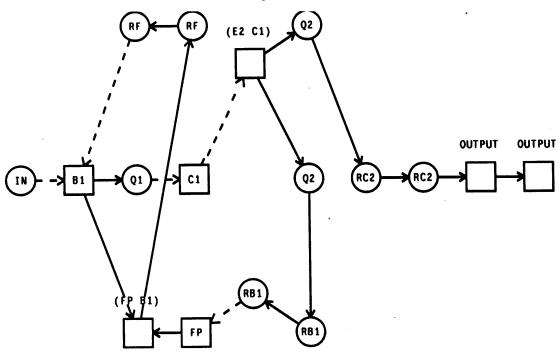

# SCENARIO 2:

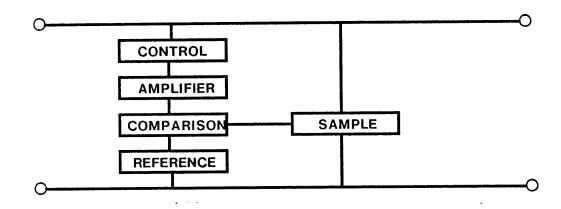

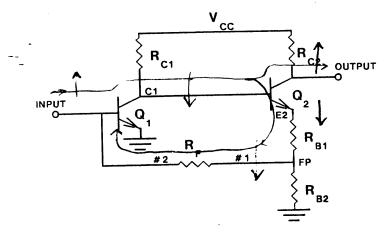

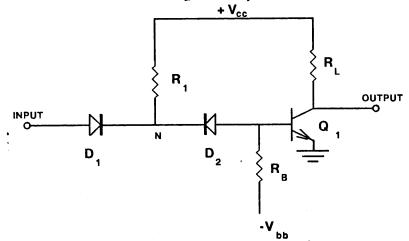

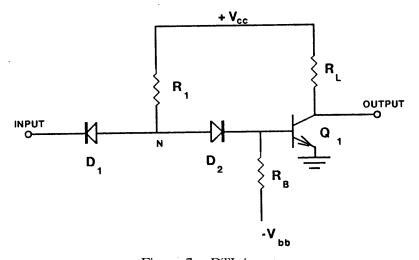

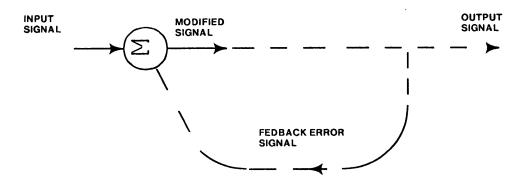

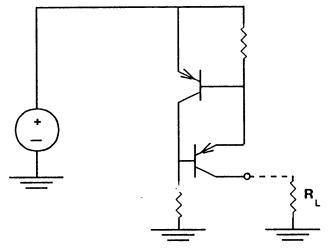

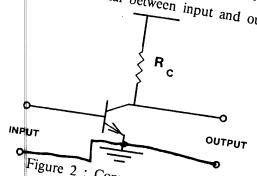

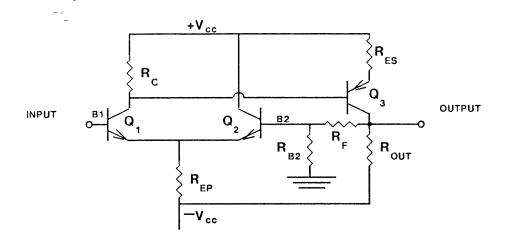

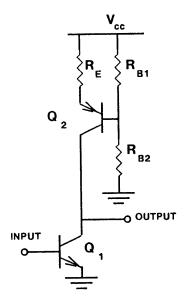

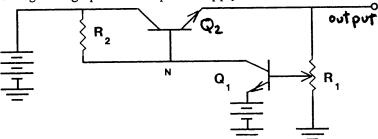

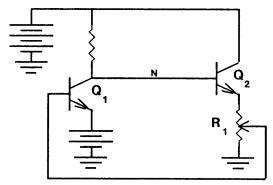

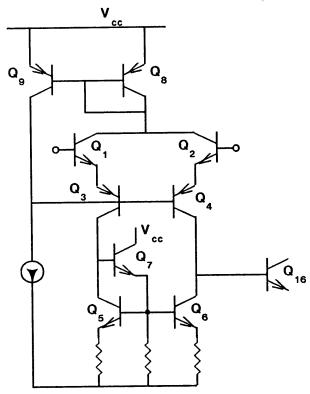

In order to recognize this circuit QUAL must be told that the input signal is the changing current to the load, and that the output signal is the voltage delivered to this load. QUAL then tries to identify the mechanism by which the circuit strives to have no incremental output and recognizes this mechanism to be a series-pass regulator.

Figure 2: Simple Power Supply

What kind of power supply is this?

A series-pass feedback regulator.

Describe how the feedback action regulates the output voltage.

Suppose the output voltage drops. This signal is coupled through R1 to Q1. Q1 compares this to the reference and begins to turn off. This increases the base drive to the seriespass element which then delivers more current to the load.

These explanations result from a combination of two very different descriptions QUAL constructs for the circuit's behavior. One description is purely causal: "The output voltage drops, causing the voltage at the base of Q1 to drop. Since the emitter of Q1 is held fixed, the base-emitter voltage of Q1 drops. This begins to turn off Q1 and lowers its collector current. As a consequence the voltage at node N rises. This causes the base-emitter voltage of Q2 to increase more than it normally would. As a consequence the output current rises." The teleological

description uses such concepts as "couple, compare, series-pass element." People do not distinguish between these two aspects of explanation and intermingle them in their explanations. Although QUAL has strategies to generate such intermingled explanations, its explanations are very crude. I constructed the text of the scenarios by starting with QUAL's crude explanation and augmenting them with other information in QUAL's data-base.

QUAL cannot generate these explanations. It knows a sufficient amount about the causality and teleology of the circuit's it recognizes to derive these explanations, but it cannot combine them into an elegant explanation. The problem of balancing how much teleology and causality to include in an argument depends on how much electronics the hearer knows. For example, if the hearer is unfamiliar with power supplies he will not understand "series-pass element." The problem of generating an appropriate explanation from a complete description of the system being explained is the subject of other research. The explanations QUAL constructs are comprehensible, but not as satisfying as possible. QUAL could far more easily be extended to a recognizer of explanations of circuit behavior than a generator of good explanations of circuit behavior.

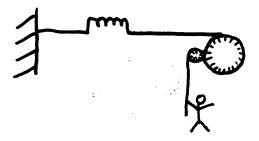

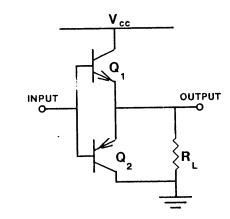

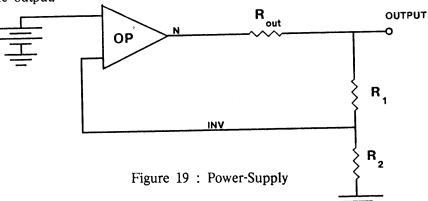

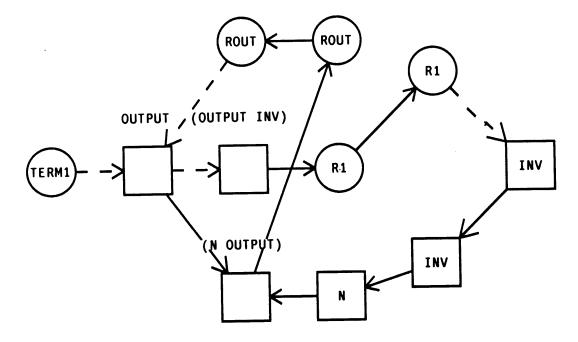

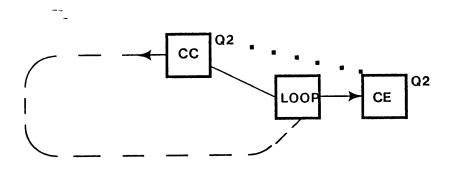

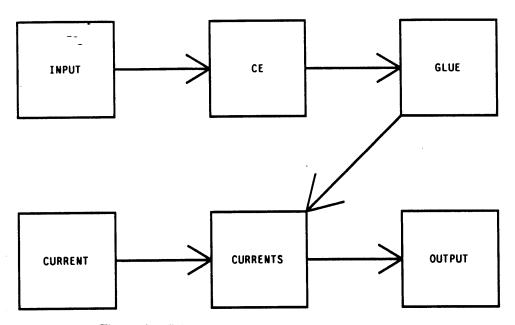

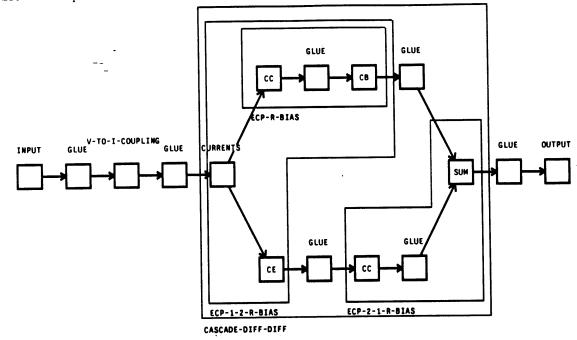

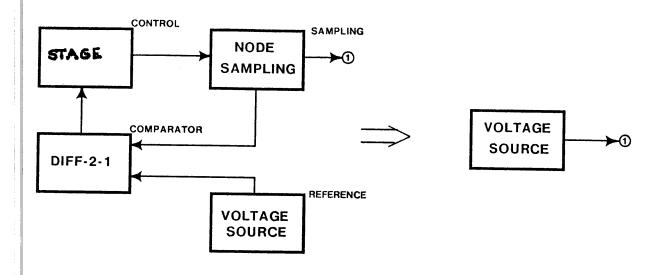

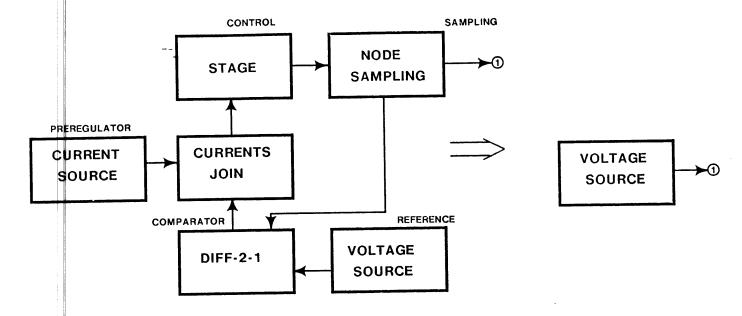

Teleology provides a method of grouping components by purpose. This final example illustrates the use of abstraction in recognizing a complex power supply. Figure 3 is block diagram for the simple power supply of figure 2:

Figure 3: Block Diagram for Power Supply

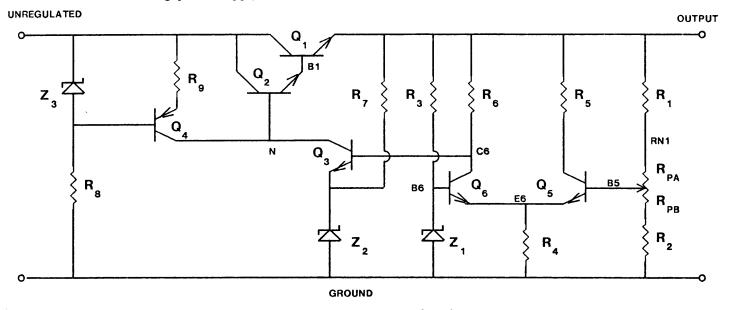

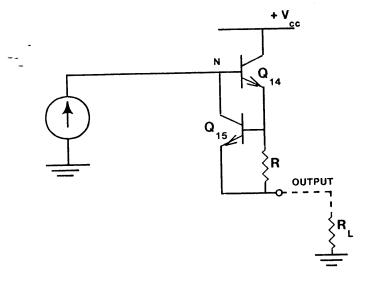

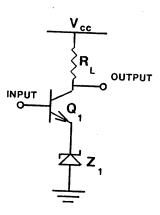

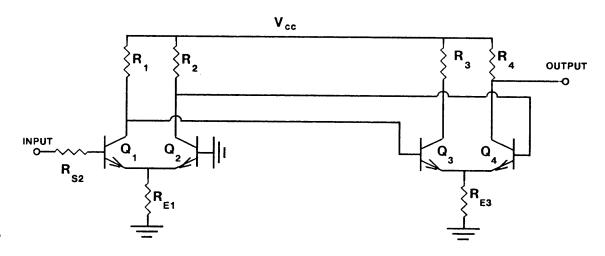

#### SCENARIO 3:

The following power supply has the same abstract description.

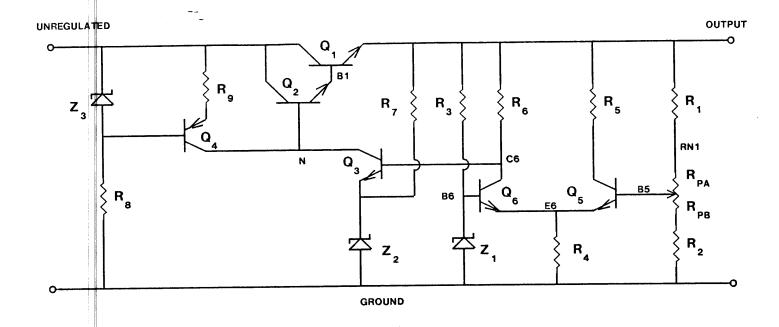

Figure 4: Complex Power Supply

This circuit poses no problem for QUAL.

#### What is Z1?

DI is part of the reference whose voltage is compared to the output voltage.

What is the purpose of Q4?

Q4 provides a constant current to the control element.

This complex circuit further illustrates the need for abstraction and teleology since the causal argument for the feedback action would fill an entire page.

#### 1.3 Reader's Guide

The thesis is organized around a development of a calculus for causal and teleological reasoning applied to the problem of recognition of electrical circuits. Chapter 4 presents a theory of causal reasoning. The specific shortcomings of this theory when applied to recognition and

solutions to these shortcomings are explored in the remaining chapters. One style of presentation is used throughout the thesis: a simple mechanism is posited to achieve a particular goal, and then modified as specific problems appear. In general, the problems are dealt with by introducing more and more abstract descriptions of circuit behavior.

To reach the widest audience, I have, as far as is possible, employed only simple and elementary electronics. Nevertheless, the depth of the reader's appreciation of the details of the theory will be influenced by his familiarity with electronics. Those who know no electronics will find the initial sections of chapter 2 and all of chapter 3 informative and the remainder of the thesis difficult to follow. Readers with a limited understanding of electronics should have little difficulty in following the examples. Since this thesis is about how people understand circuits, these readers may in fact gain a better understanding of circuits through reading it. Sections which assume a background in electrical circuits are denoted by a \*.

The following is a brief summary of the contents of the thesis:

#### Chapter 1: Introduction

The objectives and methodology of the research are presented.

#### Chapter 2: Overview and Background

An overview of QUAL's recognition process is presented. The framework of the ideas is given independently of electronics.

## Chapter 3: Theoretical Foundations

The theory underlying the causal and teleological calculus is presented independently of electronics.

## Chapter 4: Causal Reasoning

A theory is developed of the causal reasoning exhibited by engineers.

#### Chapter 5: Interpretations

The definition of a "point of view" on circuit behavior, a surprisingly subtle problem, is explored.

#### Chapter 6: Feedback

The global mechanism of feedback fits directly into the theory of causal reasoning.

#### Chapter 7: Teleology

Considering the purpose of a circuit helps the recognizer distinguish the intended point

10

of view.

Chapter 8: Abstraction

In order to deal with more complex circuits, the behavior of the circuit must be understood at shallower levels of detail.

Chapter 9: Conclusions

The results are summarized and the limitations of QUAL are discussed.

#### 1.4 Methodology

The most common technique that science uses to describe physical laws is mathematics. Since classical mathematics is better suited for describing constraints than mechanisms, this has resulted in a focus on constraints on behaviors rather than on the mechanisms by which behaviors are achieved. This research attempts to describe the more qualitative and informal techniques that humans use naturally to reason about these mechanisms. The notion of a computational process forms the foundation by which these mechanisms and human reasoning about them is described.

My approach is different from the methodology of knowledge engineering [Feigenbaum 77]. Although Feigenbaum's methodology is descriptive in that he attempts to capture the reasoning of experts, he makes no attempt to characterize the reasoning humans tacitly use. Instead he constructs a stimulus-response model consistent with expert's behavior on a narrow range of problems (and therefore is very successful on that range). Since his model is nonhierarchical, it is incapable of reasoning about the same system from different perspectives and at different levels of detail. In short, his methodology is a kind of behaviorism: he does not consider the internal calculus that humans use to be important or relevant. I believe that because of this lack of concern for internal structure his methodology will fail to elucidate the true scope of human expertise. For example, all of the current systems in his methodology cannot answer simpler versions of questions in qualitatively simpler ways. My methodology is to use the computer metaphor to explore the tacit calculus that humans use. This thesis will show how reasoning from multiple points of view and at multiple levels of detail is useful and consistent with behavior observed in engineers.

The motivation for this approach comes from cognitive psychology, education and artificial intelligence. Larkin [77] observed that expert physicists use tacit and qualitative knowledge more

extensively than neophytes working on the same problems. In general, humans do not appear to utilize the formally prescribed techniques in their thinking processes. A knowledge of how humans understand would have tremendous impact in designing teaching strategies to enable students to learn more effectively [Brown et.al. 77]. It would therefore also play a key role in computer coaches [Goldstein 77]. The experience of artificial intelligence research has been that systems which embody even a great deal of the classical knowledge fail at tasks successfully accomplished by humans with the same knowledge. An extreme example of this is Macsyma [77]. This system can perform manipulations, usually using standard techniques, which even a mathematician would find difficult; yet it rarely does what you want it to do. (See [de Kleer & Sussman 78] for a discussion of some of the problems Macsyma has when applied to electrical problems; the major points of which are summarized in section 2.5.) The major reason for the failure of these programs can be traced to the lack of more qualitative common-sense knowledge.

Humans prefer to understand systems in terms of causes and effects rather than simultaneous constraints. Until recently no techniques have existed to describe the processes which result from expressing a behavior in terms of causes and effects. The computer metaphor provides such a technique. The computer metaphor impacts this research in three ways:

- 1. The human reasoning process can be viewed as an information processing system.

- 2. Cause-effect interactions in physical systems can be viewed as processes.

- 3. It is methodologically useful to construct computer programs based on 1 and 2.

This research develops a formal theory of the informal qualitative reasoning humans appear to use in understanding electronic circuits. The reason electronics was chosen over other domains is that the structure of electrical circuits is well-understood. Powerful simplifying ideas are apparent, and that the understanding of this domain is of itself useful and important. This large body of experience provides information about how people reason about circuits. These constraints will be enumerated later in this section.

Although the theory has been implemented in the program QUAL, I do not claim that the Lisp code is a theory of anything. The presentation in the following chapters leaves out most of the implementation details. The objective of this research is to identify the key concepts which underlie human reasoning in electronics independent of any formalism. I want to maximize the constraints imposed by the domain, not those imposed by the idiosyncracies of some formalism. The following chapters are organized around the ideas, not the program. One of the shortcomings

of this research is the lack of a clean distinction of where the theory stops and the implementation begins. A rough approximation of this *architectural* boundary exists at the level where QUAL ceases to record explanations for its deductions.

There are variety of different sources of information which constrain the structure of any theory. These constraints or *forcing functions* are criteria that any alleged theory must meet. Some forcing functions are behavioral in that they specify that a certain behavior has to be met. Other forcing functions suggest what the mechanisms which produce the behavior must be like. These latter structural types of forcing functions are the more interesting.

One forcing function is performance. Does it work? Any theory has to successfully recognize circuits. Although this forcing function appears to be behavioral, it turns out to have considerable impact on the structure of the theory. Since the architectural boundary is far removed from the actual Lisp code, the implementation of tentative theories is very time consuming as well as seemingly unrewarding. However, the fact that the architectural boundary is so far removed from an actual implementation makes this effort all the more necessary. *Most theories which sound plausible do not work.* Al theories go through radical changes in the implementation process. These changes have nothing to do with the idiosyncrasics of implementation, but result from flaws in the original theory which only become obvious in the implementation process. (See McDermott [76a] for a longer discussion of this.) Throughout this research the program was run on scores of examples to determine the precise points at which the theory had to be extended. In summary, the purpose of writing a program is to debug the theory, not the implementation.

This study of electrical engineering serves primarily as an effective means to an end, and is not the end itself. It is a well-studied discipline. It provides a variety of different structural forcing functions. The circuit schematic provides a formal unambiguous representation for the circuit. Network theory can completely specify the behavior of any circuit. Electrical engineering also has a well-developed taxonomy of abstractions and teleological concepts. A great deal of literature exists on the subject which sheds light on engineers' reasoning processes. Any theory of informal reasoning must relate to these constraints. Indeed most of these constraints originate from informal concepts. Consider feedback, which has a precise and formal definition, yet it is often used informally. Any theory of qualitative reasoning must account for the relation between these two uses of the concept of feedback.

This thesis does not present any rigorous psychological experiments which either motivate or

verify the ideas discussed. The central source of insight has been introspection and observation. As a teaching assistant I had the opportunity to teach circuit theory and observe how students learn electronics. At M.I.T. we have also studied how expert electrical engineers reason about circuits [Sussman & Stallman 75]. Another source of information is the kinds of difficulties students have in understanding circuits. Experience with the SOPHIE project [Brown et.al. 74] provided data on the kinds of bugs students exhibit in trying to troubleshoot power-supplies. My research style has been to start with a simple mechanism suggested by these observations, to c ystallize it via an implementation, and to push it as far as possible to see how many of the observations it accounts for. Only when absolutely necessary is the simple mechanism extended.

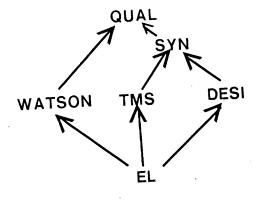

#### 1.5 The Engineering Problem Solving Project at MIT

The Engineering Problem Solving Project (EPSP) is concerned with uncovering the fundamental mechanisms involved in the kind of reasoning employed by people in the design, analysis, debugging and explanation of complex systems constructed to perform a specific function. The first achievement of this project was a formalization of the intuitive notions engineers employ in analyzing circuits quantitatively [Sussman & Stallman 75]. This theory, called propagation of constraints, led to a sequence of increasingly more sophisticated analysis programs, all called EL [Stallman & Sussman 77]. This was accompanied by a fault localization system WATSON [Brown 76] and a circuit design system DESI [McDermott 76b]. Although neither WATSON nor DESI worked as well as EL, this research argued persuasively for the role of teleology and abstraction in understanding circuit behavior.

We are currently working on a longer term project to construct a working design system [Sussman 77a]. We have recently made progress on the less ambitious goal of circuit synthesis [de Kleer & Sussman 78]. Synthesis is the determination of the parameters of the parts of network given desiderata on the network as a whole. Synthesis, unlike the full-scale design problem addressed by McDermott, presumes that the original circuit topology is given. SYN is a working system which can be of assistance to an engineer in the synthesis of a wide class of circuits. SYN's current difficulties result from its inability to understand how the circuit works. In contrast, the failure of WATSON and DESI can be traced to their inability to analyze the behavior at a specific enough level of detail. QUAL analyzes circuit behavior at a deeper level of detail than WATSON or DESI, but at a shallower level of detail than SYN. It addresses the less ambitious

14

goal of recognition, but strives for robustness.

The mechanisms that QUAL uses for its causal reasoning bear close resemblance to the propagation of constraints technique used in EL and SYN. In fact, the two systems share Lisp code. QUAL records explicit dependency information about its deductions as suggested by TMS [Doyle 77]. The idea of recording dependencies explicitly came from the original EL.

Figure 5: Evolution of EPSP

Another interest of the EPSP is programming apprentices [Rich & Shrobe 78] [Waters 78] [Shrobe 79]. Many of the ideas underlying the programming apprentice research originated from electronics, and it has progressed to the point where it now has much to contribute to the electronics side of the project. The programming apprentice project has pushed the ideas of teleology and abstraction to far more precision in its attempt to produce a taxonomy of the plan types used in programming. This ongoing work on programming has had considerable impact on this thesis.

The idea that causality and teleology are important in understanding circuit behavior is not new. Brown, McDermott and Sussman have all argued for it. The previous research emphasized the goals of analysis, design and fault localization at the expense of the underlying descriptions of circuit mechanisms. Causality and teleology are very broad concepts representing clusters of distinct ideas. QUAL deals with only a small subset of what Brown and McDermott termed causal or teleological. What is new is that a particularly simple type of teleology and causality interacting in limited ways is sufficient to account for much of circuit understanding.

#### 1.6 Other Related Work

Related work on electronics was covered in the previous section. My earlier work on mechanics [de Kleer 77b] is a precursor for this work on electronics and is discussed in chapter 3. One group of related research is characterized by Rieger & Grinberg [77] and Freiling [77] who model human causal reasoning. Another group studies human reasoning of physical systems in more generality without necessarily focusing on causality. People in this group are Bundy et.al.[76], Hayes [78] and McDermott & Larkin [78]. QUAL falls between these two groups by demonstrating how causality affects reasoning generally.

My research differs from this related work by focusing on the distinction between the object that manifests the behavior and the abstract mechanism by which the object achieves that behavior. This distinction solves many of the difficulties of Rieger's and Freiling's theories. With the distinction between object and mechanism the theory of causal reasoning and teleological reasoning can be tested by recognition. Without the object, all of the possible causal interactions have to be included by the researcher, thus making the representation highly suspect. Since it is the task of recognition to identify all possible causal interactions, this provides a forcing function on the causal representation. The only way to obtain mechanism from object is by modeling. A model for a component describes its behavior from a particular point of view. Since neither Rieger nor Freiling explore modeling, the content of their mechanism representation is completely arbitrary.

My central objection to Rieger's theory is that it has no structural representation of the device that the cause-effect representation is a description of. This objection raises serious questions about the nature of his theory and is a major source of the theory's difficulties. The structure of a cause-effect diagram for a device is determined by the person who constructed it. Different people will come up with different diagrams and there is absolutely no way to compare them. Further, his representation is nonhierarchical and therefore has little facility for describing mechanisms at a shallower level of detail.

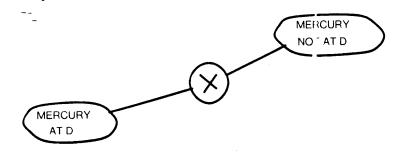

The absence of an object-device results in problems with equality. In Rieger's cause-effect diagram for the forced air furnace there are two states labeled "mercury not at D" and "mercury at D." Since there is no underlying object "D" to refer to, these labels have no meaning. In order to express that these two states are antithetical a separate "state-antagonism" node must

Figure 6: State-Antagonism in Forced Air Furnace

be placed between them (figure 6). The lack of an object-device makes it difficult to determine whether two actions are interacting since there is no common way of referring to the device parts manifesting the behavior. Rieger utilizes a procedural simulation of the declarative process description to determine unexpected sources of causal interaction. This is an obscure way of temporarily creating an approximation to the object-device.

Rieger does not use his cause-effect diagrams for anything other than simulating the physical devices. He does not explore other ways reason about them. It is a thin horizontal slice of a plausible theory of human reasoning about causality missing any forcing function. Currently, Grinberg [78] is applying Rieger's theory to design, and the application of this forcing function will likely lead to the incorporation of a more explicit notion of the object-device.

Freiling has extended Rieger's work to deal with many of the above objections. His representation is hierarchical thus allowing reasoning to take place at different levels of detail. Rieger's representation does not distinguish between cause and intention, whereas Freiling's does. The combination of hierarchy and explicit progress variables allow Freiling to circumvent the use of an object-device. Freiling explains how his representation might be used for recognition. He defines recognition as moving up the hierarchy from a basic causal description of the device to a more abstract description of the causality of the object-device. Although not the focus of his work, he also discusses the problem of determining the basic causal description of the mechanical device from its geometry. Unlike electronics where a detailed representation of the object-device has been developed by electrical engineers, vision research as not progressed as far thus making the determination of the basic causal description rather difficult.

QUAL utilizes the circuit schematic as an explicit description of the object-device. From this object-device it constructs a representation of the mechanism. This representation is closer to

Freiling's than Rieger's in that it distinguishes cause and intention and in that it is hierarchical. However, QUAL nowhere contains a representation identical to Freiling's or Rieger's. The content of their representations is separated into a number of distinct structures in QUAL. The unique focus of my research is the determination of the function from the structure of the object. This is the problem of recognition.

# Chapter 2

## OVERVIEW AND BACKGROUND

#### 2.1 The Overall Recognition Process

This chapter presents an overall perspective of the recognition process discussed in chapters 4 through 8. The discussion in this chapter makes some reference to electronics, but does not require the sophistication with electronics that is needed to appreciate those chapters. Chapter 3 discusses the theoretical foundations underlying this recognition theory, and requires no knowledge of electronics.

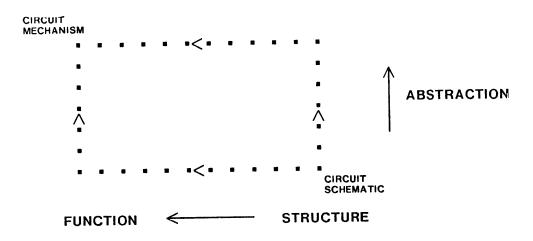

The task of recognition is to determine, from a description of the circuit, a description of the mechanism by which the circuit achieves its behavior. Recognition is a convenient forcing function since both descriptions for circuits and descriptions for mechanisms are fairly well agreed upon in electrical engineering. A description of the circuit consists of a schematic, and a description of the mechanism explains how each component's individual behavior contributes to the overall behavior of the system. This type of functional description is central for analysis, design and troubleshooting.

In order to recognize an object its properties must be related to those the recognizer is familiar with. One recognition technique, topological analysis, compares the topology of a new circuit with previously recognized topologies. Another recognition technique, functional analysis, determines the behavior of the overall circuit by combining the behaviors of the individual components. Both functional and topological analysis construct a hierarchical description of the circuit. In functional analysis this hierarchy is in terms of fragments of behavior, while in topological analysis this analysis is in terms of fragments of topology. A third technique, geometric analysis, relies on the tacit graphical language engineers use when they describe circuit topologies on paper. Geometric analysis is incomplete by definition, and its only utility is efficiency. Functional analysis is the most powerful recognition technique since the ultimate test of a circuit is whether it functions correctly, and not whether it has the correct topology or geometry. Furthermore, any geometric

or topological analysis must eventually produce a description of the circuit's mechanism.

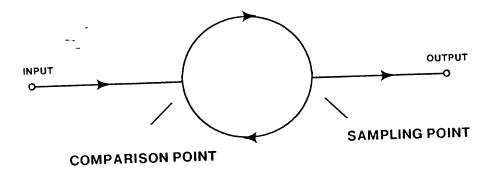

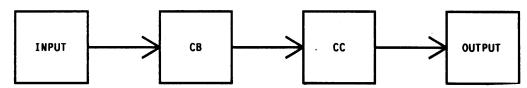

Figure 1: Functional vs. Topological Recognition

These issues can be illustrated by an example from engines. A mechanic recognizes an automobile engine simply by its shape. However, if asked to explain why it is an engine he will give a functional description of why it operates. When presented with a new engine type (e.g. from a ship or airplane), he will not be able to recognize it with the shape clues for automobile engines but will need to analyze its functioning in order to determine that it is an engine. (In order for him to successfully analyze its functioning he must, of course, recognize the parts of the new engine.)

Functional analysis has theoretical advantages over topological and geometric analysis. The same system component can have multiple purposes and may thus be shared among many modules. (See Steele & Sussman [78] for a discussion of almost-hierarchical systems.) Therefore, any hierarchical description of the system's purpose will be tangled and difficult to reason about. In functional analysis, this undesirable sharing can be isolated to one level of the analysis. If the same component is contributing in two different ways to the system's behavior, the causal and teleological analysis and will discover this and ascribe two primitive behaviors to it, and primitive behaviors are never shared. For example, functional analysis is not confused by the fact that the wheels both support the car and are part of the drive train, because these are two very different behaviors. Topological analysis has to insert "wheel" in two different places in a topological hierarchy.

This can be viewed yet another way. The basic theme of recognition is the determination of mechanism from structure. Topological analysis attempts to produce a hierarchy of structures, each of which has a known behavior. Functional analysis, on the other hand, produces a very primitive description of the mechanism from the structure, and then constructs a hierarchical description of this mechanism, ignoring the original structure.

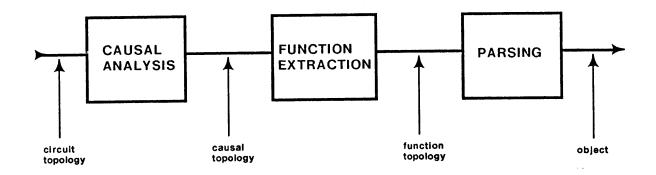

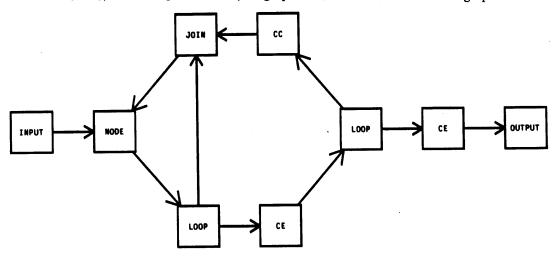

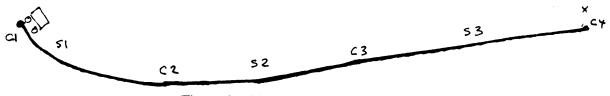

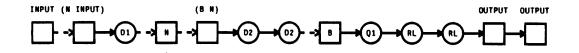

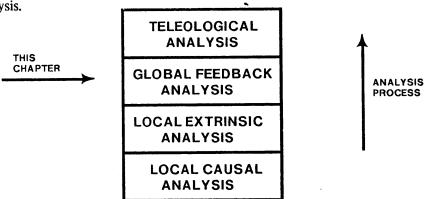

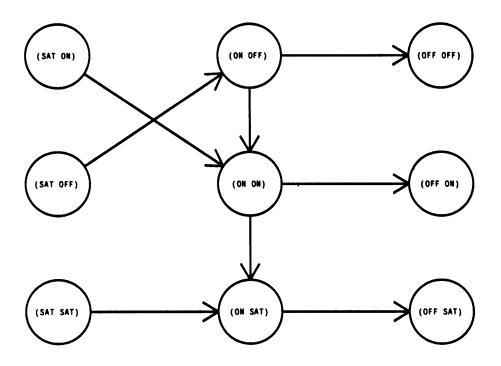

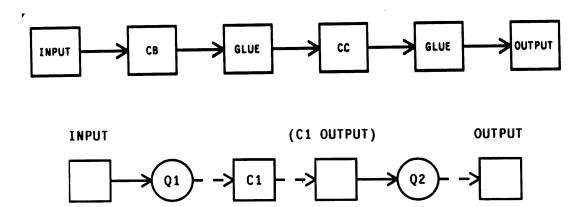

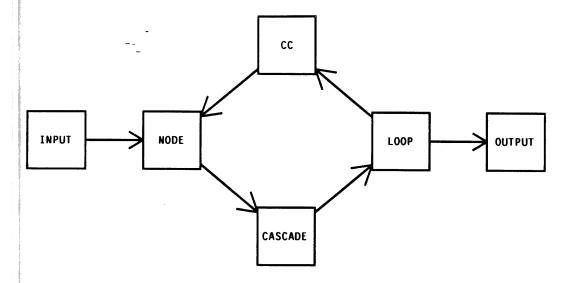

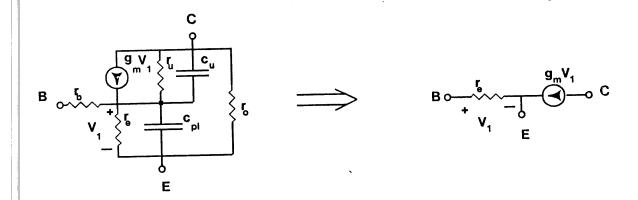

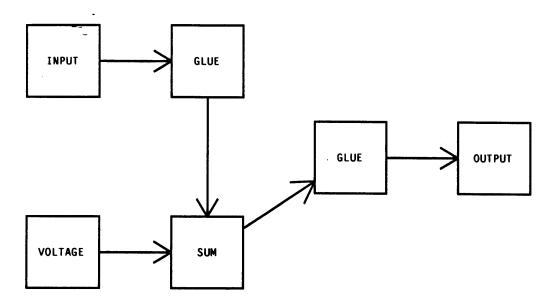

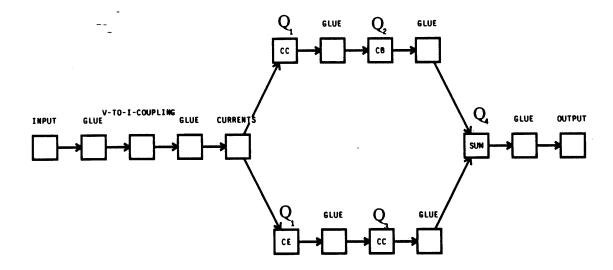

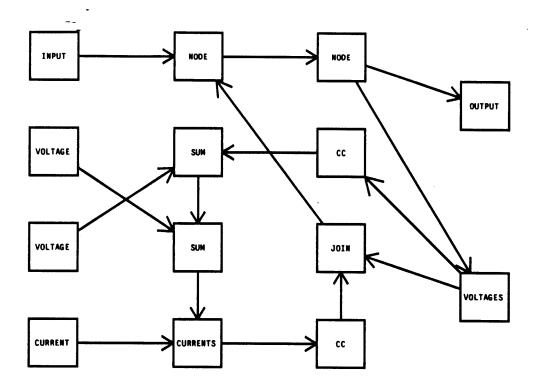

QUAL's recognition process is summarized by the following flow chart:

Figure 2: QUAL's Recognition Process

The following three sections discuss the three major steps in the process.

For this process to be useful and examinable, each step must construct extensive explanations for the circuit's behavior from its perspective, as well as recording reasons for its deductions. Therefore, although the process terminates with a single token describing the system (e.g. amplifier) the user and other programs will have access to why that circuit is what QUAL claims it is.

The process encounters choice points where ambiguities have to be resolved. For the types of circuits QUAL recognizes, these ambiguities can be dealt with by a variety of heuristics. Since these are heuristics, the resulting explanations that QUAL produces are rationalizations.

#### 2.2 Causal Analysis

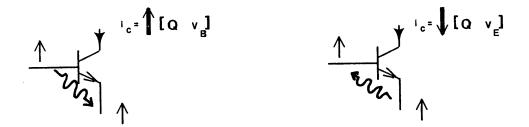

Causal analysis takes a description of the circuit's topology as an input and produces a qualitative description of the circuit's incremental behavior as an output. The input description includes an annotation identifying the circuit's input-output ports:

```

(circuit: ce-feedback

nodes: (vcc-ground b1 c1 output e2 fp)

devices: ((q1 (npn-transistor emitter: ground base: b1 collector: c1))

(q2 (npn-transistor emitter: e2 base: c1 collector: output))

(rc1 (resistor vcc c1))

(rc2 (resistor vcc output))

(rb1 (resistor e2 fp))

(rb2 (resistor fp ground))

(rf (resistor fp b1))

(input (terminal b1))

(output (terminal output))

(common (terminal ground))

(supply (battery vcc ground)))

(current input)

input:

(voltage output ground))

output:

```

Figure 3: Description of CE-FEEDBACK for QUAL

Figure 4: CE-FEEDBACK

Causal analysis determines the behavior of the circuit by propagating the input through the circuit and constructing a description of the resulting behavior. In the case of CE-FEEDBACK, QUAL produces a description which corresponds to the following english text: "The increased input voltage turns Q1 on harder, pulling down its collector. This falling voltage is applied to the base of Q2, causing it to begin to turn off. Since Q2's collector current is dropping, the voltage

across the load RC2 must also drop." QUAL quantizes each electrical quantity into increasing(1), decreasing(1) or unchanging(0). Part of the description which QUAL provides is:

Starting with input:

(VOLTAGE B1 GROUND) = 1

Premise

An increasing input voltage is applied to the circuit.

(CURRENT C Q1) = ↑

$V \Rightarrow IC \text{ for } Q1$

The convention is that currents flow into devices away from nodes. This statement indicates that the current flowing into the collector of QI is increasing.

(VOLTAGE C1 GROUND) = !

KCL-heuristic at C1

The potential at Q1's collector drops.

(VOLTAGE E2 C1) = ↑

KVL-heuristic at Q2

Since (VOLTAGE <n1> <n2>) represents the voltage from <n1> to <n2>, this is equivalent to

$(VOLTAGE\ CI\ E2) = \downarrow$

(CURRENT C Q2) = ↓

$V \Rightarrow IC \text{ for } Q2$

The current flowing into the collector of Q2 is decreasing.

(CURRENT #2 RC2) = 1

KCL for node OUTPUT

The current flowing into the bottom terminal of RC2 is increasing.

(CURRENT #1 RC2) = |

KCL for device RC2

The current flowing into the top terminal of RC2 is decreasing. Two currents appear for RC2 because currents are defined for terminals and not for devices. Ohm's law is specified using the current in the #1 terminal of resistors.

(VOLTAGE OUTPUT VCC) = ↑

⇔ V I for RC2

Ohm's law for RC2.

Also given that:

(VOLTAGE VCC GROUND) = 0

SUPPLY

Since the voltage between VCC and GROUND is fixed by the battery, it cannot change.

The combination of events (VOLTAGE GROUND VCC) (VOLTAGE OUTPUT VCC) cause: (VOLTAGE OUTPUT GROUND) =  $\uparrow$

KVL applied to nodes OUTPUT VCC GROUND

There are four important points to bear in mind when reading causal arguments. First, the values refer to changes in circuit quantities and not the quantities themselves. The fact that the collector current is negative or positive bears no relation to whether it is increasing or decreasing. The incremental voltage between the node: of a battery is always zero since the battery fixes this voltage. Second, the values refer to changes in circuit quantities, not changes in absolute values of circuit quantities. Thus a change of value from -3 to -2 is considered an increase just as a change of value from 2 to 3. Third, the statement "x is increasing" is equivalent to "—x is decreasing." Thus, (VOLTAGE  $\langle n1 \rangle \langle n2 \rangle$ ) = - (VOLTAGE  $\langle n2 \rangle \langle n1 \rangle$ ). Fourth, all currents flow into devices away from nodes. These issues are critical to the nature of causal arguments and will be examined in detail in Chapter 4.

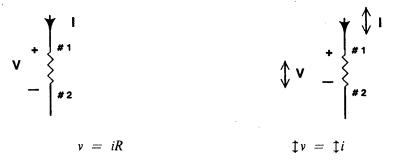

All of the standard electrical device models have been reformulated to deal with these qualitative quantities. For example, Ohm's Law V = IR, when quantized is  $V \Leftrightarrow I$  indicating that the change in V must be the same as the change in I. Since the resistance R is presumed to be positive, its precise value never contributes to the circuit's behavior.

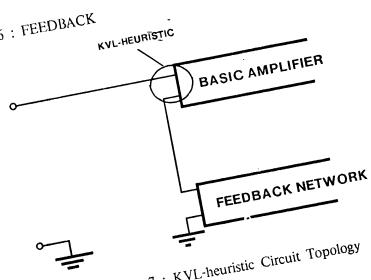

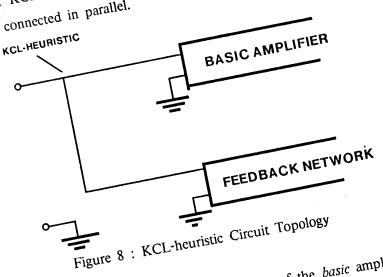

These rules are insufficient to deal with CE-FEEDBACK, and thus QUAL incorporates heuristic rules which it applies when the basic rules break down. From a network theory viewpoint these rules are invalid, but they are extremely useful in analyzing circuit behavior. These rules were discovered by examining the arguments of electrical engineers. Only two heuristics are necessary to deal with most circuits: KCL- and KVL-heuristics. (The heuristics are named after the corresponding Kirchoff's voltage or current law.) The KCL-heuristic predicts that the voltage at a node will drop if the current drawn from the node is increasing (and correspondingly, if the current is decreasing the voltage will rise). For example, since Q1 is pulling current out of node C1, the voltage at C1 drops, even though the currents from RC1 and Q2 are unknown. By the phrases "current drawn from the node is increasing" and "pulling current out of node" I mean that with the sign convention chosen such that current flowing out of a node is positive, that the particular current in question is becoming more positive. This raises a seeming contradiction. For the sake of argument assume that the base current of Q2 is zero. Then the current in RC1 is the same as that of the collector of Q1. Thus the change in current flowing out of the node

into Q1 is equal and opposite the change in current flowing out of the node into RC1. These opposite currents, by the KCL-heuristic, predict opposite voltages at node C1. This contradiction is resolved by introducing the notion of causality: since the current in Q1 "causes" the current in RC1, it is the correct current to use in the KCL-heuristic. The KVL-heuristic predicts that the potential at a device's terminal can be applied directly to the device. For example, the rising potential at the base of Q2 causes its base-emitter voltage to increase. The KVL-heuristic also requires a notion of causality, but this discussion is left until later.

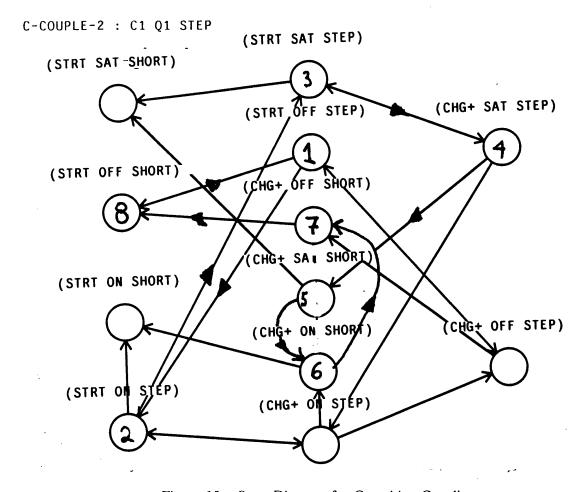

These heuristics make assumptions about the behavior of the rest of the circuit, and as a consequence the causal analysis may discover multiple conflicting behaviors for the same circuit. Both heuristics assume the circuit fragment connected to the node or device is behaving as a positive resistance. For example, the KCL-heuristic assumes that other currents flowing into the node have no effect, and the KVL-heuristic assumes that the voltage at the device's other terminals can be ignored. The causal analysis therefore produces a number of possible behaviors, or *interpretations*, for the circuit's behavior.

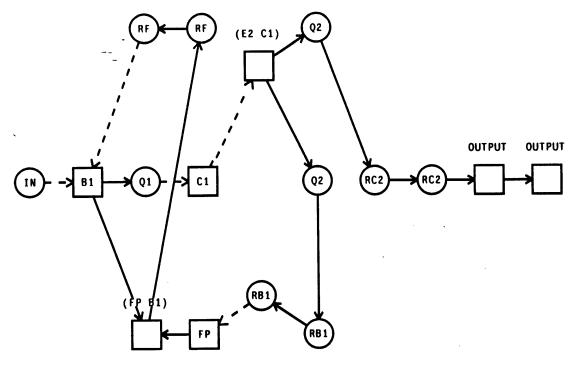

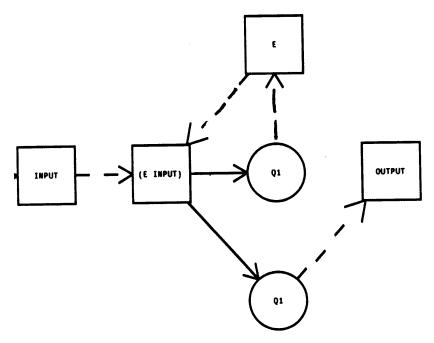

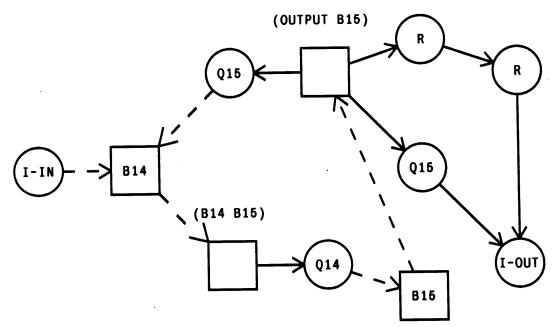

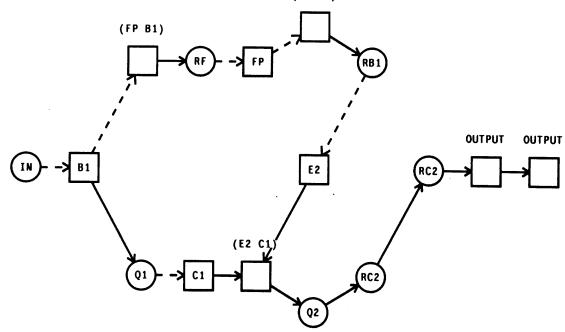

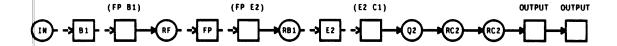

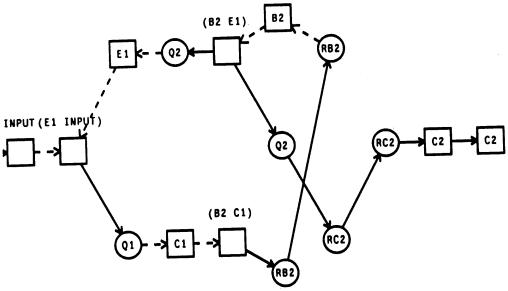

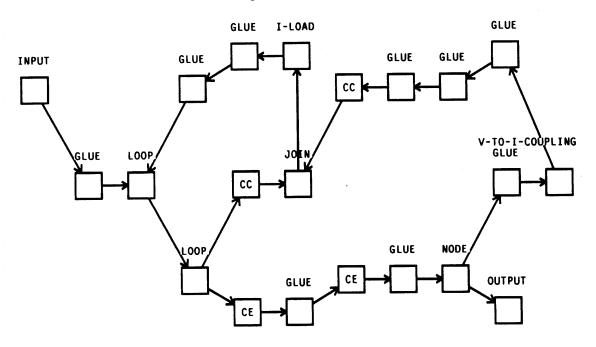

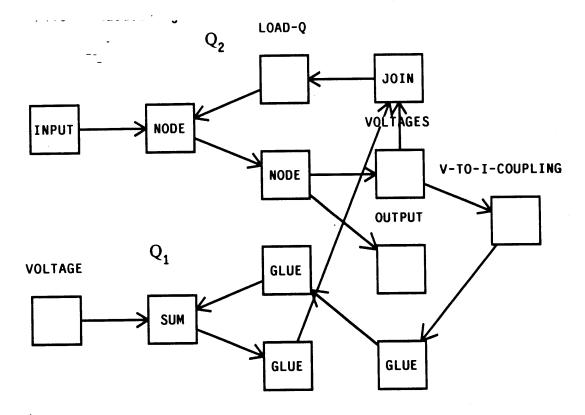

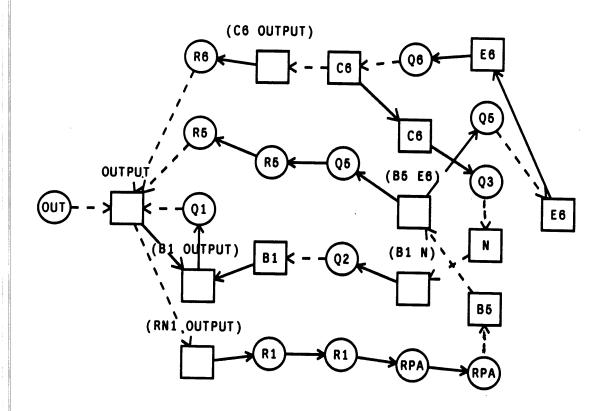

QUAL summarizes the causal argument by a *mechanism graph* which describes how the circuit achieves its behavior:

Figure 5: Mechanism Graph for Correct Interpretation

Figure 6: CE-FEEDBACK

Every vertex of the mechanism graph corresponds to a changing circuit quantity. Voltage vertices are indicated by squares and are labeled by the voltage's two nodes. If one of the nodes is incremental ground, the vertex is labeled with the name of the remaining nonground node. Current vertices are indicated by circles. Since currents only flow through terminals, these vertices are labeled by the terminal's device. Every edge of the mechanism graph corresponds to the application of a causal rule. If the causal rule makes an assumption, the edge is indicated by a dashed instead of solid line.

The path through the mechanism graph IN  $\rightarrow$  B1  $\rightarrow$  Q1  $\rightarrow$  C1  $\rightarrow$  (E2 C1)  $\rightarrow$  Q2  $\rightarrow$  RC2  $\rightarrow$  RC2  $\rightarrow$  OUTPUT  $\rightarrow$  OUTPUT is in one-to-one correspondence with the causal argument presented at the beginning of the section (after figure 4). The remaining edges and vertices describe the feedback path.

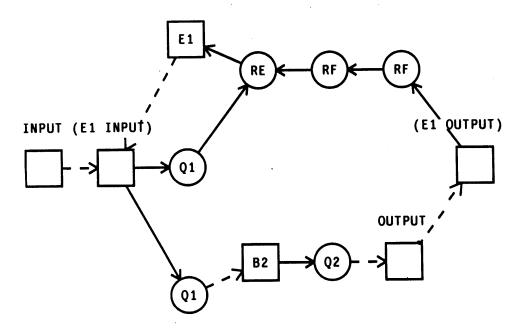

#### 2.3 Function Extraction

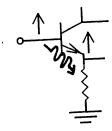

For each of the interpretations produced by the causal analysis, the function extraction phase constructs a description in terms of the behavioral features used by electrical engineers. Finally, it chooses that interpretation which exhibits the most plausible features.

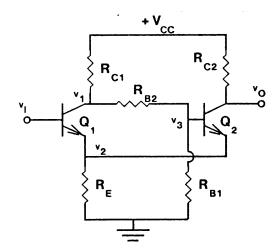

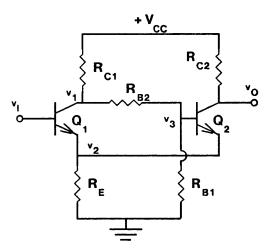

The electrical models utilized within the causal analysis characterize the device's behavior in every possible context. However only a part of this general description is required to deal with the behavior of the device in any particular interpretation. This part characterizes the *function* of the device with respect to the interpretation. Since function describes how individual devices contribute to the overall behavior of the system, it assigns purpose to the individual devices. In QUAL this simple kind of purpose description is called *implementation teleology*.

Consider CE-FEEBACK again. The causal argument for CE-FEEDBACK indicates that Q1's input signal is applied to its base and that its output signal is its collector current. This is known to engineers as the common-emitter configuration. Similarly, Q2 is also functioning in the common-emitter configuration. (There are 11 such transistor configurations. The resistor has 6 configurations.) For example, RC2 is functioning as a current-to-voltage converter. QUAL produces the following description of the implementation teleology of CE-FEEDBACK:

Q1 is functioning in the common-emitter configuration.

Q2 is functioning in the common-emitter configuration.

Q2 is functioning in the common-collector configuration.

RC1 is functioning as a current load.

RC2 is functioning as a current load.

RB1 is functioning as a wire.

RB2 is functioning as a current load.

RF is functioning as a voltage sensor.

Note that Q2 is functioning in two configurations: in the common-collector configuration on the feedback path and in the common-emitter configuration on the main signal path. Because causal analysis does not adequately deal with bias, it cannot find any meaningful purpose for RB1.

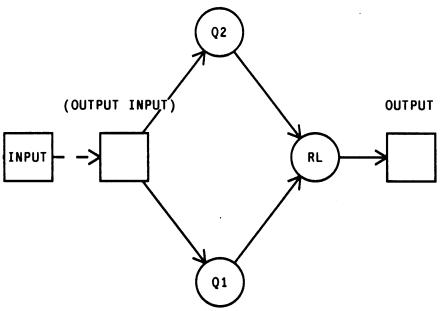

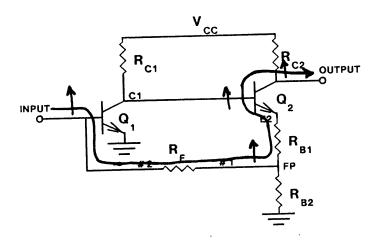

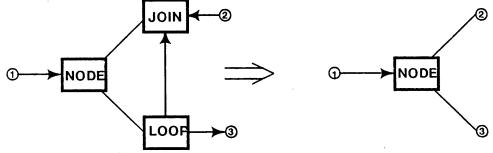

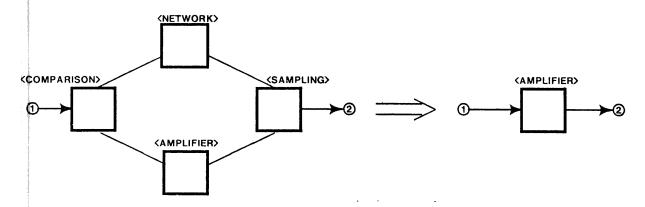

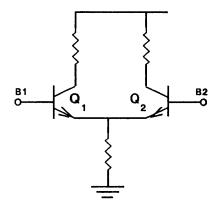

Each configuration shares inputs and outputs with other configurations permitting the configuration topology to be represented by a graph similar to the mechanism graph:

Figure 7: (Abbreviated) Configurations for CE-FEEDBACK

The vertices correspond to configurations and edges indicate shared input-output ports. In figure 7, every edge corresponds to some vertex of the mechanism graph. The vertex labeled NODE indicates that B1 is a comparison point of type node. The vertex labeled LOOP indicates that Q2 is a sampling point of type loop.

Electrical circuits have been studied extensively and as a consequence, the potentially useful configurations have been culturally identified (although somewhat informally). QUAL's library contains a taxonomy of these configurations, all of which can be identified by connected patterns of vertices in the mechanism graph. The construction of the configuration graph from the mechanism graph is therefore straightforward.

Each interpretation leads to a different implementation teleology, and QUAL chooses that interpretation which assigns maximum purpose to the components, as the correct one. For example, in the interpretation in which the signal flows through RF to Q2 bypassing Q1, Q1 has no purpose and therefore the interpretation is rejected. The correct interpretation can be determined without knowing the ultimate purpose of the system. One of the reasons this strategy is successful is that circuits are designed to meet minimum cost constraints and therefore only components with functional purpose are ever included.

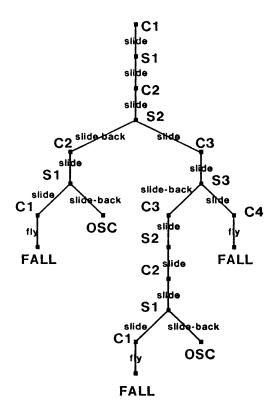

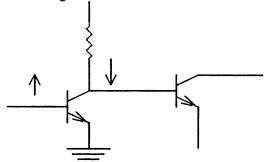

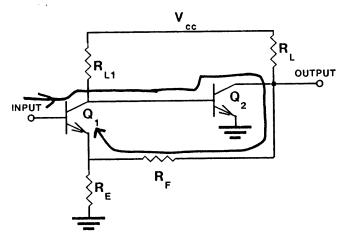

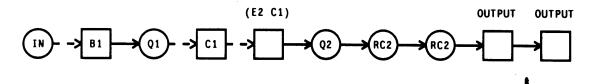

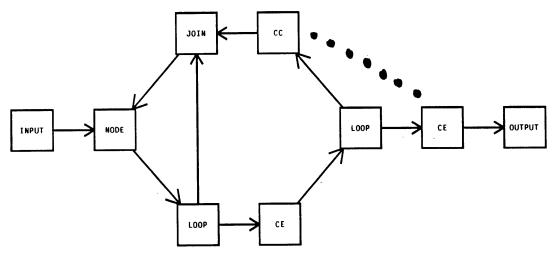

### 2.4 Parsing

The final step of the recognition process takes the configurations produced by the function extraction step and produces a hierarchical description of how the functioning of the individual components contributes to the overall behavior of the circuit. This step determines that CE-FEEDBACK is a two-stage feedback amplifier with Q1 being the first stage and Q2 the second, and that both stages exhibit voltage and current gains such that the overall amplifier has high voltage and current gain.

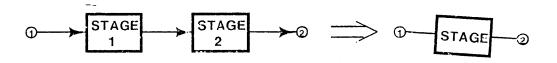

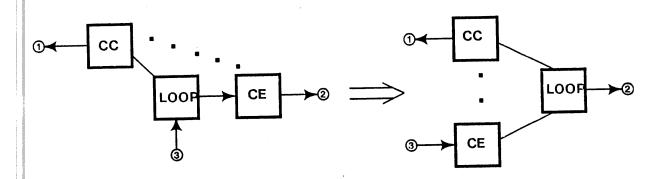

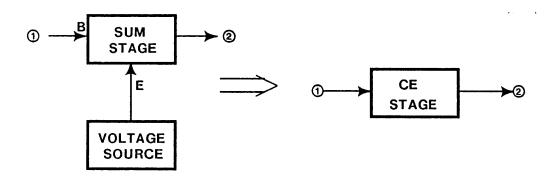

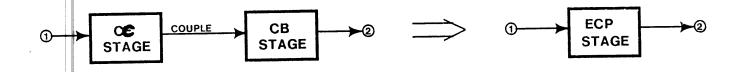

Each piece of behavior is represented by a *fragment*. The configurations provided by the function extraction step form the primitive fragments which are parsed with topological rewrite rules. In the parsing step these rewrite rules are applied until only one fragment remains, thus producing a hierarchical description of the circuit's behavior. The simplest rewrite rule is the cascade rule:

Figure 8: Cascade Rewrite Rule

The gain of the composite is the product of the constituent gains. The input impedance of the composite fragment is the input impedance of the input stage and the output impedance of the composite fragment is the output impedance of the output stage. QUAL's library contains a grammar of approximately 30 such rules which are applicable to power-supplies and amplifiers.

Since these rules deal with function and not structure there is no sharing, and the description produced by the rewrite rules is completely hierarchical. QUAL explains the purpose of each component by listing its parent fragments within the hierarchical parse:

Q1 is functioning in CE configuration.

Which is STAGE1 of CASCADE

Which is BASIC-AMPLIFIER of FEEDBACK

Which is STAGE of TOP-LEVEL

Q2 is functioning in LOOP configuration.

Which is SAMPLING of FEEDBACK

Which is STAGE of TOP-LEVEL

And,

Q2 is functioning in CE configuration.

Which is STAGE2 of CASCADE

Which is BASIC-AMPLIFIER of FEEDBACK

Which is STAGE of TOP-LEVEL

And.

Q2 is functioning in CC configuration.

Which is FEEDBACK-COUPLING of FEEDBACK-NETWORK

Which is FEEDBACK-NETWORK of FEEDBACK

Which is STAGE of TOP-LEVEL

RC1 is functioning in I-LOAD configuration.

For Q1 functioning in CE configuration.

Which is STAGE1 of CASCADE

Which is BASIC-AMPLIFIER of FEEDBACK

Which is STAGE of TOP-LEVEL

The topological rewrite rules have much the same structure as the rewrite rules that might be used in the topological analysis of a circuit schematic. However, these rules operate on the topology of the causal interactions, not the topology of the physical connections. Besides the theoretical advantages discussed in section 1, this strategy abstracts away much of the surface details of the circuit topology and provides a simple kind of canonicalization which makes the last step of the recognition process much easier.

## 2.5 \*Propagation of Constraints Applied to Circuit Analysis

When the engineer needs to know the detailed behavior of the system, he models the behavior of the components as constraint equations and manipulates these equations in order to solve for the quantities of interest. Classical network theory has a formal technique for constructing a necessary and sufficient number of these constraints: node equations or loop equations. The resulting simultaneous equations are guaranteed to be solvable for the quantities of interest. However, we have observed that few engineers use these techniques to solve circuits. Instead they employ a tacit calculus for constructing and manipulating these constraints which takes advantage of the idiosyncratic structure of equations about electrical quantities and minimizes the amount of symbolic manipulation that is required to solve them. This tacit calculus has been articulated in recent AI research, and is called *propagation of constraints*. This section discusses propagation of constraints and two circuit analysis programs based on it, since they are the precursors to the research presented in this report.

Propagation of constraints is directly related to the theory of causal reasoning developed in chapter 4. Although EL and SYN are capable of analyzing and synthesizing a variety of circuits, they suffer from a number of difficulties whose origin can be traced to the incomplete characterization of the calculus engineers use to analyze circuits. The theory of causal and teleological reasoning presented in this thesis is one part of this tacit calculus that is missing from EL and SYN. As this theory is developed, I will explain how it solves some of the problems of

EL and SYN.

SYN, the latest of a sequence of circuit analysis programs based on propagation of constraints, was developed specifically for circuit synthesis. Synthesis, the determination of the parameters of the parts of a network given desiderata for the behavior of the network as a whole, is a major facet of design. However, the following discussion only considers its analysis capabilities.

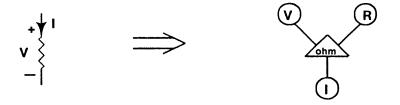

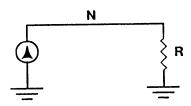

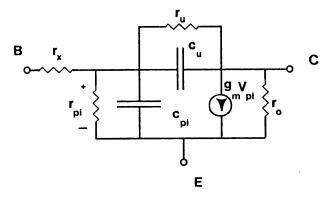

Abstractly, a circuit is made of cells, each of which represents an electrically interesting quantity, such as a voltage, current or resistance. A cell may participate in one or more constraint expressions each of which represents an electrical circuit law. A constraint expression involves several cells, thus the voltage across a resistor, the current through it, and its resistance are related by a constraint expression which is an instance of Ohm's law for that particular resistor.

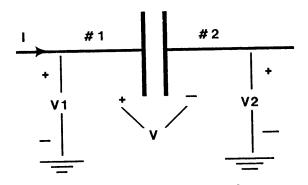

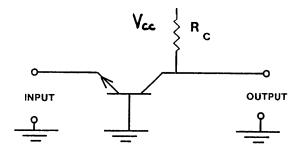

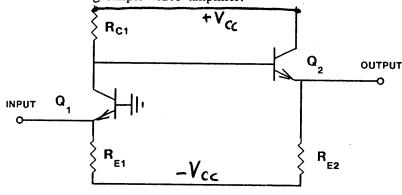

Figure 9: A Resistor as a Constraint Diagram

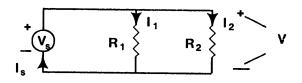

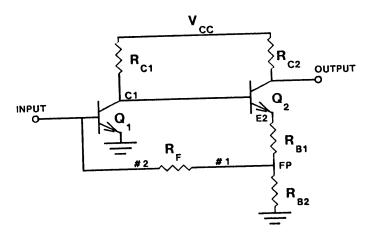

When a model of a circuit is made, a network of cells and constraint expressions is constructed. For example the following circuit

Figure 10: A Simple Circuit

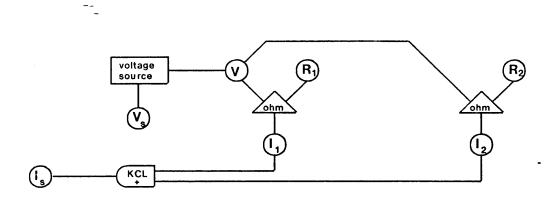

may be represented by the following simplified constraint diagram. (SYN's constraint diagram is more complex.):

Figure 11: A Constraint Diagram for the Circuit of Figure 10

Each cell may have a value. The value may come from the user or it may be deduced from other values by constraint expressions. When a cell is assigned a value each constraint it participates in is considered to determine if enough information is available to enable it to use that constraint to deduce a value for another cell. Discovering a new value may thus determine yet other values, thus "propagating the constraints."

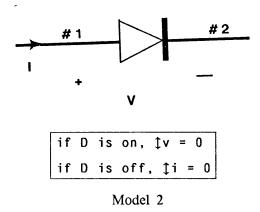

Sometimes two different constraints each can produce a value for the same cell. If this condition, called a *coincidence*, occurs, the values must be the same for the set of constraints to be satisfiable. If the values are constants, and if they are equal no new information is deduced, but if the constants differ, a contradiction has been found. A contradiction indicates that some faulty assumption has been made in the analysis. Sometimes, the value is a symbolic expression. In the case of a coincidence equating symbolic quantities, there is a third possible outcome. One symbolic quantity may be eliminated by solving for it in terms of the others.

Consider an example: SYN knows the voltage of the source  $V_S$ , the resistance  $R_1$ , and the resistance  $R_2$  in the circuit of figure 10. Looking at the constraint diagram in figure 11, we see that the only constraint which can make a deduction is the voltage-source law. Thus cell V is assigned a value equal to the value of cell  $V_S$ . The constraints attached to cell V are now examined to determine if any other deductions can be made. Ohm's law for both resistors can combine the values of V and their resistances to produce values for their currents.  $I_1$  and  $I_2$  can now be combined to determine a value for  $I_S$ .

The method does not always work so easily. If in the circuit of figure 10, SYN was told  $I_S$  instead of the voltage,  $V_S$ , no local constraint expression would have enough information to make any deductions by itself, though the behavior of the network can be totally determined from the given information. The problem involves an inherent simultaneity in the constraints. This can be overcome by introducing a symbolic quantity and propagating it as if it was known. This symbolic quantity is called an *anonymous object* since it is propagated as if it were known in the hope that ensuing propagations will constraint its value. In this example, SYN could give cell  $I_1$  the value  $\alpha$ . Now it is possible to use KCL to deduce that  $I_2$  is  $I_S - \alpha$  and it is also possible to use Ohm's law to deduce that V is  $\alpha R_1$ . These new values can be further propagated. Using Ohm's law on the other resistor allows us to determine that V is  $(I_S - \alpha)R_2$ . But SYN already knows a value for V. Hence there is a coincidence, and the algebraic equation:

$$(I_S - a)R_2 = aR_1$$

must be solved. It can be solved:

$$\alpha = \frac{R_2}{R_1 + R_2} I_{S}$$

The value of V is now known in terms of given parameters. This value can be propagated by the voltage-source law to give a value for  $V_S$ .

Such examples illustrate the need for symbolic algebraic manipulation in a program which performs analysis by propagation of constraints. The simultaneity is apparent in the constraint diagram (see figure 11) because there is a loop of constraints containing only unknown quantities. In the first example, the loop was broken when V was determined by propagation from  $V_S$  outside of the loop. In the second example, a symbolic unknown,  $\alpha$ , was used to break the loop. The unknown could have been introduced anywhere in the loop and the coincidence could have happened anywhere in the loop. In essence, propagation is a means of constructing a small, dense set of equations from a large but sparse set.

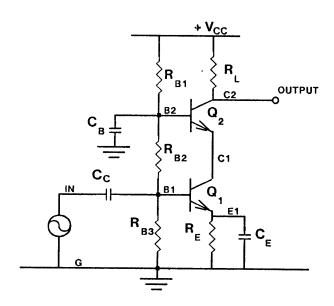

A typical circuit SYN can deal with is the cascode:

Figure 12: A Cascode Amplifier

By examining quiescent and incremental models of this circuit, SYN determines that its midband gain is:

$$\frac{r_{\pi 1} \text{gm}_2 \text{R}_L}{r_{X1} + r_{\pi 1}}$$

In order to solve a circuit by propagation of constraints, all possible constraints relating interesting circuit quantities are constructed. This collection includes all the device rules, applications of KCL at every node and device, and applications of KVL around every loop. These constraints are not represented as algebraic equations, but simply as black boxes which have no internal structure and whose inputs and outputs represent circuit quantities. Each such box represents a relation between circuit quantities that may be useful for solving the circuit, and has the potential of becoming an equation. This collection, or constraint graph, is a representation of all the potential equations that might be created to describe the circuit. Node equations and loop equations can be viewed as a way of choosing a specific subset of the black boxes that produces a necessary and sufficient set of equations to solve the system.

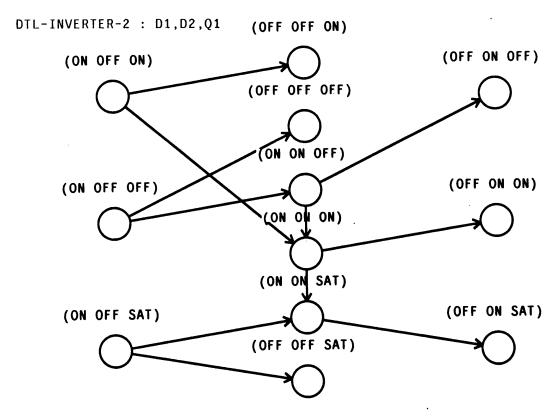

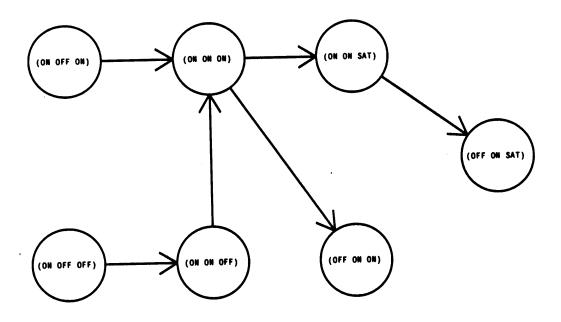

Propagation of constraints is another technique for solving the constraint graph which often requires less algebraic manipulation. It can be best illustrated by the following protocol. Suppose that we are told that the dc bias at B1 is 5 volts: