**SYSTEMASTER**

User Manual

Copyright c 1982 Teletek Enterprises, Inc. Sacramento, California, USA Revision 2, March 1982

# Table of Contents

| Ι.   | PRODU | JCT DESCRIPTION                 | 3  |  |  |

|------|-------|---------------------------------|----|--|--|

| II.  | SPEC  | SPECIFICATIONS 5                |    |  |  |

| III. | INSTA | ALLATION                        | 6  |  |  |

|      | 3.1   | Peripheral Connections          |    |  |  |

|      |       | Serial Ports                    | 7  |  |  |

|      |       | Parallel Ports                  | 9  |  |  |

|      |       | Floppy Disk Drive               | 11 |  |  |

|      | 3.2   | Options                         |    |  |  |

|      |       | Write Compensation              | 12 |  |  |

|      |       | Extended Head Load              | 13 |  |  |

|      |       | Wait State Generator            | 14 |  |  |

|      |       | CTC Timing                      | 14 |  |  |

|      |       | EPROM/RAM Options               | 15 |  |  |

| IV.  | THEOR | RY OF OPERATION                 | 17 |  |  |

| ٧.   | IN CA | ASE OF TROUBLE                  | 29 |  |  |

|      | Apper | ndíx A - Board Layout           |    |  |  |

|      | Apper | ndix B - Disk Drive Interfacing |    |  |  |

|      | Apper | ndix C - Memory Board Set-up    |    |  |  |

|      | Anner | ndix D = NFC uPD765 Manual      |    |  |  |

#### I. PRODUCT DESCRIPTION

The SYSTEMASTER is a microcomputer on a board. It incorporates all of the features required in a small computing system including a CPU, 64k bytes of RAM, serial and parallel I/O, and a floppy disk controller.

On board is a Z80A CPU which operates at 4 MHz for high-speed, efficient processing of information. The Z80A provides the capability to support many sophisticated applications. The interrupt structure of the Z80A is particularly important for systems which perform multiple tasks concurrently. The SYSTEMASTER utilizes the structured interrupt system of the Z80A in most of its I/O capabilities.

The on-board memory of SYSTEMASTER can provide up to 8k bytes of storage in EPROM/ROM and 64k bytes of RAM. The standard SYSTEMASTER is set up for 2k bytes of EPROM (to be used for on-board initialization routines) and 64k bytes of RAM. Options are available allowing the RAM to be bank switched.

Providing two independent serial ports, the Z80A SIO provides RS232C-compatible serial ports which can be operated under interrupt control. Both serial ports include full handshaking for connection to external devices as a printer, CRT terminal, or MODEM.

Also on board is a counter-timer chip which provides software-settable clocks for both serial ports and a real time clock. The real time clock is used by the software to provide timekeeping functions. It normally functions under interrupt control requiring a minimum of overhead. This real time clock can be used by software for any time-related functions, such as time dating of files, a stop watch or timing loops for external operations.

The Z80A PIO provides two parallel ports. One of these two ports is bidirectional with 8 data and 4 handshake lines. Normally this port is configured as a printer output, but because it is under software control, it can be reconfigured by the user to be a device input or a truly bidirectional port. The second parallel port has 8 data lines available which can be set independently to be input or output lines.

Using the NEC 765AC FDC and Zilog Z80 DMA ICs, SYSTEMASTER provides single- and double-density data storage on both miniand maxi-floppy disk drives providing capabilities which minimize the overhead burden on the CPU and software. Some of these capabilities are: single- and double-density data transfer under software control; performance of simultaneous seek operations on all drives connected to the system; IBM compatible formatting for ease of information exchange with controllers using similar

operating system software; compatibility with both single- and double-sided drives; ANSI standard 50 pin disk drive connector; automatic reading of sequential sectors on a diskette; automatic reading of both tracks of a two-sided diskette; automatic error-checking detected via CRC; under software control, possible selection of sector size to be 128, 256, 512, or 1,024 bytes.

The floppy disk control section of SYSTEMASTER also incorporates a phase-locked oscillator (PLO) which is used to stabilize the separated information and clock for precise data recovery.

A reset-jump circuit on SYSTEMASTER makes the CPU jump to the EPROM software on board whenever the system reset button is activated. This is useful for systems which do not have a front panel. For systems with a front panel, reset-jump will override the functions of the front panel. Also, incorporated as part of the reset-jump circuit, a power-on-clear function is included which automatically generates a reset when power is first applied.

SYSTEMASTER can be used as a cost effective stand-alone microcomputer board or as the basis for a high-performance multi-user multi-processing system.

#### II. SPECIFICATIONS

Central processor: Z80A CPU - 4 MHz operation.

Memory: 64k bytes dynamic RAM, bank selectable. Uses 64k bit x 1 devices, 200nS (or faster), 128 cycle refresh.

Serial: Z80A SIO - 2 RS232C, independent operation. Speeds from 110 to 19200 baud.

Timer: Z80A CTC - 4 channels, 2 used for serial ports, 2 used for real-time clock.

Parallel: Z80A PIO - 1 bidirectional port with 4 handshake lines, 1 port with 8 independent input or output lines.

Floppy disk controller: NEC uPD 765AC, single- or double-density and single- or double-sided operation, mini- or maxi-drives, ANSI standard 50 pin connector, IBM compatible format.

DMA: Z80A DMA controller handles floppy disk transfers

Disk data transfer rates:

Single density 5-1/4" - 125k bits/sec 8" - 250k bits/sec Double density 5-1/4" - 250k bits/sec 8" - 500k bits/sec

EPROM/ROM: 2716, 2732, 2764, 2316, 2332, 2364; up to 8k bytes total.

RFSH\* S-100 bus signals: A0-A15 pHLDA HOLD\* DODSB\* CDSB\* **CLOCK** INT\* **sHLTA** DATA IN ADSB\* sINP DATA OUT P0C\* sINTA MWRITE RDY sM1 NMI\* RESET\* **sMEMR** pSYNC s0UT pSTVAL\* sW0\* XRDY pWR\* SDSB\* pDBIN sXTRO\* SLAVE CLR\*

Note: SYSTEMASTER does not provide 8080-type I/O addressing; only the lower 8 address lines contain the I/O address.

Dimensions: 5.05" x 10.0", excluding edge connector.

Power requirements: +8v @ 2.0 amp, +16v @ 50mA, -16v @ 50mA.

Workmanship conforms to the requirements of MIL-STD-454.

Forced air cooling is required.

#### III. INSTALLATION

Upon receipt of SYSTEMASTER, check the shipping package for signs of abuse which may indicate possible damage. Check the board physically to look for any parts which may have been damaged during shipping. If any diskettes were shipped with SYSTEMASTER, check the diskettes for signs of damage which might be any bending or signs of a sharp object placed against the diskettes. Diskettes are quite fragile and any warping of the surface of the diskette will render it inoperative. Notify the shipper of any damage.

SYSTEMASTER is ready for immediate use upon receipt. It requires only that the peripherals which will be used with it be connected to the appropriate female connector which will then plug into the headers along the top of the board. For the particular connections required, see the section entitled "Peripheral Connections."

SYSTEMASTER need only be plugged into a standard S-100 bus for power and it will be functional, able to utilize the peripherals connected to it with the memory on board. The SYSTEMASTER needs to be in a well ventilated area due to the high density of IC's on board. Ideally, the board should be mounted vertically in a stream of air which will be moving across the face of the board. Whatever the mounting position, forced-air cooling is mandatory. Bring peripheral cables neatly away from the board with enough slack to prevent any tension being applied to the cable, as this may cause the cable to separate from its crimp connection causing intermittent problems.

For serial console devices, SIO A is the primary port. With the standard software, SIO A can determine the baud rate of a carriage return and thus set the appropriate speed automatically after a reset. The serial speed must be a standard value between 110 and 19200. Also, SIO A requires the handshake lines of the RS-232-C interface before it will function. See "Serial Ports" for further information.

Some versions of SYSTEMASTER do not have RAM on board. If no RAM is on-board, it must be supplied by the user. Care must be exercised in choosing the right RAM device for use on the board.

## 3.1 Peripheral Connections

## Serial Ports

SIO A and SIO-B

|   |                 |                  |                |                 |                  | (20)            |    |

|---|-----------------|------------------|----------------|-----------------|------------------|-----------------|----|

| 2 | 4               | 6                | 8              | 10              | 12               | 14<br>DTR<br>IN | 16 |

|   | (2)             | (3)              | (4)            | (5)             | (6)              | (7)             |    |

| 1 | 3<br>DATA<br>IN | 5<br>DATA<br>OUT | 7<br>RTS<br>IN | 9<br>CTS<br>OUT | 11<br>DSR<br>OUT | 13<br>GND       | 15 |

EIA pins shown in parentheses.

These are the connections going into channels A and B of the SIO chip. In this configuration, each channel appears as a data communication device and will connect to a terminal or a printer.

IN and OUT refer to data direction with respect to the SYSTEMASTER. Data from an external device is IN to SYSTEMASTER, and data to an external device is OUT.

CTS (Clear To Send) and DSR (Data Set Ready) are outputs to the external device and are at a positive voltage levels when the SIO channel is ready to function. RTS (Request To Send) and DTR (Data Terminal Ready) are inputs which must be at a positive voltage level for the SIO channel to function if the Auto Enables option is activated through software. This option is normally enabled in the standard SYSTEMASTER software.

Either channel can be crimp-connected to a 25-pinRS-232C connector by aligning pin 1 of the cable from the SYSTEMASTER connector with pin 1 of the 25 pin RS-232C connector. In this configuration, the channel connects directly to a terminal or printer. To connect to a MODEM, the signals must be connected as follows:

| SYSTEMASTER | EIA   | Direction | Function                  |

|-------------|-------|-----------|---------------------------|

| Pin #       | Pin # |           |                           |

| 5           | 2     | OUT       | Data to MODEM             |

| 3           | 3     | IN        | Data to SYSTEMASTER       |

| 11          | 4     | OUT       | RTS (Request To Send)     |

| 14          | 5     | IN        | CTS (Clear To Send)       |

| 7           | 6     | IN        | DSR (Data Set Ready)      |

| 13          | 7     |           | Signal Ground             |

| 9           | 20    | OUT       | DTR (Data Terminal Ready) |

IN refers to data sent to SYSTEMASTER, and OUT refers to data sent to the  $\mbox{MODEM}\mbox{.}$

Note: If the terminal or printer does not provide RTS and DTR, pins 4, 5, and 20 on the terminal side of the RS-232C male connector must be jumpered together. This ensures that the required handshake signals to the SIO port are provided. If the AUTO ENABLES feature of the SIO is not enabled this is not required. In the standard software provided, AUTO ENABLES is enabled.

### EIA Serial Data Transfer Protocol

Prior to sending or receiving data, the four handshake lines should be active low. However, the SIO will allow control of its receive and transmit functions independently. If the "Auto Enables" function of the SIO channel is enabled (standard), the SIO will not send data until DTR is low. (This function is labelled "CTS" on the SIO chip.) This is handy for buffered printers which need to stop receiving data until the buffer is printed. By pulling DTR high, the printer will stop the flow of data from the SIO. When it is ready to receive more data, it pulls DTR low. Similarly, if "Auto Enables" is enabled, the SIO will not accept information until RTS is low. (This functionis labelled "DCD" on the SIO chip.) This is primarily used with a communications link where, if signal conditions deteriorate, the data may be garbled.

In summary, the handshake lines provide a convenient means of controlling the flow of information in a serial channel. If any line goes high, transfer ceases.

## RS-232C Voltage Levels

A logic high (a binary ONE), or marking condition, is any voltage less than -3 volts to a minimum of -25 volts. A logic low (a binary ZERO), or spacing condition, is any voltage greater than +3 volts to a maximum of +25 volts. Any level between -3 and +3 volts is undefined. This is called the transition region. The maximum transition time between bit cells is four per cent of the basic clock period. The maximum voltage rate of change (slew rate) is 30 volts/uSec. Thus the maximum RS-232C transmission

speed, based on voltage swings of -12 to +12 volts, is 50,000 band.

## Serial Data Timing

Prior to transmitting data the signal line is held high, or marking. It goes low(spacing) to indicate the start of a character. The bits representing the character are then sent Least Significant Bit first, then a parity bit (if used), and finally 2 stop bits. The stop bits indicate the end of the character and are always logic ONEs. The standard SYSTEMASTER is set up for 8 data bits, no parity, and 2 stop bits.

The value of each character bit is held for the entire length of each bit cell. The length in time of each bit cell is the basic clock period, equal to the reciprocal of the baud rate. Thus for 9600 baud, each bit cell is 104 uSec long (.0001041 Sec=1/9600).

## Parallel Ports

|             |         |          | F        | PIO A       |         |           |             |             |

|-------------|---------|----------|----------|-------------|---------|-----------|-------------|-------------|

| 2<br>RESET* | 4       | 6<br>+5  | 8<br>GND | 10<br>B STB | 3 E     | 12<br>RDY | 14<br>A STB | 16<br>A RDY |

| 1<br>D7     | 3<br>D6 | 5<br>D5  | 7<br>D4  | 9<br>D3     |         | 11<br>D2  | 13<br>D1    | 15<br>D0    |

|             |         |          | ſ        | olo B       |         |           |             |             |

|             |         | 2<br>GND | 4        | 6<br>D1     | 8<br>D2 | 10<br>D0  |             |             |

|             |         | 1<br>D3  | 3<br>D4  | 5<br>D7     | 7<br>D6 | 9<br>D5   |             |             |

These are the connections into the PIO chip. The PIO chip has two parallel ports, A and B. As configured, PIO A may be used as an input, output, bidirectional or control port with four handshake lines. PIO B is the same except that it does not have bidirectional capabilties or handshake lines.

## The signals are:

DO - D7 8 data lines

A STB Strobe input pulse from a device. Depending on the mode of operation, it means:

- 1. Output mode: Positive edge of this strobe is issued by the device to acknowledge the receipt of data made available by PIO A.

- 2. Input mode: The strobe is issued by the device to load data from the device into PIO A.

- 3. Bidirectional mode: Same as 1, except output data are present only while A STB is low.

- 4. Control mode: The strobe is inhibited internally.

A RDY Ready output to a device. Depending on the mode of operation, it means:

- 1. Output mode: Indicates that the data bus is stable for transfer to the device.

- 2. Input mode: When active, it indicates that PIO A is ready to accept data from the device.

- 3. Bidirectional mode: Same as 1.

- 4. Control mode: Always in a low state.

RESET\* The active-low reset line on the SYSTEMASTER.

This can be used to reset a hard disk connected to PIO A.

B STB Used when PIO A is in the bidirectional mode; strobes data from the device into PIO A.

B RDY Used when PIO A is in the bidirectional mode; it goes high to indicate that PIO A is ready for data from the device.

The software supplied by Teletek allows PIO A to be set up as an input port or an output port. PIO B is set up in the control mode with all eight data lines available individually as input or output lines.

## Floppy Disk Drive

| Ground<br>Pin # | Signal<br>Pin # | Input - I<br>Output - O | Description          |

|-----------------|-----------------|-------------------------|----------------------|

| 1               | 2               | 0                       | Above track 43       |

| 3               | 4               | _                       | Not used             |

| 1<br>3<br>5     | 6               | -                       | Not used             |

| 7<br>9          | 8               | 0                       | Above track 43       |

| 9               | 10              | I                       | Dual sided           |

| 11              | 12              | -                       | Not used             |

| 13              | 14              | 0                       | Head 1               |

| 15              | 16              | -                       | Not used             |

| 17              | 18              | 0                       | Head load            |

| 19              | 20              | I                       | Index                |

| 21              | 22              | I                       | Ready                |

| 23              | 24              | -                       | Not used             |

| 25              | 26              | 0                       | Drive select O       |

| 27              | 28              | 0                       | Drive select l       |

| 29              | 30              | 0                       | Drive select 2       |

| 31              | 32              | 0                       | Drive select 3       |

| 33              | 34              | 0                       | Direction            |

| 35              | 36              | 0                       | Step pulse           |

| 37              | 38              | 0                       | Write data           |

| 39              | 40              | 0                       | Write gate           |

| 41              | 42              | I                       | Track ÖO             |

| 43              | 44              | I                       | Write protected      |

| 45              | 46              | I                       | Read data, composite |

| 47              | 48              | -                       | Not used             |

| 49              | 50              | 0                       | Motor control        |

Input/Output are referenced to SYSTEMASTER. Input is a signal from the disk drive to SYSTEMASTER, and output is a signal to the disk drive.

More detailed information regarding floppy disk drive interfacing is available in appendix B. Please refer to that section of the manual when installing disk drives on the SYSTEMASTER.

#### 3.2 Options

### Write Compensation

To help compensate for the shifting of data bits during the read process of the floppy disk drive, the write data are compensated. This is particularly critical for double-density operation. Different drives require different amounts of write compensation. The symptoms of too much or not enough write compensation are as follows: 1. Too much write compensation shows up as read errors (usually CRC) in the outer tracks (0-42); 2. Not enough write compensation shows up as read errors in the inner tracks (43-76).

SYSTEMASTER provides selectable compensation for both 5 1/4" and 8" drives in the following combinations:

| Jumper |     |     |      | Compensation   |                 |  |

|--------|-----|-----|------|----------------|-----------------|--|

|        | 0P0 | 0P1 | OP 2 | 5 1/4"         | 8"              |  |

|        | 0   | 0   | 0    | None           | None            |  |

|        | 1   | 0   | 0    | None           | 125 nSec        |  |

|        | 0   | 1   | 0    | None           | 250 nSec        |  |

|        | 1   | 1   | 0    | 250 nSec       | 125 nSec        |  |

|        | 0   | 0   | 1    | 250 nSec       | 250 nSec        |  |

|        | 1   | 0   | 1    | 500 nSec       | 125 nSec        |  |

|        | 0   | 1   | 1    | 500 nSec       | 250 nSec        |  |

|        | 1   | 1   | 1    | Illegal, no wr | ite data output |  |

A 0 for 0P0-2 indicates the jumper is in place, while a 1 indicates the option pins are open.

Compensation is automatically switched as the on-board drive size control is switched from  $5\ 1/4$ " to 8" drives.

Compensation depends on the recommendations of the drive manufacturer. Both 5 1/4" and 8" drives usually require 250 nSec compensation.

Track 43 Selectable Compensation

In addition to the above options, SYSTEMASTER provides one more: if the OP3 jumper is in place, the compensation for tracks O-42 will be one step less than that in the above table. At track 43 and higher, write compensation will be equal to the table value. This option is provided because most drives require more compensation on the inner tracks where the recording density is higher. For 5 1/4" drives which do not have more than 42 tracks, select compensation one step greater than that required.

For example, assume an 8" drive which requires 250 nSec compensation, and a 5 1/4" drive with 40 tracks which requires 250 nSec compensation. Option jumper OP3 is in place:

Select OPO=0, OP1=1, OP2=1

At Tracks 0-42, 5 1/4" compensation is 250 nSec, and 8" compensation is 125 nSec. For tracks 43 and above, the 8" drive will have 250 nSec compensated data.

#### Extended Head Load

The uPD-765AC floppy disk controller has a maximum head unload time of 240 mSec. In some applications this will cause an undue amount of head loading and unloading. To increase this head unload time and reduce the number of head load actions, a 74LS123 monostable can be wired into the head drive circuit. With the addition of a 6 volt capacitor, the head unload time is extended. This increases the life of the media and the heads where there would normally be a great deal of head load activity. The following table gives the effective head load time for several different capacitor values:

| Capacitor | (uF) | Head | Load | Time | (sec) |

|-----------|------|------|------|------|-------|

| 10        |      |      | 0.5  |      |       |

| 30        |      |      | 1.4  |      |       |

| 50        |      |      | 2.3  |      |       |

| 70        |      |      | 3.2  |      |       |

| 90        |      |      | 4.1  |      |       |

| 110       |      |      | 5.0  |      |       |

| 130       |      |      | 5.9  |      |       |

| 150       |      |      | 6.8  |      |       |

| 170       |      |      | 7.7  |      |       |

| 190       |      |      | 8.6  |      |       |

| 210       |      |      | 9.5  |      |       |

| 230       |      |      | 10.4 |      |       |

| 250       |      |      | 11.3 |      |       |

|           |      |      |      |      |       |

The time values are approximate (since normally resistor values are  $\pm$  10% and capacitor values  $\pm$  20%) and are arrived with the following equation: HLT =  $(45 \times C)/(1E03)$ , where C is in microFarads.

To enable the head load option, jumper option pin E-19 to E-20 and install the desired capacitor value at location C-12. If this option is not desired then pin E-19 should be connected to E-18.

Channels 2 and 3 of the CTC are ganged together to provide a 1-second interrupt real-time clock. Channel 2 is programmed in the timer mode, pre-scaler set to 256, time constant set to 125. Channel 3 is set to the counter mode, time constant set to 125, and interrupt enabled. For a multi-user operating system which requires a fast clock interrupt, enable the interrupt for channel 2 also. The interrupt routine for channel 2 can count down to provide periods which are integral multiples of the 8 millisecond interrupt.

### EPROM/RAM Options

The on-board ROM socket can accommodate 24 or 28-pin EPROMs or ROMs occupying 2k, 4k, or 8k bytes of memory space. This ROM can originate at 0000H, E000H, F000H, or F800H depending on the setting of the option jumpers on LA-5:

## **ROM Memory Space Options**

| ROM       | Origin | End   | 4k | Jumpers                |

|-----------|--------|-------|----|------------------------|

| 2316,2716 | 0000H  | 07FFH |    | E14 to E16, E15 to E17 |

| 2332,2732 | 0000H  | 0FFFH |    | E14 to E16, G to E17   |

| 2364,2764 | 0000H  | 1FFFH |    | G to E16, G to E17     |

| 2316,2716 | F800H  | FFFFH | 4k | E14 to E16, E15 to E17 |

| 2332,2732 | F000H  | FFFFH |    | E14 to E16, E13 to E17 |

| 2364,2764 | E000H  | FFFFH |    | E13 to E16, E13 to E17 |

The type of ROM used determines the socket and jumpers used at the socket:

| ROM  | Size | Socket | Jumpers    |            |           |

|------|------|--------|------------|------------|-----------|

| 2316 | 2k   | 24 pin | E5 to E8,  | E6 to E10, | E7 to E12 |

| 2332 | 4k   | 24     | E5 to E11, | E6 to E10, | E7 to E12 |

| 2364 | 8k   | 24     | E5 to E9,  | E6 to E12, | E7 to E11 |

| 2716 | 2k   | 24     | E5 to E8,  | E6 to E10, | E7 to E12 |

| 2732 | 4k   | 24     | E5 to E11  | E6 to E10, | E7 to E12 |

| 2764 | 8k   | 28     | E5 to E11. | E6 to E10. | E7 to E12 |

The chip select options for the 2316 and 2332 must be specified as follows for the above jumper connections:

| 2316 | Pin 18 active low  | *** , |

|------|--------------------|-------|

|      | Pin 20 active low  |       |

|      | Pin 21 active high |       |

| 2332 | Pin 18 active low  |       |

|      | Pin 20 active low  |       |

Note: when the 24-pin 2364 is used, underlying RAM cannot be written when the ROM is enabled.

Except for the 24-pin 2364, when the ROM is enabled, either during reset-jump or otherwise, the underlying RAM can be written but not read. Memory other than that occupied by the ROM can be accessed normally. Thus on reset the ROM monitor could copy itself into RAM then disable the ROM and continue execution from RAM.

#### RAM Select

SYSTEMASTER contains 64k bytes of RAM. This RAM is partitioned into a fixed and a selectable block. The selectable block can be disabled allowing CPU access to additional external memory. The fixed block is always resident in the CPU memory space. This combination of fixed and selectable memory accommodates such multi-user operating systems as MP/M from Digital Research, which requires a fixed block of RAM for the operating system.

The size of the fixed block of RAM can be varied by option jumpers AJ-1, 2, and 3:

| Fixed Block Size | Range       | Jumpers              |                                     |

|------------------|-------------|----------------------|-------------------------------------|

| 32k              | 8000H-FFFFH | AJ-1<br>AJ-2<br>AJ-3 | Open<br>Open<br>Open                |

| 16k              | COOOH-FFFFH | AJ-1<br>AJ-2<br>AJ-3 | Open<br>Open<br>Connected           |

| 8k               | E000H-FFFFH | AJ-1<br>AJ-2<br>AJ-3 | Open<br>Connected<br>Connected      |

| 4k               | F000H-FFFFH | AJ-1<br>AJ-2<br>AJ-3 | Connected<br>Connected<br>Connected |

The selectable block of RAM occupies the memory space from 0000H up to the fixed block of RAM. The selectable block is enabled when /RAMEN islow. (/RAMEN is bit 7 of the control register.) When disabled, the selectable block of RAM is not affected by memory accesses in its memory space.

Note: The on-board RAM cannot be accessed by off-board temporary bus masters.

#### IV. THEORY OF OPERATION

SYSTEMASTER is a single-board computer for the S-100 bus. It contains 2k- 8k bytes of ROM, 64k bytes of RAM, a flexible-disk controller, two parallel ports, two serial ports, a DMA controller, a CTC, and a CPU. With appropriate software, SYSTEMASTER comprises a complete stand-alone single-user computer. The following discussion details the operation of the various functional areas of SYSTEMASTER.

## Central Processor Operations

The heart of SYSTEMASTER is a 4 MHz Z80A. It provides the intelligence to operate the on-board peripherals and to provide the information interchange to the S-100 bus. Connections to the bus are made through tri-state buffers and control logic to provide the correct timing signals and status signals to operate other peripherals within the microcomputer.

#### CPU Clock Driver

Three sections of U-58 drive the processor clock line. Resistor R-2 pulls this line up to +5 volts, while R-3 controls the low-going overshoot. On an oscilloscope, with a high-impedance probe connected to TP-1 and a short ground line connected to SYSTEMASTER adjacent to TP-1, the low-going clock signal should not overshoot ground potential by more than 0.3 volts. The measuring oscilloscope must have a bandwidth of one gigahertz. TP-1 is between J-5 and J-2.

## Wait State Generator

The wait-state generator functions by holding the CPU wait input low until one clock cycle after MREQ from the CPU is active. U-53A, a J-K flip-flop, has its K input connected to MREQ from the CPU. The inverted state of MREQ connects to the Jinput. Initially, prior to a memory cycle, MREQ is high. This causes U-53A to clock its Q output low. When MREQ goes active, U-53's Q output is gated with MREQ low via U-28, an OR gate, and the output is gated with the desired state (M1, ROM, or all memory). If the current CPU cycle is the desired state, pin 8 of U-28 will be low, which in U-29, an AND gate, causes the wait input of the CPU to be low. On the next negative edge of the CPU clock, because MREQ is low and the J input of U-53A is now high, the Q output of U-53A will go high. This is gated to the wait input of the CPU allowing it to complete the cycle. U-53A resets itself at the end of the memory cycle when MREQ again goes inactive.

SYSTEMASTER incorporates a DMA controller to provide efficient, transparent flexible-disk data transfer without requiring CPU intervention. The DMA controller is a single-channel device which can execute only one series of operations at a time. Although it is connected to the 765 flexible-disk controller, when the 765 is idle the DMA controller can perform block moves of data between memory and I/O devices.

Interrupts can be enabled during DMA operations. Prior to a series of DMA data transfers the DMA controller must be set up as necessary for the particular operation desired. No CPU intervention is required during a DMA transfer process. At the completion of the series of data transfers the DMA controller will interrupt the CPU. At this time, the CPU performs any operations necessary to terminate the data transfer.

#### On-board Control Register

U-13, an octal D-type flip-flop, provides control for several areas of SYSTEMASTER. The output lines of U-13 are:

|     | Name<br>/RAMEN | Function When low, enables the selectable block of |

|-----|----------------|----------------------------------------------------|

| ·   | ,              | on-board RAM.                                      |

| 6   | /ROMEN         | With /JMP, controls the on-board ROM               |

| 5   | /JMP           | With /ROMEN, controls the on-board ROM             |

| 4   | /MOT           | When low, turns on the flexible-disk drive         |

|     |                | spindle motor                                      |

| 3   | /FL8           | When low, allows 8" flexible-disk data             |

|     |                | transfers. When high, 5 1/4" flexible-disk         |

|     |                | data transfers are enabled.                        |

| 0-2 | -              | Not presently used                                 |

All these bits are reset low when a reset pulse occurs. The control register bits are set simultaneously by a CPU output to port 1CH. The outputs follow the inputs directly.

## ROM-I/O Decoder

LA-5, a logic array, provides the logic necessary to access the on-board ROM, select I/O, and control the RAM data buffer. When the CPU accesses memory, LA-5 decodes the address and option lines to determine if the on-board ROM is being accessed. If the CPU is accessing ROM, the RAM data buffer is held inactive, otherwise it is enabled if LA-1 has determined that on-board-memory is to be accessed.

During an I/O operation, if the CPU address is less than 20H, the on-board I/O decoder is selected. If /Ml is active at the same time as /IORQ, an interrupt acknowledge cycle is in process and neither ROM, RAM nor I/O is selected.

#### Power-On Clear

SYSTEMASTER generates a reset pulse when power is applied, to automatically initialize the system. Thus during the start-up operation operator intervention is not required. To develop the power-on reset pulse, circuitry on-board SYSTEMASTER detects the first application of power: Capacitor C-26 is initially discharged. C-26 holds the plus input of U-17 (a dual comparator) low, which causes the output of U-17 to be low. The output of U-17 enables two drivers of U-6, a hex inverting bus driver, which pull RESET\* and SLAVE CLR\* low on the S-100 bus. In addition, the cutput of U-17 is buffered by U-18 to drive POC\* low. When C-26 charges above the level on the minus input pin of U-17, the output of U-17 goes high. RESET\* and SLAVE CLR\* are released and pulled high by resistors connected to +5 volts, and POC\* goes high. At this time the CPU on board SYSTEMASTER begins execution of the instructions in the on-board ROM. When power is turned off, diode D-1 discharges C-26 quickly to provide a reset action if power is shortly reapplied. (Such a sequence can occur during a temporary power outage.)

#### Reset-Jump

After a reset operation SYSTEMASTER begins execution of the instructions in the ROM to initialize the system. Because the ROM may reside at 0000H or a higher memory address, special circuitry enables the ROM independent of its actual location.

The outputs of U-13, an octal D-type flip-flop, the on-board control register, are cleared by a reset pulse. Therefore, outputs /JMP and /ROMEN are low. This combination causes LA-5, a logic array, to enable the ROM for any CPU memory access. If the ROM options are set for a ROM location at E000H, F000H, or F800H, the first instruction in the ROM should be an absolute jump to the ROM location plus three. For example, a SYSTEMASTER set up for a 2716 has the ROM options set for an address of F800H. The first instruction in the ROM is a jump to F803H. This sets the CPU program counter to the actual ROM address space.

After the CPU begins executing the ROM in the correct address space, RAM can be enabled by setting /JMP high if the ROM occupies high address space, or setting /ROMEN high if the ROM occupies memory starting at 0000H. /JMP is bit 5, and /ROMEN is bit 6 of U-13, the control register.

To summarize:

ROM is always enabled after a reset.

ROM at 0000H: Set /ROMEN nigh to enable RAM.

ROM at F000H or higher: CPU jump to ROM + 3, set /JMP high

to enable RAM.

#### Dynamic RAM Control

Logic Array LA-1 controls the access to the on-board dynamic RAM. A RAM cycle is started by /M1 going low, or by /MREQ active low in conjunction with /RD, /WR, or /RFSH. If the RAM-select options match /RAMEN and the option address jumpers, /MSTRT goes low. Both sections of U-19, a dual J-K flip-flop, are clocked active by the action of /MSTRT. U-19A activates the /RAS line of the dynamic RAM ICs. /RAS clocks the lower 8 bits of the memory address into the RAM ICs. U-19B sends a positive pulse into the delay line, U-47. The 20% output of the delay line resets U-19B to terminate the positive pulse, and in addition clocks U-54A. The output of U-54A causes the address multiplexers, U-42 and U-43, to select the upper 8 bits of the memory address.

When the positive pulse in the delay line reaches the 40% tap it clocks U-54B, which generates a /CAS signal to complete the RAM access. After the RAM access time has elapsed, data are stable at the RAM outputs. When the positive pulse in the delay line reaches the 100% tap, U-19A is reset which resets the /RAS signal. This allows the RAM RAS circuit to pre-charge in preparation for the next memory access.

As long as /CAS is low, the RAM outputs are stable. When the CPU terminates the memory request, LA-1 resets U-54 which returns the address multiplexers to the low-order address lines and resets the /CAS signal.

A memory write operation does not begin until /WR from the CPU is active. This ensures that the R/WR line to the RAM ICs is active when the RAM ICs are accessed. This precaution allows the DATA IN and DATA OUT lines of the RAM ICs to be connected together, simplifying the memory circuitry.

A refresh operation begins when /RFSH and /MREQ from the CPU are both active low. A normal memory cycle is started, but the address multiplexer and /CAS circuits are held idle. The CPU outputs a refresh address during this time to refresh one of 128 consecutive locations in the RAM necessary to retain data.

NOTE: An extended RESET\* or Wait State condition will cause a loss of refresh in the on board dynamic RAM.

#### Serial Ports

The Z80A SIO is used to generate two entirely independent serial ports. Both serial ports incorporate all the handshaking lines required by an RS232C datainterconnection device. Each channel of the SIO is driven by an independent section of the CTC. This means that baud rates for the two channels can be independently selected. In fact, the baud rates may range anywhere from 45 baud up to 19200 baud. These frequencies are determined during initialization of the CTC. The data lines to and from the SIO channels are buffered by RS232C level translators. These buffers are also inherently protected from short circuits on the external lines.

Both serial ports will interconnect with terminal equipment (printer, CRT terminal, etc) using standard insulation-displacement connectors. Connection to a MODEM requires a transposition of all six serial lines as required by the MODEM. When connecting to a synchronous MODEM, which provides the receive and transmit clocks, the clock inputs to SIO A must be connected to the MODEM:

SIO A clocks Jumper

Internal, CTC E22 to E21, E25 to E24 From MODEM E22 to E23, E25 to E26

The transmit and receive clocks for SIO A are provided by CTC channel 0. Those for SIO B are provided by CTC channel 1.

### Parallel Ports

The parallel ports consist primarily of the Z80A PIO. Port A is used as an 8 bit input, output or bidirectional port. The four handshaking lines of the PIO are used with port A. Normally, port A is configured as an output for such parallel items as a printer. Under software control, port A can be configured as an input or as a bidirectional port where input data and output data as well as direction are controlled by the four handshaking lines.

Port B of the PIO is used in a bit control mode. This port is normally used to provide individual control lines for interfacing to parallel devices such as hard disk drives.

### Floppy Disk Controller Operation

The heart of the flexible-disk controller is the NEC uPD765AC. Capable of single- and double-density, single- and double-sided 5 1/4" and 8" data recording, the 765 provides a flexible, reliable disk controller for SYSTEMASTER. Circuitry on board SYSTEMASTER supports the 765 in stabilizing the read data from the disk drive, compensating data written to the disk drive, and buffering status signals to and from the disk drive. The following discussion details the circuitry surrounding the 765.

The 765 has two drive-select outputs. U-49, a dual decoder, decodes USO and US1 from the 765 to develop four drive select signals.

To reduce the number of its pins the 765 multiplexes dual signals on four of its control lines. Pin 39 of the 765 selects the seek mode when high and the data read-write mode when low. One section of U-56, an inverting buffer, inverts the signal from pin 39 to enable the appropriate drivers when the 765 is in its seek mode. When in the seek mode, the 765 positions the disk drive head over the desired track on the diskette. In this mode, the 765 looks at the dual-sided and track O signals and outputs drive control signals to the direction and step lines. In the read-write mode, these four function lines become write-protect, write-fault, low-current (track greater than 42), and write-fault reset. As mentioned earlier, the output of the Seek/Read-Write pin selects the necessary signal lines.

#### 765 Interrupt

The 765 generates an interrupt request to the CPU when it detects an error or completes an operation. The 765 interrupt output on pin 18 is active high, thus it is inverted by U-57 and activates the output of U-7, a tri-state buffer. U-7 pulls down the CPU interrupt request line. When the CPU acknowledges the interrupt, LA-4 will pull down data line 0 if no other interrupts are active on SYSTEMASTER. Because the other data lines to the CPU have resistor pull ups to +5 volts, the CPU sees FEH on its data bus and will execute the absolute address stored at FEH in the interrupt table. The data input buffer from the S-100 bus is held inactive by LA-4 during the interrupt acknowledge operation when the 765 interrupt line is active.

#### Phase-Lock Loop

The read data from the disk drive may vary in frequency due to disk drive rotation speed variations. To maintain reliable read data, a phase-locked loop oscillator follows the frequency of the read data and provides a stabilized read clock for the 765. The read data pulses from the drive are applied first to U-23A, which provides a fixed pulse width for each data pulse to the 765. The read data pulses are also applied to U-23B, which generates a pulse whose width is one-fourth of the read data clock period. The output of U-23B is set by resistors driven by te outputs of LA-3. Depending on drive size and density, the pulse width generated by U-23B will be as follows:

| Drive Size | Density | U-23B Pulse Width |

|------------|---------|-------------------|

| 5 1/4"     | Single  | 2.0 uSec          |

| 5 1/4"     | Double  | 1.0 uSec          |

| 8"         | Single  | 1.0 uSec          |

| 8"         | Double  | 0.5 uSec          |

The voltage-controlled oscillator, composed of two sections of U-21 and transistor Q-3, oscillates at a nominal frequency of 2.0 MHz. Frequency dividers within LA-3 provide outputs that are 2 x the read data frequency and equal to the read data frequency. The output at the read data frequency is sent to the 765. The frequencies depend on drive size and density:

| Drive Size | Density | 2 x Frequency | 1 x Frequency |

|------------|---------|---------------|---------------|

| 5 1/4"     | Single  | 250 KHz       | 125 KHz       |

| 5 1/4"     | Double  | 500 KHz       | 250 KHz       |

| 8"         | Single  | 500 KHz       | 250 KHz       |

| 8"         | Double  | 1.0 MHz       | 500 KHz       |

In addition, LA-3 provides a write clock whose frequency is determined by drive size and density:

| Drive Size | Density | Write Clock Output |

|------------|---------|--------------------|

| 5 1/4"     | Single  | 250 KHz            |

| 5 1/4"     | Double  | 500 KHz            |

| 8"         | Single  | 500 KHz            |

| 8"         | Double  | 1.0 MHz            |

The output of U-23B and the inverted 2 x frequency from LA-3 are applied to U-22, a dual flip-flop connected as a phase detector. The outputs of U-22 will be active depending on the relative occurrence of the applied signals. These outputs are buffered by two sections of U-21 to eliminate amplitude variations. The summing junction of R-21 and R-23, nominally +2.1 volts, is filtered by C-17 and R-24 and applied to the input of an op-amp, U-44. The voltage at the junction of R-21 and R-23 will vary depending on the difference between the frequency of the voltage-controlled oscillator and the read data frequency. U-44 amplifies this error signal and changes the charging current into C-20 which changes the frequency of the voltage-controlled oscillator. Thus the oscillator is made to follow the frequency of the disk drive data.

The action of the phase-lock loop is such that the read data pulses will occur in the center of the high or low portion of the read data clock sent to the 765. This provides the maximum margin for error in disk read operations.

### PLL Adjustment

Variable resistor R-32 is provided to adjust the quiescent output voltage of U-44 which in turn controls the frequency of the oscillator. R-32 is adjusted to provide an oscillator frequency measured at TP-3 of 2.00 + or - 0.02 MHz. If the oscillator will not adjust to 2.00 MHz, either C-20 or U-21 must be changed. After adjustment, the output of U-44 must be 0.4 + or - 0.4 volt as measured at TP-2, adjacent to R-32.

#### Data Transfer

SYSTEMASTER flexible-disk data transfers are handled via the on-board DMA controller. The sequence of operations should be: set up the DMA controller for the # of bytes to transfer (the sector size) and the starting memory address for the transfer, and finally send the read or write command to the 765. When the DMA controller interrupts the CPU at the end of the data transfer, the interrupt routine must immediately issue a terminal count to the 765 by doing an input from port 14H.

The DMA controller accesses port 10H to transfer data to or from the 765. This port connects to the DACK (DMA acknowledge) pin of the 765.

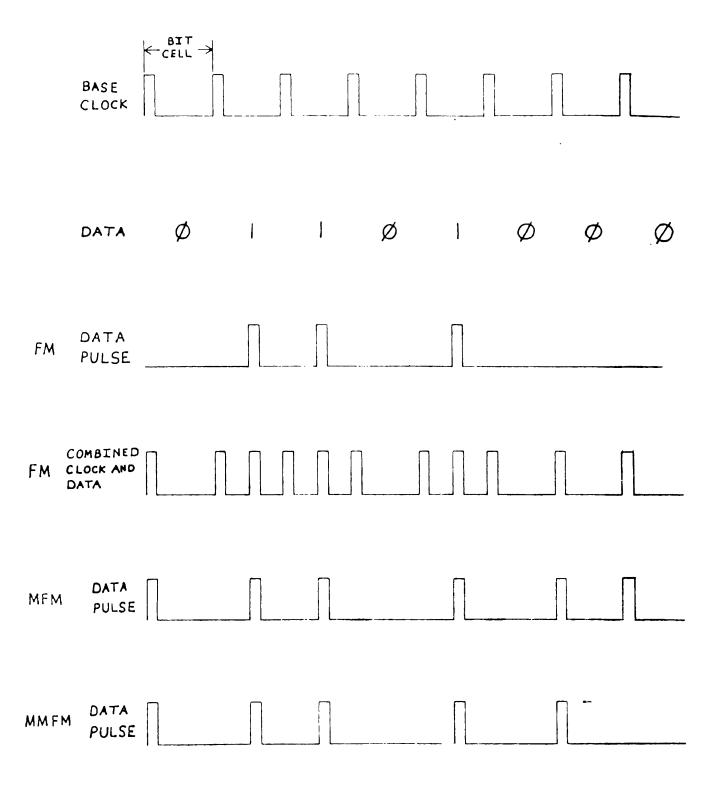

Physically, double density disk drives do not differ significantly from their single density counterparts. Improvements in double density record and playback heads and changes in mechanics often provide less expensive and more These changes are minor compared to the durable drives. differences in reading and writing functions. Figure 1 reviews encoding methods used in single and double density. The standard recording formats are EM (for frequency modulation), MFM (for modified frequency modulation-double density), and MMEM (for modified modified frequency modulation) which is a refinement of MFM. Line 1 of Figure 1 indicates the basic clock frequency which designates the bit cell in which information will be passed. The next line illustrates a sample of information; the line following shows the pulses which generate that information in a single- density FM format. Notice that information actually sent to and received from the drive is a combination of the basic clock frequency and data pulses. Refer to the next line which is MFM.

Here, only the data pulses will be sent to the drive and their orientation within the bit cell determines the value of that particular data pulse (a 1 or a 0). Every 0 is represented by a data pulse that coincides with the basic clock frequency. Every 1 is represented by a pulse that occurs midway between two clock pulses. Thus, when the data pulse occurs in the middle of a bit cell, it is a 1; when it occurs in the beginning of a bit cell, it is a 0. Look at the next line which represents MMFM.

This is a slight refinement of MFM; in this instance the data pulses once again represent 1's and 0's via their placement within the bit cell. However, the rules change slightly. If the preceding data pulse was a 0 and the present datum is a 0, then the data pulse will occur. If the last data pulse was a 1 and the present datum is a 0, the present data pulse does not appear. If the last data pulse was a 1 and the present datum is a 1, that data pulse appears. Every time there is a 1, a data pulse will appear in the middle of a bit cell. But whether or not a 0 data pulse occurs depends on the preceding datum. Note that the density of data pulses for MFM is almost exactly one-half the density of data pulses for FM. Thus, for the same density of pulses on the diskette, MFM will record twice as much information as FM. MMFM has slightly less dense data pulses than MFM, but its complexity of encoding and decoding outweighs the slight advantage it might enjoy due to slightly less density.

The basic clock frequency for FM ercoding is 250 KHz for an 8-inch diskette. When we delete the clock and leave only the data pulses in MFM, that clock rate changes to 500 KHz. The MFM data transfer rate is twice as fast as FM. The density and the speed are both doubled, which means that twice as much information can be stored in the same physical space and manipulated twice as fast.

## FIGURE 1 FLOPPY DISK DATA ENCODING

The SYSTEMASTER CPU is configured in interrupt mode 2. In this mode, a requesting peripheral generates an interrupt and when that interrupt is acknowledged, the CPU expects the peripheral device to place an 8 bit address vector on the data lines. The CPU then adds this 8 bit vector with another 8 bit register internal to the CPU to form a 16 bit absolute memory address. This address points to a 2 byte location in memory which contains the absolute address of the desired subroutine to service the interrupt. In the case of the Z80A DMA, SIO, PIO and CTC, the necessary interrupt vectors are loaded to internal registers during initialization. For the case of the floppy controller IC, the interrupt vector is simply composed of that vector formed by the pull-up resistors on the data lines, an FE. The Z80 peripheral IC's normally begin on an even memory location because bit 0 is always a 0 during their interrupt response. When a device external to the CPU requests an interrupt, the external device must provide an interrupt vector on the data bus when interrupt acknowledge status line goes active high. The Z80A peripheral IC's are series connected to provide priority interrupts. The last peripheral in the chain, namely the PIO, provides an interrupt enable signal for external devices. this line is high, interrupts are enabled for external requests. When this line is low, external devices must be prevented from generating a response to an interrupt acknowledge signal. The vector that external devices place on the bus, when combined with the internal high order vector of the CPU, must point to a location in memory which provides the absolute address of the subroutine used for servicing that particular interrupt.

#### S-100 Bus Interface

The signals generated by SYSTEMASTER are compatible with the proposed IEEE-696 standard. Logic array LA-4 transforms the Z-80 family status signals to those of the S-100 bus. In addition, LA-4 controls the data input bus driver, U-12, to prevent conflicts with on-board I/O and memory devices. If a conflict could occur, SYSTEMASTER ignores the off-board device.

SYSTEMASTER generates the S-100 standard memory write strobe by the logical equation: MWRT= pWR AND /SOUT.

In addition to the standard S-100 signals, SYSTEMASTER brings the Z-80 CPU refresh signal to pin 66 of the bus for those memory boards which need this signal.

U-5, a dual monostable, generates the pSYNC and pSTVAL\* signals. Whenever the CPU activates a status line (M1, MREQ, or IORQ), LA-4 outputs an active-low signal to trigger U-5A. The output of U-5A appears on the bus as pSYNC and also triggers U-5B. U-5B generates a pSTVAL\* signal whose active edge occurs after status is valid, and during the pSYNC pulse.

## SYSTEMASTER Port Assignments

| Port        | Device         | Function                            |

|-------------|----------------|-------------------------------------|

| ООН         | 012            | A-Data                              |

| 01          | it .           | A-Control                           |

| 02          | н              | B-Data                              |

| 03          | 11             | B-Control                           |

| 04          | PIO            | A-Data                              |

| 05          | "              | A-Control                           |

| 06          | O C            | B-Data                              |

| 07          | ŧI.            | 8-Control                           |

| 08          | CTC            | Channel O, SIO-A baud rate          |

| 09          | 11             | Channel 1, SIO-B baud rate          |

| 0A          | п              | Channel 2, Real-time clock          |

| 0B          | п              | Channel 3, Real-time clock-connects |

|             |                | to the output of Channel 2.         |

| OC          | 765            | Status register                     |

| OD          | 11             | Data                                |

| OE-OF       | и              | Not used                            |

| 10          | DACK           | DMA acknowledge to 765              |

| 11-13       | <del>1</del> 1 | Not used                            |

| 14          | TC             | Terminal count to 765               |

| 15-17       | H              | Not used                            |

| 18          | DMA            | DMA processor control registers     |

|             |                |                                     |

| 19-1B       | н              | Not used                            |

| 19-1B<br>1C |                | ,                                   |

#### V. IN CASE OF TROUBLE

If the SYSTEMASTER does not respond the first time it's connected, relax. Due to its complexity, there are many areas that may have inadvertently been overlooked. Take time to read the "Peripheral Connections" section. The following trouble-shooting guide lists the major functional areas of the SYSTEMASTER and some typical problems associated with each. Suggested solutions are offered for each. But remember: it is highly recommended that the entire manual be read.

Some important considerations:

SIO A, the console serial port, requires handshaking lines before it will function.

After reset, a carriage return must be the first character typed to establish the baud rate into SIO A. If the baud rate is less than 19,200, up to 6 carriage returns may be required.

Floppy drives must be able to seek even if not continually selected during seek operations. This usually means enabling a continuous stepper power option.

Dynamic memories must be set up according to the requirements for interfacing with a Z-80A CPU. Also, no wait states are inserted for system memory accesses with the standard SYSTEMASTER.

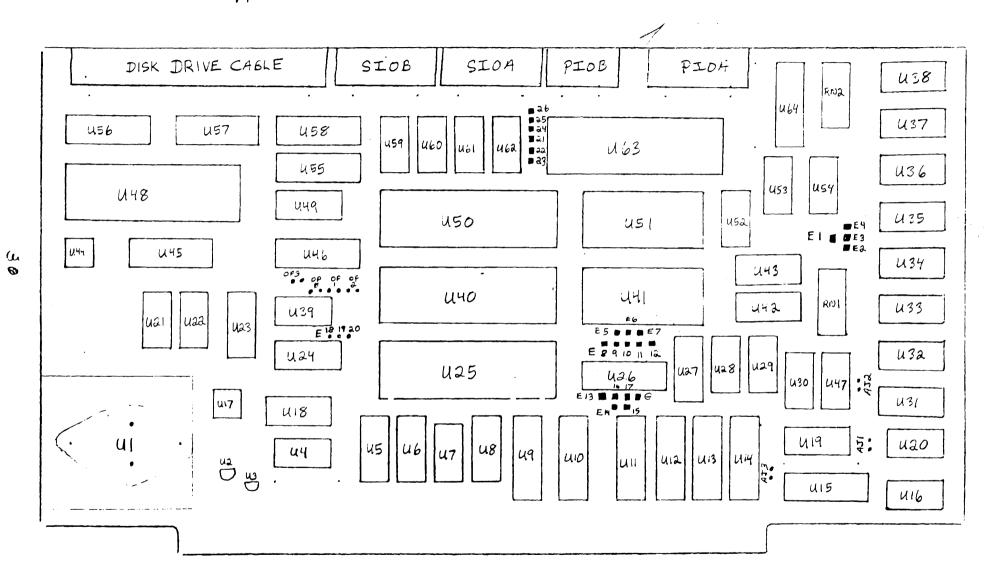

APPENDIX A SYSTEMASTER LAYOUT

#### APPENDIX B

#### SYSTEMASTER DRIVE INTERFACING

In controlling a disk drive from SYSTEMASTER, proper connections must be made to the disk drive in order for it to be operational. The drive options must be configured as outlined in the appropriate manufacturer's section following this introduction. Particularly important is the fact that the uPD-765 continuously polls all drives in the system to keep track of their status. With some drives this will interfere with their seek function (positioning of the head). Thus, most drives will have a stepper motor enable option, or simultanious seek option, that powers the stepper motor continuously, rather than just when the drive is selected. If the drive won't read initially, check for this option.

Drive interfacing deals with the proper connection of functional signals and the satisfying of electrical and mechanical requirements.

To help ease the shock of transition from the interchanging of various disk drives to other host controllers, a standard known as ANSI was developed which standardized the means of intercommunication between disk drive and host controller by specifying power requirements and voltage levels, edge connector and cable specifications, and specific pin numbers of the connector to particular functional signals.

## ANSI Standards

Functional signals assigned to specific pin numbers of the connector are shown on the next page for a 5.25-inch disk drive and an 8-inch disk drive.

## ANSI Standard for 5.2

| Signal<br>Pin No. | Ground<br>Pin No. | Signal                       |

|-------------------|-------------------|------------------------------|

| 2                 | 1                 | Not assigned (Head load)     |

| 4                 | 3                 | In use control               |

| 6                 | 5                 | Drive select 3 (Ready)       |

| 8                 | 7                 | Index/sector                 |

| 10                | 9                 | Drive select O               |

| 12                | 11                | Drive select 1               |

| 14                | 13                | Drive select 2               |

| 16                | 15                | Motor on                     |

| 18                | 17                | Direction select             |

| 20                | 19                | Step                         |

| 22                | 21                | Composite write data         |

| 24                | 23                | Write gate                   |

| 26                | 25                | Track Ö                      |

| <b>2</b> 8        | 27                | Write protected              |

| 30                | 29                | Composite read data          |

| 32                | 31                | Side one select              |

| 34                | 33                | Disk change (Drive select 3) |

## ANSI Standard for 8-Inch Drive

| Signal<br>Pin No. | Ground<br>Pin No. | Signal               |    |

|-------------------|-------------------|----------------------|----|

| 2                 | 1                 | Head current switch  |    |

| 4<br>6            | 3                 | Not assigned         |    |

| 6                 | 5                 | Not assigned         |    |

| 8                 | 3<br>5<br>7<br>9  | Drive busy           |    |

| 10                | 9                 | Two-sided            |    |

| 12                | 11                | Disk change          |    |

| 14                | 13                | Side one select      |    |

| 16                | 15                | In use control       |    |

| 18                | 17                | Head load            |    |

| 20                | 19                | Index                |    |

| 22                | 21                | Drive ready          |    |

| 24                | 23                | Sector               |    |

| 26                | 25                | Drive select O       |    |

| <b>2</b> 8        | 27                | Drive select 1       |    |

| 30                | 29                | Drive select 2       |    |

| 32                | 31                | Drive select 3       |    |

| 34                | 33                | Direction select     |    |

| 36                | 35                | Step                 |    |

| 38                | 37                | Composite write data |    |

| 40                | 39                | Write gate           |    |

| 42                | 41                | Track O              |    |

| 44                | 43                | Write protected      | •- |

| 46                | 45                | Composite read data  |    |

| 48                | 47                | Separated read data  |    |

| 50                | 49                | Separated read clock |    |

|                   |                   |                      |    |

## Electrical

- 1. Multi Drop Bus: Multiple drives may be connected to the same host controller as shown in Figure 1. Only one drive is logically connected to the interface at a time.

- 2. Voltage Levels (as measured at the driver) Logical true Active low +0V to +0.4V Logical false Active high +2.4V to +5.5V

- 3. Termination: Signal lines shall be terminated by one of the two resistive networks illustrated below, whether the termination occurs at the drive or the host, but only at the terminal point of a signal.

+5V +5V

220 Onms 150 Onms

OR

330 Onms

- 4. Signal Drivers: The signal drivers should have open collector output stages capable of sinking a minimum of 40mA at logical true (low) level, with maximum voltage of 0.4V as measured at the driver output.

- 5. Signal Receivers: The signal receivers should not unduly load the multi drop bus and should not require more than 40uA current from the driver at input high (2.4V) nor supply more than 1.6mA to a current sink at input low (0.4V) level.

Interconnecting Cable

Conductor Size

Copper- AWG #30 or larger for solid conductor AWG #28 or larger for stranded conductor

Non-copper- Sufficient size as to yield a dc resistance not to

exceed 110 Ohms per 1000 ft. per conductor.

Stray capacitance- Capacitance between one wire in a cable and all others in the cable with all others connected to ground shall not exceed 40pF/ft. and the value shall be reasonably uniform over the length of the cable.

Mutual pair capacitance- Capacitance between one wire of the pair to the other shall not exceed 20pF/ft. and the value should be reasonably uniform over the length of the cable.

## Mini-Floppy Drives

Use of mini-floppy drives requires the use of a special 50 to 34 pin adapter board. The following is a diagram of this board and its options.

Eight inch to five and a quarter inch drive p.c. adaptor board:

J1 is the 50 pin connector and J2 is the 34 pin connector.

J2-10, 5.25" DSO (8)

## Options:

- 1) Pad 0 to 1 8" drive select 1 connected to 5.25" drive select 1.

- 2) Pad 1 to 2 8" drive select 2 connected to 5.25" drive select 1.

- 3) Pad 2 to 3 8" drive select 3 connected to 5.25" pin 6. Normally this pin is drive select 3 for 5.25" drives but is the READY signal for Micropolis drives.

- 4) Pad 2 to 4 8" drive select 3 connected to 5.25" pin 34. This pin is drive select 3 for Micropolis drives or READY for Pertec drives.

- 5) Pad 5 to 3 8" READY connected to 5.25" pin 6. This pin is the READY pin for Micropolis drives.

- 6) Pad 5 to 6 8" READY connected to GROUND. Since most 5.25" v i r do not provide a READY signal it is neccessary to ground

## Mini-Floppy Drives

Use of mini-floppy drives requires the use of a special 50 to 34 pin adapter board. The following is a diagram of this board and its options.

Eight inch to five and a quarter inch drive p.c. adaptor board:

J1 is the 50 pin connector and J2 is the 34 pin connector.

#### Options:

- 1) Pad 0 to 1 8" drive select 1 connected to 5.25" drive select 1.

- 2) Pad 1 to 2 8" drive select 2 connected to 5.25" drive select 1.

- 3) Pad 2 to 3 8" drive select 3 connected to 5.25" pin 6. Normally this pin is drive select 3 for 5.25" drives but is the READY signal for Micropolis drives.

- 4) Pad 2 to 4 8" drive select 3 connected to 5.25" pin 34. This pin is drive select 3 for Micropolis drives or READY for Pertec drives.

- 5) Pad 5 to 3 8" READY connected to 5.25" pin 6. This pin is the READY pin for Micropolis drives.

- 6) Pad 5 to 6 8" READY connected to GROUND. Since most 5.25" drives do not provide a READY signal it is neccessary to ground this line.

- 7) Pad 7 to 8 8" drive select 0 connected to 5.25" drive select 0.

- 8) Pad 9 to 8 8" drive select 2 connected to 5.25" drive select 0.

## Micropolis 1015 Disk \_\_\_\_

Required drive configuration:

1. DS1-4 Select appropriate drive address

2. HDLD Enable this option

Install the termination network only in the last drive in the daisy chain.

Each drive requires 12 volts at 1.3A and 5 volts at 0.5A.

Required Pre-write Compensation: 250 ns.

Note: Since the Micropolis drive does not follow the ANSI standard several changes are neccessay on the p.c. adaptor board as follows:

- 1. Cut the trace between pads 2 and 3.

- 2. Cut the trace between pads 5 and 6.

- 3. Add a jumper between pads 2 and 4.

- 4. Add a jumper between pads 3 and 5.

## Shugart SA-400 Disk Drive

Required drive configuration:

1. HL Jumper

2. DS-1,2,3 Select appropriate drive address

3. MX Open

4. MH Open

Install the termination network only in the last drive in the daisy chain.

Each drive requires 12 volts at 1.8A and 5 volts at 0.7A.

Required Pre-write Compensation: none. (If pre-write compensation is wanted use 250 ns.)

### MPI B-51/52 Disk Drive

Required drive configuration:

| 1. | T1    | Jumper                           |

|----|-------|----------------------------------|

| 2. | T2-T4 | Select appropriate drive address |

| 3. | T5    | 0pen                             |

| 4. | T6    | 0pen                             |

| 5. | T7    | 0pen                             |

Install the termination network only in the last drive in the daisy chain.

Each drive requires 12 volts at 1.5A and 5 volts at 0.7A.

### Caldisk 143M Disk Drive

Required drive configuration:

| 1.  | DS A    | Closed (DS = Dip Switch)        |

|-----|---------|---------------------------------|

| 2.  | DS B    | Open '                          |

| 3.  | DS C    | 0pen                            |

| 4.  | DS D    | 0pen                            |

| 5.  | JPR1    | 0pen                            |

|     | JPR2    | 0pen                            |

| 7.  | JPR3    | 0pen                            |

| 8.  | JPR4    | Jumper                          |

| 9.  | JPR5    | 0pen                            |

| 10. | JPR6    | 0pen                            |

| 11. | JPR7    | Jumper                          |

| 12. | JPR8-11 | Select appropiate drive address |

| 13. | JPR 12  | Jumper                          |

| 14. | JPR13   | 0pen                            |

| 15. | JPR 14  | 0pen                            |

| 16. | JPR15   | 0pen                            |

| 17. | JPR 16  | 0pen                            |

Install the termination network only in the last drive in the daisy chain.

Each drive requires 24 volts at 1.5A and 5 volts at 1.0A.

#### Innotronics 410/420 Disk Drive

Required drive configuration\*:

| 1. EH          | Trace intact                     |

|----------------|----------------------------------|

| 2. AH          | 0pen                             |

| 3. TH          | Trace intact                     |

| 4. NT          | 0pen                             |

| 5. TE          | Trace intact                     |

| 6. NT          | 0pen                             |

| 7. LM          | Trace intact                     |

| 8. TM          | Open .                           |

| 9. WP          | Trace intact (2 places)          |

| 10. NP         | Open (2 places)                  |

| 11. T4         | Jumper                           |

| 12. T3, T5, T7 | Jumpered on last drive in system |

| 13. SO-3       | Select appropriate drive address |

To use the Model 420 (Hard Sector) Disk Drive as a Soft Sector Disk Drive, the following link positions must be set:

| 1. IB     | Jumper                           |

|-----------|----------------------------------|

| 2. HS     | 0pen                             |

| 3. RD     | Jumper                           |

| 4. SD     | Open (2 places)                  |

| 5. VV     | Jumper to accept -5 volt supply, |

| otherwise |                                  |

|           | open to accept -7 to -12 volts.  |

Install the termination network only in the last drive in the daisy chain.

Each drive requires +5 volts at 0.8A, -5 volts at .08A, and +24 volts. The current rating for the 24 volts supply depends on whether the drives will seek individually or simultaneously. If CP/M or a similar DOS is used, the total current is 1.4A. This is because Innotronics applies power to the stepper motor only when the drive is seeking. If software is used that can simultaneously seek on all drives in the system, each individual drive will require 1.4A.

Required Pre-write Compensation: 125 ns. \*The model 410 disk drives are shipped fully compatible with the FDC-I.

#### PerSci 277 Disk Drive System

The PerSci 277 disk drive system is a system composed of two 8-inch drive units requiring a 50 pin connector to the host system used. Pin assignments to functional signals of the 50 pin connector and the changes required to interface to SYSTEMASTER are shown below.

| SM  | Signal<br>Pin No. | Ground<br>Pin No. | Signal                       |

|-----|-------------------|-------------------|------------------------------|

| 2   | 2                 | 1                 | Unassigned                   |

| 4   | 4                 | 3                 | Drive select 2 right         |

| 6   | 6                 | 3<br>5<br>7       | Ready 1                      |

| Cut | 8                 | 7                 | Index 1                      |

| Cut | 10                | 9                 | Seek complete                |

| 12  | 12                | 11                | Restore                      |

| Cut | 14                | 13                | Remote eject O               |

| 18  | 16                | 15                | Direct headload              |

| Cut | 18                | 17                | Drive select 2 left          |

| 20  | 20                | 19                | Index 0                      |

| 22  | 22                | 21                | Ready O                      |

| 50  | 24                | 23                | Spindle motor enable         |

| 26  | 26                | 25                | Drive select 1 l <b>e</b> ft |

| 28  | 28                | 27                | Drive select 1 right         |

| Cut | 30                | 29                | Write protect 1              |

| Cut | 32                | 31                | Remote eject 1               |

| 34  | 34                | 33                | Direction select             |

| 36  | 36                | 35                | Step                         |

| 38  | 38                | 37                | Write data                   |

| 40  | 40                | 39                | Write gate                   |

| 42  | 42                | 41                | Track O                      |

| 44  | 44                | 43                | Write protect O              |

| 46  | 46                | 45                | Read data                    |

| 48  | 48                | 47                | Separated data               |

| Cut | 50                | 49                | Separated clock              |

Required drive configuration:

1. Address DIP, U-11: connect pin 4 to 11, and pin 2 to

| 10  | 1. Address DIF, 0-11. | connect pin 4 to 11, and pin 2 to |

|-----|-----------------------|-----------------------------------|

| 13. | 2. A-B                | Raw read data                     |

|     | 3. D-BL               | Select gate enabled               |

|     | 4. E,F,G              | Open                              |

|     | 5. J-Z                | Enable L=O, and R=1               |

|     | 6. K-L                | Wire-OR the Write Protect signals |

|     | 7. M,N,P              | 0pen                              |

|     | 8. R,S,T              | 0pen                              |

|     | 9. U-V                | Wire-OR the Index signals         |

|     | 10. W-X               | Enable Index O                    |

|     | 11. AB-AC             | Enable Index O                    |

|     | 12. AD-AE             | Enable Index 1                    |

|     | 13. AH-AJ             | Enable Index 1                    |

|     | 14. AM-AL             | For spindle motor control         |

|     |                       |                                   |

| or           |                                 |

|--------------|---------------------------------|

| AM-AN        | Spindle motor runs continuously |

| 15. AP-AR    | Wire-OR the Ready signals       |

| 16. AS-AT    | Remote eject, connects L and R  |

|              | together                        |

| 17. AU,AV,AW | 0pen                            |

| 18. BA-BB    | Enable Index 1                  |

| 19. BD-BE    | Seek complete enable            |

| 20. BF,BH,BJ | 0pen                            |

| 21. BK-BM    | Enable Index O                  |

Each drive requires 24 volts at 1.3A, 5 volts at 2.2A, -5 volts at 0.2A and for the spindle power, 7 - 10 volts 2.0A.

Because the PerSci has two physical drives connected to one head positioner, the SYSTEMASTER software must be made to seek and recalibrate only drive 0. Otherwise the uPD-765 will seek on both drives 0 and 1, and position past the correct track. Also, if the motor control option is used, the software must have the motor control option enabled.

If fast seek is required (seek rate less than the standard 10 ms step), the seek complete line must be connected to PIO B on one of its spare lines, and a 150 ohm 1/4 watt resistor connected to +5 volts. Contact the factory for further information relating to software requirements.

#### Siemens FDD 100-8D Disk Drive

Required drive configuration:

| 1. RAD SEL 0-3 2. RAD STEP 3. "36" 4. A 5. "34" 6. B 7. RR 8. "22" 9. RI 10. C 11. "20" 12. "24" 13. L 14. J 15. K 16. "18" 17. M 18. SS 19. HS 20. S 21. U 22. R 23. H 24. "16" 25. E 26. V | Select appropriate drive address Jumper pads labelled "2" Jumper Open Jumper Open Open Open Open Open Open Open Open |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25. E                                                                                                                                                                                        | Jumper                                                                                                                                                                                                                                                                                                                  |

| 27. "12"                                                                                                                                                                                     | Upen<br>Jumper                                                                                                                                                                                                                                                                                                          |

| 28. G<br>29. H                                                                                                                                                                               | Open (cut trace)<br>Open (for Phase Option)                                                                                                                                                                                                                                                                             |

| 30. F                                                                                                                                                                                        | Jumper                                                                                                                                                                                                                                                                                                                  |

Install the terminator resistor pack in the last drive of the daisy chain.

Each drive requires 24 volts at 1.6A, and +5 volts at 1.0A.

The Siemens drives need to be modified if more than 1 drive will be in the system. On the drive p.c. board, cut the trace going to pin 9 of IC 6C. Add a jumper between pins 9 and 12 of IC 6C. This change accommodates the NEC controller.

#### Remex 2000/4000 Disk Drive

Required drive configuration:

```

1. 2S

Jumper

2. DC

0pen

3. C

Jumper

4. D

0pen

5. DS1-4

Select appropriate drive address

6. 1B, 2B, 3B, 4B

Open

7. S1, 2, 3

8. TS-FS

S2

Don't care

9. 4000/4001

4000

10. DL

Jumper

11. S

Jumper

12. R

Jumper

13. I

Jumper

14. X

Jumper

15. B

Open

16. A

Jumper

17. HL

Open

18. Z

Jumper

19. DS

0pen

20. Y

Open

21. RI

Traces intact

22. RR

Traces intact

```

The last drive in the daisy chain must have the resistor termination pack installed in location 7A.